计算机组成原理期末复习

第1章 计算机系统概论

1.2.1 冯诺依曼计算机的特点

①计算机由运算器、存储器、控制器、输入设备和输出设备组成。

②指令和数据以同等地位存放在存储器中,并可按地址寻访。

③指令和数据均用二进制数表示。

④指令由操作码和地址码组成。

⑤指令在存储器内按顺序存放。

⑥机器以运算器为中心。

1.2.3 计算机的工作过程

计算机组成:CPU、主存储器、I/O设备。

控制器:由程序计数器PC、指令寄存器IR以及控制单元CU组成。

1.3.1 机器字长

机器字长:指CPU一次能处理数据的位数,通常与CPU的寄存器位数有关。字长越长,数的表示范围越大,精度也越高。

存储容量=存储单元个数×存储字长。

第3章 系统总线

3.3总线特性及性能指标

总线是连接多个部件的信息传输线,是各部件共享的传输介质。

按系统总线传输信息的不同,可分为:数据总线、地址总线、控制总线。

总线带宽:工作频率×(总线宽度÷8),单位为MBps。

3.5 总线控制

常见的集中控制优先权仲裁方式有以下三种:

(1) 链式查询;(2)计数器定时查询;

(2) 独立请求方式:总线控制部件中有一排队电路,可根据优先次序确定响应哪一台设备的请求。

例3.1 假设总线的时钟频率为100MHz,总线的传输周期为4个时钟周期,总线的宽度为32位,试求出总线的数据传输率。若想提高一倍数据传输率,可采取什么措施?

解:

根据总线时钟频率位100MHz,得

1个时钟周期为1/100MHz=0.01μs

总线传输周期为0.01μs×4=0.04μs

由于总线的宽度为32位=4B(字节)

故总线的数据传输率为4B/(0.04μs)=100MBps。

若想要提高一倍数据传输率,可以在不改变总线时钟频率的前提下,将数据线的宽度改为64位,也可以仍保持数据宽度为32位,但使总线的时钟频率增加到200MHz。

例3.2 在异步串行传输系统中,假设每秒传输120个数据帧,其字符格式规定包含1个起始位、7个数据位、1个奇校验位、1个终止位,试计算波特率。

解:

根据题目给出的字符格式,一帧包含1+7+1+1=10位。

故波特率位(1+7+1+1)×120=1200bps=1200波特。

例3.4 在异步串行传输系统中,若字符格式为:1位起始位、8位数据位、1位奇校验位、1位终止位。假设波特率为1200bps,求这时的比特率。

解:

根据题目给出的字符格式,有效数据位为8位,而传送一个字符需1+8+1+1=11位,故比特率为:1200×(8/11)=872.72bps 。

第4章 存储器

4.1存储器的层次结构

缓存-主存层次主要解决CPU和主存速度不匹配问题。

主存-辅存层次主要解决存储系统的容量问题。

4.2 主存储器

1.主存中存储单元地址的分配

不同的机器存储字长不同,为了满足字符处理的需要,常用8位二进制表示一个字节,因此存储字长都取8的倍数。通常计算机系统既可按字寻址,也可按字节寻址。

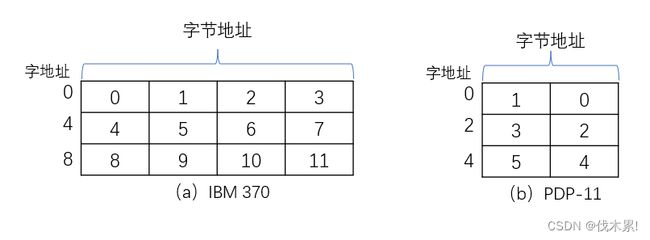

例如IBM370机的字节为32位,它可按字节寻址,即它的每一个存储字包含4个可独立寻址的字节,其地址分配如图4.6(a)所示。字地址是用该字高位字节的地址来表示,故其字地址是4个整数倍,正好用地址码的末两位来区分同一字的4个字节的位置。但对于PDP-11机而言,其字长为11位,字地址是2的整数倍,它用低位字节的地址来表示字地址,如图4.6(b)所示。

图4.6 字节寻址的主存地址分配

2.主存的技术指标

存储容量=存储单元个数×存储字长

4.2.3 随机存取存储器

(1)动态RAM的刷新

通常有三种方式刷新:集中刷新、分散刷新和异步刷新。

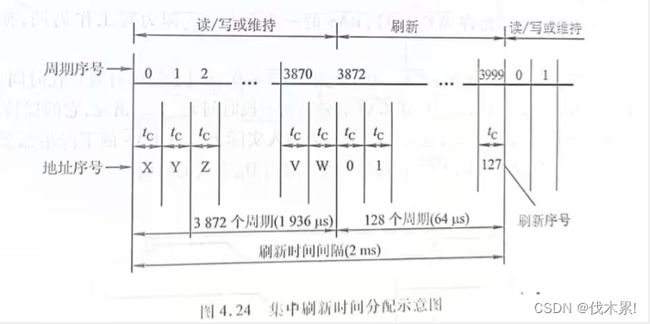

集中刷新:如图4.24所示,由于在这64μs时间内不能进行读/写操作,故称为“死时间”,又称访存“死区”,所占比率为128/4000×100%=3.2,成为死时间率。

例4.1 设CPU有16根地址线、8根数据线,并用MREQ(低电平)作为访存控制信号,用WR(低电平)作为读/写控制信号。现有下列存储芯片:1K×4位RAM、4K×8位RAM、8K×8位RAM、2K×8位ROM、4K×8位ROM、8K×8位ROM及74138译码器和各种门电路,如图4.36所示。画出CPU与存储器的连接图,要求如下:

① 主存地址空间分配:

6000H~67FFH为系统程序区。

6800H~6BFFH为用户程序区。

② 合理选用上述存储芯片,说明各选几片。

解:

第一步,先将十六进制地址范围写成二进制地址码,并确定其总容量。

可知,系统程序区为2K×8位,用户程序区为1K×8位。

第二步,选择存储芯片。

根据6000H~67FFH为系统程序区范围,应选择1片2K×8位的ROM。

根据6800H~6BFFH为用户程序区的范围,选2片1K×4位的RAM芯片正好满足1K×8位的用户程序区要求。

4.2.6 存储器的校验

1.汉明码的组成

汉明码,具有一位纠错能力。

设欲检测的二进制代码为n位,为使其具有纠错能力,需增添k位检测位,组成n+k位的代码。为了能准确对错误定位以及指出代码没错,新增添的检测位数k应满足:

2k≥n+k+1

由此关系可求得不同代码长度n所需检测位的位数k,如表4.2所示。

具体分配如下:

C1 检测的g1小组包含1,3,5,7,9,11,…位。

C2 检测的g2小组包含2,3,6,7,10,11,14,15,…位。

C4 检测的g3小组包含4,5,6,7,12,13,14,15,…位。

C8 检测的g4小组包括8,9,10,11,12,13,14,15,24,…位。

例如,欲传递信息为b4b3b2b1(n=4),根据2k≥n+k+1,可求出配置成汉明码需增添检测位k=3,且它们位置的安排如下:

如果按配偶原则来配置汉明码,则C1应使1、3、5、7位中的“1”的个数为偶数;C2应使2、3、6、7位中的“1”的个数为偶数;C4应使4、5、6、7位中的“1”的个数位偶数。

令b4b3b2b1=0101,则

C1=b4+b3+b1=0+1+1=0

C2=b4+b2+b1=0+0+1=1

C4=b3+b2+b1=1+0+1=0,故0101的汉明码应为C1C2b4C4b3b2b1,即0100101。

2.汉明码的纠错过程

汉明码的纠错过程实际上是对传送后的汉明码形成新的检测位Pi(i=1,2,4,8,…),根据Pi的状态便可直接指出错误的位置。Pi的状态是由原检测位Ci及其所在小组内“1”的个数确定的。倘若按配偶原则配置的汉明码,其传送后形成新的检测位Pi 应为0,否则说明传送有错,并且还可以直接指出出错的位置。

设已知传送的正确汉明码(按配偶原则配置)位0100101,若传送后接收到的汉明码为0100111,其出错位可按下述步骤确定。

则新的检测位为

P4=4+5+6+7,即P4=0+1+1+1=1

P2=2+3+6+7,即P2=1+0+1+1=1

P1=1+3+5+7,即P1=0+0+1+1=0

由此可见,传送结果P4和P2均不呈偶数,显然出现了差错。分析只有第6位出错才会同时使P4和P2不呈偶数,显然出现了差错,即P4P2P1=110,表示第6位出错。发现错误后,计算机便自动将错误的第6位纠正为“0“。

又如若收到按偶配置的汉明码为1100101,经检测得P4P2P1=001,表示第1位出错。由于第1位不是欲传送的信息位,而是检测位,不参与运算,故一般不予纠正。

4.3.2 Cache-主存地址映射

地址映射方式很多,有直接映射、全相联映射、组相联映射。

例4.8 假设主存容量为512KB,Cache容量为4KB,每个字块为16个字,每个字32位。

(1) Cache地址有多少位?可容纳多少块?

(2) 主存地址有多少位?可容纳多少块?

(3) 在直接映射方式下,主存的第几块映射到Cache中的第5块(设起始字块为第1块)?

(4) 画出直接映射方式下主存地址字段中各段的位数。

解:

(1) 根据Cache容量为4KB,Cache地址为12位。由于每字32位,则Cache共有4KB/4B=1K字。因每个字块16个字,故Cache中有1K/16=64块。

(2) 根据主存容量为512KB,主存地址为19位。由于每字32位,则Cache共有512KB/4B=128K字。因每个字块16个字,故主存中共128K/16=8192块。

(3) 在直接映射方式下,由于Cache共有64块,主存共有8192块,因此主存的5,64+5,2×64+5,…,213-64+5块能映射到Cache的第5块中。

(4) 在直接映射方式下,主存地址字段的各段数分配如图4.57所示。其中字块内地址为6位(4位表示16个字,2位表示每字32位),缓存共64块,故缓存字块地址为6位,主存字块记为主存地址长度与Cache地址长度之差,即19-12=7位。

图4.57 例4.8 主存地址各字段的分配

例4.9 假设主存容量为512K×16位,Cache容量为4096×16位,块长为4个16位的字,访存地址为字地址。

(1) 在直接映射方式下,设计主存的地址格式。

(2) 在全相联映射方式下,设计主存的地址格式。

(3) 在二路组相联映射方式下,设计主存的地址格式。

解:

(1) 根据Cache容量为4096=212字,得Cache字地址为12位。根据块长为4,且访存地址为字地址,得字块内地址为2位,即b=2,且Cache共有4096/4=1024=210块,即c=10。根据主存容量为512K=219字,得主存字地址为19位。在直接映射方式下,主存字块标记为19-12=7。

(2) 在全相联映射方式下,主存字块标记为19-b=19-2=17位。

(3) 根据二路组相联的条件,一组内有2块,得Cache共分1024/2=512=2q组,即q=9,主存字块标记为19-q-b=19-9-2=8位。

例4.10 假设Cache的工作速度是主存的5倍,且Cache被访问命中的概率为95%,则采用Cache后,存储器性能提高多少?

解:

设Cache的存取周期为t,主存的存取周期为5t,则系统的平均访问时间为

ta=0.95×t+0.05×5t=1.2t

性能为原来的5t/1.2t=4.17倍,即提高了3.17倍。

第5章 输入输出系统

5.1.4 I/O设备与主机信息传送的控制方式

I/O设备与主机交换信息时,共有5中控制方式:程序查询方式、程序中断方式、直接存储器存取方式(DMA方式)、I/O通道方式、I/O处理机方式。

5.3.2 接口的功能和组成

接口的功能:(1)选址功能;(2)传送命令功能;(3)传送数据功能;(4)反映I/O设备工作状态的功能。

5.4.2 程序查询方式的接口电路

例5.1 在程序查询方式的输入输出系统中,假设不考虑处理时间,每一次查询操作需要100个时钟周期,CPU的时钟频率为50MHz。现有鼠标和硬盘两个设备,而且CPU必须每秒对鼠标进行30次查询,硬盘以32位字长为单位传输数据,即每32位被CPU查询一次,传输率为2MBps。求CPU对这两个设备所花费的时间比率,由此可得出什么结论?

解:

(1)CPU每秒对鼠标进行30次查询,所需的时钟周期为100×30=3000

根据CPU的时钟频率为50MHz,即每秒50×106个时钟周期,故对鼠标的查询占用CPU的时间比率为

[300/(50×106)]×100%=0.006%

可见,对鼠标的查询基本不影响CPU的性能。

(2)对于硬盘,每32位被CPU查询一次,故每秒查询2MB/4B=512K次

则每秒查询的时钟周期数为 100×512×1024=52.4×106

故对磁盘的查询占用CPU的时间比率为 [(52.4×106)/(50×106)]×100%=105%

可见,即使CPU将全部时间都用于对硬盘的查询也不能满足磁盘传输的要求,因此CPU一般不采用程序查询方式与磁盘交换信息。

5.5.3 程序中断方式的接口电路

中断向量地址形成部件的输入是来自排队器的输出INTP1,INTP2,…,INTPn,它的输出是中断向量(二进制代码表示),其位数与计算机可以处理中断源的个数有关,即一个中断源对应一个向量地址。

5.5.5 中断服务程序的流程

一般中断服务程序的流程分为四大部分:保护现场、中断服务、恢复现场和中断返回。

中断返回:如果CPU暂停现行的中断服务程序,转去处理新的中断请求,这种现象称为中断嵌套,或多重中断。

5.6 DMA方式

通常DMA与主存交换数据时采用如下三种方法:

(1) 停止CPU访问主存;(2)周期挪用(或周期窃取);(3)DMA与CPU交替访问。

第6章 计算机的运算方法

6.3.2 定点的加减法运算

1.补码加减运算的基本公式

补码加法的基本公式如下:

整数 [ A ]补+[ B ]补=[ A+B ]补(mod 2n+1)

小数 [ A ]补+[ B ]补=[ A+B ]补(mod 2)

对于减法,因A-B=A+(-B),则[A-B]补=[A+(-B)]补

由补码加法基本公式可得

[ A - B ]补=[ A ]补+[-B]补(mod 2n+1) (其中n是小数点后二进制的位数)

[ A - B ]补=[ A ]补+[-B]补(mod 2)

因此,若机器数采用补码,当求A-B时,只需先求[-B]补,就可按补码加法规则进行运算。而[-B]补由[B]补连同符号位在内,每位取反,末位加1而得。

例6.8 已知A=0.1011,B=-0.0101,求[A+B]补。

解:

因为A=0.1011,B=-0.0101,

所以[A]补=0.1011,[B]补=1.1011

则 [A]补+[B]补= 0.1011

+ 1.1011

0.0110=[A+B]补

按模2的意义,最左边的1丢掉,故[A+B]补=0.0110,结果正确。

例6.9 已知A=-1001,B=-0101,求[A+B]补。

解:

因为 A=-1001,B=-0101

所以 [A]补=1,0111,[B]补=1,1011

则,[A]补+[B]补= 1,0111

+ 1,1011

1,0010 = [A+B]补

按模24+1的意义,最左边的1丢掉。

6.4 浮点的加减法运算

1.对阶

对阶的目的是使两操作数的小数点位置对齐,即使两数的阶码相等。为此,首先要求出阶差,再按小阶向大阶看齐的原则,使阶小的尾数向右移位,每右移一位,阶码加1,直到两数的阶码相等为止。右移的次数正好等于阶差。尾数右移时可能会发生数码丢失,影响精度。

例如,两浮点数x=0.1101×201,y=(-0.1010)×211,求x+y。

首先写出x,y在计算机中的补码表示。

[x]补=00,01; 00.1101, [y]补=00,11; 11.0110

在进行加法前,必须先对阶,故先求阶差:

[△j]补=[jx]补-[jy]补=00,01 + 11,01 =11,10

即△j=-2,表示x的阶码比y的阶码小,再按小阶向大阶看齐的原则,将x的尾数右移两位,其阶码加2,得

[x]’补=00,11; 00.0011

此时,△j=0,表示对阶完毕。

2.尾数求和

将对阶后的两个尾数按定点加(减)运算规则进行运算。

如上例中的两数对阶后得

[x]’补=00,11; 00.0011

[y]补 =00,11; 11.0110

则[Sx+Sy]补为

00.0011 [Sx]’补

+ 11.0110 [Sy]补

11.1001 [Sx+Sy]’补

即 [x+y]补=00,11; 11.1001

第7章 指令系统

7.1 机器指令

例7.1 假设指令字长为16位,操作数的地址码为6位,指令有零地址、一地址、二地址三种格式。

(1) 设操作码固定,若零地址指令有P种,一地址指令有Q种,则二地址指令最多有几种?

(2) 采用扩展操作码技术,若二地址指令有X种,零地址指令有Y种,则一地址指令最多有几种?

解:

(1) 根据操作数地址码为6位,则二地址指令种操作码的位数为16-6-6=4。这4位操作码有24=16种操作。由于操作码固定,则除去了零地址指令P种,一地址指令Q种,剩下二地址指令最多有16-P-Q种。

(2) 采用扩展操作码技术,操作码位数可变,则二地址、一地址和零地址的操作码长度分别为4位、10位和16位。可见二地址指令操作码每减少一种,就可多构成26种一地址指令操作码;一地址指令操作码每减少一种,就可多构成26种零地址指令操作码。

因二地址指令有X种,则一地址指令最多有(24-X)×26种。设一地址指令有M种,则零地址最多有[(24-X)×26-M]×26种。

根据题中给出零地址指令有Y种,即

Y=[(24-X) ×26-M]×26

则一地址指令

M=(24-X) ×26-Y×2-6

7.3 寻址方式

寻址方式分为指令寻址和数据寻址两大类。

指令寻址分为顺序寻址和跳跃寻址两种。

数据寻址分为立即寻址、直接寻址、隐含寻址、间接寻址、寄存器寻址、寄存器间接寻址、基址寻址、变址寻址、相对寻址

例7.2 设相对寻址的转移指令占3个字节,第一字节为操作码,第二、三字节为相对位移量(补码表示),而且数据在存储器中采用以低字节地址为字地址的存放方式。每当CPU从存储器取出一个字节时,即自动完成 (PC)+1→PC。

(1) 若PC当前值为240(十进制),要求转移到290(十进制),则转移指令的第二、三字节的机器代码是什么?

(2) 若PC当前值为240(十进制),要求转移到200(十进制),则转移指令的第二、三字节的机器代码是什么?

解:

(1) PC当前值为240,该指令取出后PC值为243,要求转移到290,即相对位移量为290-243=47,转换成补码为2FH。由于数据在存储器中采用以低字节地址为字地址的存放方式,故该转移指令的第二个字节为2FH,第三字节为00H。

(2) PC当前值为240,该指令取出后PC值为243,要求转移到200,即相对位移量为200-243=-43,转换成补码为D5H,由于数据在存储器中采用低字节地址为字地址的存放方式,故该转移指令的第二字节为D5H,第三字节为FFH。

例7.3 一条双字长直接寻址的子程序调用指令,其第一个字为操作码和寻址特征,第二个字为地址码5000H。假设PC当前值为2000H,SP的内容为0100H,栈顶内容为2746H,存储器按字节编址,而且进栈操作是先执行 (SP)-△→SP,后存入数据。试回答下列几种情况,PC、SP及栈顶内容各为多少?

(1) CALL指令被读取前。

(2) CALL指令被执行后。

(3) 子程序返回后。

解:

(1) CALL指令被读取前,PC=2000H,SP=0100H,栈顶内容为2764H。

(2) CALL指令被执行后,由于存储器按字节编址,CALL指令共占4个字节,故程序断点2004H进栈,此时SP=(SP)-2=00FEH,栈顶内容为2004H,PC被更新为子程序入口地址5000H。

(3) 子程序返回后,程序断点出栈,PC=2004H,SP被修改为0100H,栈顶内容为2764H。

第8章 CPU的结构和功能

8.3.2影响流水线性能的因素

通常由于在流水过程中会出现三种相关,使流水线不断流实现起来很困难,这三种相关是结构相关、数据相关和控制相关。