niosII处理器与串行D/A转换器接口设计

niosII处理器与串行D/A转换器接口设计

指导教师

中文摘要:本文先通过方案论证对设计采用Verilog HDL根据串行D/A的spi时序图和Avalon总线协议标准设计TLC5615的IP核,在Modelsim上面进行仿真验证,然后通过SOPC builder设计SOPC系统并且将IP加入进去,结合在niosII IDE里面编写一个三角波软件程序一起烧录在目标硬件环境中去调试通过观察示波器波形完成硬件件验证。通过设计和仿真验证以及硬件环境验证发现FPGA里面跑IP核灵活优点,大大减少软件的开销,提升整体系统的速度。通过本设计让我们领略到FPGA设计流程,对FPGA的设计有更多认识。

关键词:FPGA nios II处理器 IP核 SOPC Builder DAC

Abstract:This article first through scheme comparison of design using Verilog HDL according to the spi serial D/A sequence diagram and the Avalon bus protocol standard design TLC5615 IP core, above the Modelsim simulation validation, and then through the SOPC builder design and add the IP in the SOPC system, combining with inside the niosII IDE burn together write A triangle wave software program in the target hardware environment to debug by observing the oscilloscope waveform complete hardware validation.Through the design and simulation, and hardware environment test run found inside the FPGA IP core advantages of flexible, greatly reduce the cost of software, improve the speed of the whole system.Through this design, let’s enjoy the FPGA design flow, know more about the design of FPGA.

Key Words:The FPGA nios II processor IP core SOPC Builder DAC

目录

一、 绪论 3

1、题目背景和意义 3

二、 串行D/A接口设计方案的选择与比较 4

1、常用的D/A转换接口设计方案 4

2、本设计所使用的方案 4

三、 本设计对FPGA的目标环境选择 5

1、FPGA芯片技术原理结构 5

(1)FPGA简介 5

(2)FPGA的结构细节和运行原理机制 5

(3)主流FPGA厂商 6

(4)FPGA与CPLD的区别和关系 6

(5)FPGA特点 7

(6)FPGA发展状况和趋势 8

2、本设计采用的FPGA目标环境介绍 8

四、 本设计涉及技术背景 10

1、本设计涉及技术总述 10

2、Quartus II软件 10

(1)Quartus II软件介绍 10

3、Verilog HDL硬件描述语言及其优点 11

4、SPI接口 11

5.Avalon总线 12

(1)Avalon总线介绍 12

(2)Avalon总线的信号 13

6、Modelsim软件 13

(1)Modelsim软件介绍 14

7.SOPC及其IP 14

(1)SOPC技术 14

(2)IP核技术 14

(3)SOPC系统开发流程 15

8、NIOS II处理器及NIOS II IDE 16

(1)NIOS II处理器简介 16

(2)nios处理器特点 16

(3)NIOS II IDE 17

五、 TLC5615串行D/A转换器的IP核设计 18

1、Quartus II上面HDL文件的设计 18

(1)确定接口 18

(2)确定时序和传输寄存器原理 18

(3)设计IP核的接口 18

(4)设计IP核的时序和逻辑 19

2、Modelsim ISE上面对IP的HDL文件进行仿真 21

(1)确定仿真模型, 22

(2)编写testbench激励块HDL文件。 22

(3)建立仿真工程 23

(4)仿真结果 25

3、IP核封装 26

六、 D/A接口IP核在SOPC里面的应用 28

1、构建SOPC系统 28

2、在Quartus II里面配置管脚约束生成硬件配置信息 28

3、Nios II IDE里面三角波程序设计 29

(1)三角波原理 29

(2)建立Nios II工程 30

(3)设计结果 32

七、 结论 34

八、 结束语 35

参考文献 35

九、 附录 35

一、绪论

1、题目背景和意义

D/A转换器是嵌入式领域比较常用的一款芯片,随着芯片封装逐渐做小,系统集成度的越来越高,为简化硬件电路的设计,降低硬件的复杂度,所以当前大多数的D/A 转换器都采用了串行数据接口来对D/A转换器送数值,所以本文讨论设计串行D/A转换接口驱动的设计,再加上当前FPGA逐渐成为嵌入式的一种趋势,所以niosII处理器的串行D/A接口设计意义比较重大。首先通过比较传统驱动设计和IP核硬件驱动设计来论证用verilog HDL语言设计硬件驱动的方案优势。再通过用硬件描述语言verilog HDL设计串行D/A转换器TLC5615的接口驱动,通过Modelsim仿真验证之后由SOPC builder封装成IP核添加到SOPC工程形成SOPC系统,再通过nios IDE链接SOPC系统文件建立工程,编写三角波的C语言源程序,编译之后将SOPC系统和Nios II软件源程序一起烧写到硬件目标板调试验证IP核的逻辑功能正确性和用硬件描述语言verilog HDL编写串行D/A接口IP核的优越特性。

二、

串行D/A接口设计方案的选择与比较

1、常用的D/A转换接口设计方案

方案一:单片机与TLC5615,原理:基于单片机写C程序软件驱动TLC5615,用C语言写软件运行在单片机上。首先速度上,单片机的速度一般只有几十兆,并且单片机的指令是串行执行的,如果用单片机做TLC5615的驱动接口肯定大大消耗单片机CPU资源,不利于其他程序的开发,成本上,单片机价格较低,软件速度上比较慢。

方案二:FPGA和TLC5615,原理:用Verilog HDL语言写TLC5615的驱动并封装成IP核,在SOPC builder上构建NIOS II处理器加入TLC5615的IP构成硬件软核系统,然后基于nios II处理器做软件开发。速度上,FPGA速度都比较快,再加上FPGA的内部集成有锁相环,可以轻松把速度提升几倍到几十倍,例如Altera公司的Cylone IV代的芯片可以倍频26倍,外部晶振一般接50M,最高可以达到1.3G,再加上FPGA的指令是并行执行,执行效率高,所以速度上完全够用,成本上一块Cylone 系列的芯片大概几十块钱,比单片机稍贵,软件速度上比较快。

方案三:CPLD和TLC5615,原理:用Verilog HDL语言基于CPLD做TLC5615接口驱动的开发,然后用Verilog HDL 做基于CPLD其他外设资源的开发,不做软件,全部硬件描述设计。速度上可以和FPGA媲美,并且也是并行执行的指令,速度上满足要求,成本上,一块CPLD芯片介于单片机与FPGA之间,不过CPLD内部资源有限,一般适合做速度快复杂度简单的器件,不适合复杂的系统开发。

方案四:单片机加CPLD和TLC5615,原理:用verilog HDL语言基于CPLD开发TLC5615接口,用C语言基于单片机开发软件构成CPLD与单片机的系统。此方案解决了上一方案CPLD 的不足,同时又继承了CPLD速度上的优势,但是成本上与方案二相当,软件执行速度上低于方案二。

2、本设计所使用的方案

综合上面几个方案,方案二速度上软件和接口的速度都比较快,价格上适中,所以我们最终选择方案二做为TLC5615的接口设计,综合成本和系统复杂度考虑,选择Altera公司的Cylone系列第二代的EP2C5T144C8的FPGA芯片,由于学校资源和制作成本上的原因,所以直接使用现成的FPGA开发板作为硬件平台。

三、

本设计对FPGA的目标环境选择

1、FPGA芯片技术原理结构

(1)FPGA简介

FPGA英文全称Field-Programmable Gate Array,即英文翻译名称现场可编程逻辑门阵列,是从PAL、GAL、CPLD等一系列可编程器件的之后产生的新一种可编程器件,所以复杂度要强与传统可编程器件,性能优于传统可编程器件,也是定制集成电路的一种半定制电路器件。

(2)FPGA的结构细节和运行原理机制

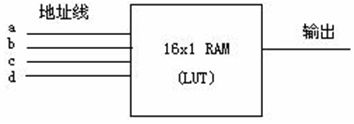

大部分FPGA是基于SRAM技术,组成可编程逻辑器件最基本的逻辑单元是LUT中文名查找表如图3-1-1-1(四输入的查找表),

图3-1-1-1四输入的查找表

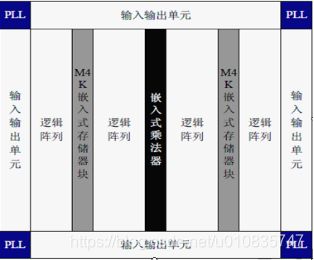

一个由n个输入的查找表可以实现n个输入的任何逻辑,例如上面的四输入查找表,可以实现四输入量间的任何逻辑运算,例如四输入“与”,“或“等等,以Altera公司的Cylone II飓风2代为例,它的组成有:嵌入式阵列块(EAB)、逻辑阵列块(LAB)、快速通道(FAST TACK)互联、IO单元(IOE)、以及一个实现储存功能和专用功能的逻辑阵列块和一个一般的逻辑阵列块,其结构如图3-1-1-1

图3-1-1-2 FPGA内部结构

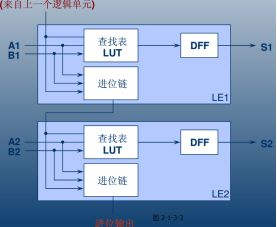

FPGA里面最小的逻辑单元叫LE,LE又是由组合逻辑电路和时序逻辑电路组成,构成有:

一个LUT查找表,作用:函数发生器

一个可编程且有同步使能的触发器,作用:组成时序电路

一个进位链,作用:提供进位的连接,还可以连接LAB中所有LE,以及同一行中所有LE

一个级联链,作用:连接相邻的LE

例如快速加法器如图3-1-1-3

图3-1-1-3快速加法器

(3)主流FPGA厂商

说到FPGA当然要提到目前主流的两家FPGA芯片厂商,一个是美国的Altera公司,生产的FPGA大体上分为:

EPS系列,即Stratix,普通高端系列,速度和性能高,应该在高端产品里面

EPA系列,即Arria,普通中端系列,速度和性能适中,应用在中低端产品

EP*C系列,即Cyclone,普通低端系列,价格低廉,比如一块Cyclone II芯片只要35美分,但是资源上完全满足一个稍微复杂的片上系统。

以及每一系列的第五代产品系列,5x系列,第五代产品有标志性的技术突破采用28nm技术,有更优越的性能,所以单独分为一个系列。开发工具是Quartus

另一个是Xilink公司,生产的FPGA主要分为两大类

Spartan系列,低成本的,它的容量和性能可以满足一般逻辑设计要求,应用在中低端产品

Virtex系列,高性能,容量大,应用在比较高端的产品中,比如航空航天等

开发工具是ISE

(4)FPGA与CPLD的区别和关系

FPGA是现场可编程逻辑门阵列,CPLD是复杂可编程逻辑门阵列,它们都同属于可编程器件,而且编程方法都可以用硬件描述语言来设计电路。虽然它们同属于可编程阵列,但是有有着各自的特点

它们的结构组成由所不同,FPGA的最小逻辑单元是LE,FPGA内部的IO单元是分布与四周,再加上内部规模的庞大,所以FPGA的时间参数难以预测。CPLD的最小逻辑单元是可编程逻辑宏单元LMC,LMC有较复杂的IO单元结构,用户可以很灵活的配置成相应特定的结构系统,从而可以预见电路的时间参数,如门延迟等等除此之外CPLD一般也会比FPGA速度更快。

它们的逻辑单元集成程度不一样,CPLD的集成逻辑单元从几千到几万,而FPGA的集成的逻辑单元是几万到几百万,这点上FPGA明显优于CPLD,FPGA也就更适合做超大规模的集成系统,而CPLD也就适合做逻辑不是太复杂,规模较中小型的集成系统。

程序存储不一样,FPGA大多采用的SRAM技术,掉电丢失数据,所以FPGA的程序都是放在外部的数据存储器ROM里面,虽然需要外加flash作为存储,但这也增加了FPGA的灵活性,而且芯片内部的擦除次数在芯片没损坏的情况下可以是无限次。外部存储当然也会有一定风险,程序也就容易被人窃取。而CPLD采用的是fastflash或者e2prom技术,数据信息都是直接存放在芯片内部无需外加存储芯片,这样的优点就是不用担心程序信息被窃取,但是因为这个原因,CPLD的数据擦除次数也是有限的,不过一般可以达到数万次。

他们的功耗不同,因为结构的原因,CPLD一般都会比FPGA的能耗要高一些。

基于以上区别,和本设计的编程规模,所以选择采用FPGA作为本设计的硬件芯片。

(5)FPGA特点

FPGA运行速度快,FPGA内部集成有锁相环,比如Altera CYCLONE IV代芯片,价格低廉,一块50块左右,50M晶振速度可以倍频26倍达到到1.3G,而同等价格的单片机或者ARM芯片都达不到如此高的速度。

FPGA管脚多和触发器,FPGA器件一般都是数百的管脚,这易于内部资源分配到管脚和外部资源连接,如果是单片机或者ARM芯片因为管脚和功能管脚在特定管脚上,都要仔细分配。

FPGA是并行运行的、效率高,单片机或者ARM芯片是串行运行,指令是逐条执行的,突发事件需要用到有限的中断,还得仔细分配中断优先级,而FPGA所有的逻辑是并行运行的,无需担心并行事件,更容易处理突发事件指令,处理效率更高。

FPGA采用的高速CMOS工艺,功耗低,节约能源,除此之外可以与COMS和TLL电平完全兼容。

开发周期短,FPGA生产厂商提供了嵌入式处理器解决方案,以及很多免费的IP核供开发人员使用,开发人员可以利用FPGA厂商提供的IP开发,大大缩减了开发周期。

灵活性高,FPGA的程序是存储在EPROM里面,工作时由EPROM里面读出读入片内RAM里面,而RAM掉电后数据会丢失成空白片,所以只需要改变EPROM就可以改变FPGA的程序,不需要专用的编程器,还可以利用这个让同一个FPGA复用两套或者多套程序。

(6)FPGA发展状况和趋势

FPGA:是从20世纪70年代开始萌芽,当时出现了可以反复烧写程序的紫外线可擦除只读存储元件EPROM和电擦除制度存储元件EEPROM,后来逐渐出现较复杂的课编程器件PAL和GAL,到20世纪90年代末的时候,出现了现在主流的两家FPGA公司,Altera和Xilink,它们推出自己的第一款CPLD产品,从那以后,Altera公司和Xilink公司占据了FPGA主导厂商,到现在这个两家公司已经生产了规模大、速度快、效率高的FPGA,足以胜任以前的SOC系统所有逻辑,占据各着个行业,特别是通信、数字信号处理、图像处理方面有着重要的地位。随着FPGA成本价格的逐渐降低,性能不断的升高,肯定会成为未来嵌入式的发展趋势。

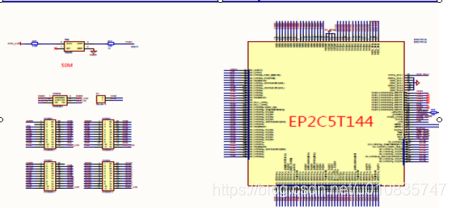

2、本设计采用的FPGA目标环境介绍

根据上面FPGA原理结构的介绍,本设计采用的网购的大西瓜开发板,采用Altera公司的飓风系列二代芯片EP2C5T144C8N芯片,1M外部Flash芯片,外接50M晶振,一个TLC5615串行dac芯片,图3-1-2-1开发板图片,如图3-1-2-2最小系统电路图

图3-1-2-1开发板图片

图3-1-2-2最小系统电路图

Altera公司的Cyclone飓风系列芯片,采用的SRAM技术,芯片尺寸已经非常小,采用的300毫米的晶元,并且采用先进的90nm工艺技术,使片上集成度更高,集成了更多的逻辑单元,飓风二代芯片一般有4608到68416个可编程逻辑单元,并且飓风二代芯片继承了第一代芯片的优秀性能,有一系列的优越功能,例如嵌入式乘法器、专用外部存储器接口电路、4kbit嵌入式存储器块、锁相环(PLL)和高速差分I/O能力。正因为飓风系列优越的性能和低廉的价格,一块飓风二代芯片只要35美分,使其有较高的影响力。altera芯片型号解析,EP2C5T1448N:“2”代表代数,第二代;“5”:逻辑单元数量有4608个;“T”:它的封装类型;“144”:有144个管脚;“8”:代表它的速度等级为8,数字越小速度越快,8是最慢的。

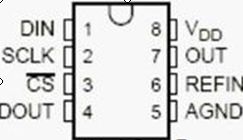

TLC5615 是美国德州公司1999出的一个10位SPI串行模数转换芯片,只要3个引脚就可以串行数据的传送,并且只需要一个5v供电,最大可以输出2倍的基准电压,能耗比较低,最多只消耗1.75mw,它的转换速度非常快,转换频率1.21MHz,最大传入数据频率14M,芯片一共有8个管脚:

DIN: 串行数据输入端; SCLK: 外部时钟信号输入端; /CS: 芯片选用通端,低电平有效; DOUT: 用于级联时的串行数据输出端; AGND: 模拟地; REFIN:基准电压输入端, 2V~ (VDD - 2),通常取2.048V; OUT: DAC 模拟电压输出端;

VDD: 正电源端,4.5~5.5V ,通常取 5V。

图3-1-2-4 TLC5615电路图,图3-1-2-5 TLC5615管脚图

图3-1-2-4 TLC5615电路图

图3-1-2-5 TLC5615管脚图

四、本设计涉及技术背景

1、本设计涉及技术总述

本设计是在quartu II 开发工具上利用verilog HDL硬件描述语言基于Avalon总线协议写TLC5615串行D/A转换器的spi接口文件,然后在Modelsim仿真工具上面用Verilog HDL硬件描述语言编写测试激励块testbench,并建立仿真工程仿真之前的IP核HDL文件。待仿真验证通过后使用qutarus II上面的SOPC builder对IP的HDL文件进行封装,然后在SOPC builder上面建立SOPC系统,添加封装好的IP核到系统中,然后在Quartus II上面做顶层模块的设计,管脚约束,编译生成sof文件,通过nios II IDE编写三角波的软件程序编译与生成sof文件一起下载到目标环境中去调试验证即是做的一个三角波发生器完成硬件目标环境的验证,由以上的设计到的技术和软件下面将按顺序一一介绍。

2、Quartus II软件

(1)Quartus II软件介绍

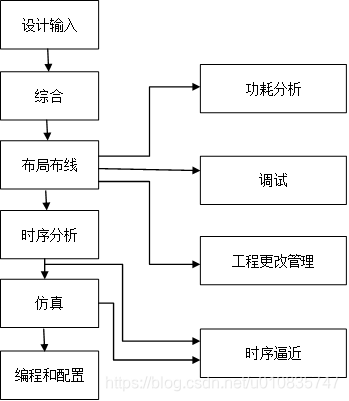

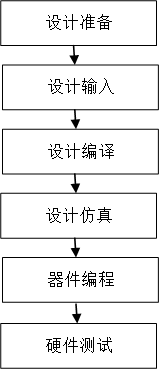

Quartus II:硬件编程工具,Quartus II是Altera公司为FPGA设计而开发的一个软件工具,这个软件工具实际是众多FPGA设计工具为一体的集成EDA工具,里面有Altera公司自己出的EDA工具,如文本编辑工具、内存编辑工具、、IP核生成工具、原理图编辑工具、内嵌综合工具、约束编辑工具等,除此外还有第三方的EDA工具软件生成商提供的EDA工具,如Synplify/Synplify Pro综合工具、Amplify综合工具、Mentor Precision综合工具等等,不过第三方软件商提供的EDA工具需要另外付费才能使用。正是由于有如此多的软件工具集成在一起,所以Quartus II功能非常完善,所以开发者可以直接在上从设计输入到硬核设计完成,除此外,Quartus II还继承了Altera公司早期开发逻辑可编程器件PLD软件工具Maxplus II的性能,如界面非常友好,使用方法非常简洁使开发设计变得更容易。所以这个软件越来越受到业界设计者的欢迎。本设计中采用Quartus II这个软件完成所有的硬件描述设计。Quartus II设计流程如图4-2-1-1

图4-2-1-1

3、Verilog HDL硬件描述语言及其优点

verilog HDL和VHDL是目前FPGA设计最流行的两种硬件描述语言,verilog HDL是,verilog HDL是起源一个公司,VHDL起源美国军方,相比之下Verilog HDL更加灵活,并且由于verilog HDL很相似,所以学习掌握起来会更加容易。正是基于此,本设计采用了verilog HDL语言编写了TLC5615的spi接口的HDL文件。

4、SPI接口

spi是一种串行外设接口,是一种同步全双工串行通信协议,硬件连接用4根线就可以高速传输,有主设备和从设备之分,所以spi有主设备模式和从设备模式。两种模式对应的是硬件的的接口有所不同。当作为主设备时,数据接口信号分别是:

主设备串行数据输入MISO、主设备串行数据输出MOSI、时钟信号口SCK、片选/使能信号口SS;当作为从设备时,数据接口信号分别是:从设备串行数据输出MISO、从设备串行数据输入MOSI、时钟信号口SCK、片选/使能信号口SS

通信原理:主设备发出时钟信号,当从设备检测到由主设备发出的时钟信号后数据开始移位发送或者接收,可以同步传送一帧数据位1到16位即一个字节,以8位为例,加上起始位和停止位以及校验位一共11位有效位。

一共有四种工作模式

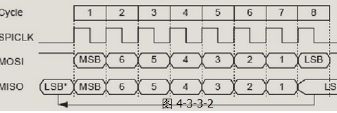

模式一:时钟信号初始状态为低电平,第一位数据在时钟初始化阶段就开始传送,保持一个时钟周期,最后一位数据传送完以后时钟复位到低电平,如图4-4-1-1

图4-4-1-1 spi模式一时序图

模式二:时钟初始状态为低电平,第一位数据在第一个时钟周期的上升沿开始传送,到最后一位数据传送完成以后,时钟复位到低电平。如图4-4-1-2

图4-4-1-2 spi模式二时序图

模式三:时钟初始状态为高电平,第一位数据在第一个时钟周期的下降沿开始传送,传送完成最后一位后时钟回到高电平状态,如图4-4-1-3

图4-4-1-3 spi模式三时序图

模式四:时钟初始状态为高电平,第一位数据在时钟初始化阶段就开始传送,保持一个时钟周期,传送完成最后一位后时钟回到高电平状态,如图4-4-1-4

图4-4-1-4 spi模式四时序图

根据TLC5615的接口寄存器,使用的是16位数据spi传输。

5.Avalon总线

(1)Avalon总线介绍

Avalon:是一种总线规范,是为SOPC系统外设开发而设计的。它是nios cpu与外设的一种通信总线接口规范标准,例如片上资源rom、ram或者片外资源pio、串口等等,系统会根据Avalon接口自动为这些资源分配基地址和偏移量

Avalon总线的特点

接口协议简单,除了片选信号接口是必须的信号外,其他信号接口可以根据需要用户自己手动添加,

速度非常快,cpu可以通过Avalon总线每一个总线周期传送一次数据,再加上Avalon总线的位宽很宽,可以达到128位,以及所有外设接口和总线的时钟接口是同步的,形成了同步传输,Avalon总线的传输速度比较快。

免费开源,用户不需要支付任何费用直接就可以使用这个接口协议。

(2)Avalon总线的信号

Avalon总线的信号分为主设备信号和从设备信号,由于此设计用到的是从设备的信号,主设备信号是cpu提供,所以这里重点介绍从设备Avalon信号,从设备信号类型此设计只用到了基本信号,所以这里主要列举从设备Avalon基本信号,有以下信号

时钟信号clk,位宽1位,输入方向,提供Avalon总线的同步接收时钟,同步传输数据的时候用,

片选信号chipselect,位宽1位,输入方向,方便cpu控制相应的从设备,无效时,忽略主设备对其数据和指令的传输

地址信号adress,位宽1到32位,输入方向,当从设备有多个寄存器共用一个接口作为外部数据传输时,需要用地址信号选通相应寄存器。

读使能信号read,位宽1位,输入方向,当主设备要向从设备读取数据时需要先使能,再传输数据,

读数据信号readdata,位宽1到128位,输出方向,负责读取数据的接口

写使能信号write,位宽1位,输入方向,当需要主设备向从设备传输数据时,必须先打开写使能,然后才能传输

写数据信号witedata,位宽1位,输入方向,主设备向从设备传输的数据口,但是必须要有写使能信号才可以。

字节使能信号byteenable,位宽0、2、4、6、8、16,输入方向,控制Avalon总线传输数据的位数,必须是以字节位单位的位数。

writebyteenable,位宽0、2、4、6、8、16,输入方向,作用就是字节信号和写使能信号同时打开,

begintransfer,位宽1位,输入方向,每次传送数据的第一次总线周期起作用,由自定义其功能。

6、Modelsim软件

(1)Modelsim软件介绍

Modelsim:是业界公认最好的HDL仿真工具,原因如下,它的仿真支持目前两种的HDL语言Verilog和VHDL,而且也是唯一一个单内核支持两种HDL的仿真工具,其次他的界面非常友好,受到业界的追捧,再则在上面编译的代码不与平台链接,也就是在任何开发工具上面写的HDL文件都可以到这个软件上面去仿真,最后,它是业界仿真最快的仿真工具,所以被公认是最好的HDL仿真软件。

7.SOPC及其IP

(1)SOPC技术

SOPC是即SOC技术之后出现的一种技术,SOC(System On Chip)技术:将大规模的数字逻辑和嵌入式处理器集成在单个芯片的,整合模拟电路和数字电路,以及软件硬件一体在片上的嵌入式系统。SOPC技术(System On programmable Chip):片上可编程系统,提出背景是美国Altera公司解决SOC在超大规模专用集成电路上的额开发周期长、团队要求高的难点而提出的有效的解决方案,用大规模可编程器件FPGA实现SOC的功能。

SOPC技术的实现方式分为3种:

基于FPGA嵌入IP(Intellectual Property)硬核的SOPC系统。例如Altera 公司的一些FPGA就嵌入了ARM嵌入式处理器,Xilink公司的FPGA则嵌入了Power pc嵌入式处理器完美的整合了ARM处理器软件功能与FPGA硬件功能的优点,

基于FPGA嵌入IP软核的SOPC系统,例如:Altera公司官方提供了Nios处理器的软核解决方案给用户,解决固核资源固定结构、功能不能改变的难点,增加设计的灵活性,以及减少资源的浪费。

基于HardCopy技术的SOPC系统,HardCopy是指将完成FPGA设计以及验证的设计用特定技术转向硬核固化其中的功能和资源。

(2)IP核技术

IP软核:由硬件描述语言设计,并且在仿真工具上完成过逻辑仿真验证,但是没有任何物理硬件设计信息,需要用户自自己完成后续的设计工作,灵活性较高。

IP硬核:除了在仿真工具完成逻辑仿真验证过以外而且已经含有硬件物理结构,经过,拓扑网表设计验证过,不可以再修改封装好了交给用户的半成品,还具有一定灵活性。

IP固核:所有的设计都已经完成,不能再做修改的已经验证过所有的功能,完全封装好了交给用户的产品。

(3)SOPC系统开发流程

SOPC的设计流程主要包括:设计输入、功能仿真、综合优化、布局布线、时序仿真、下载调试,当哪步有问题都会设计修改

设计输入:常用的设计方式有三种:硬件描述语言(HDL)、状态图、原理图三种方式,主要使用Quartus II作为设计软件,完成的工作主要是设计总体方案和报告,需要很细节的报告,一般都要细化到第三级模块的描述,报告完成有用HDL语言将其描述出来,在软件上编译检查语法错误。

功能仿真:这个阶段主要的任务是验证设计输入阶段代码的逻辑正确性,主要使用的软件是仿真软件,如Modelsim、Synplify等等,主要完成任务是是设计testbech激励快文件,然后编译连接在仿真工具上面观察波形完成对设计输入阶段代码的逻辑进行验证,当不满足预期的设计要求返回修改。

综合优化:这个阶段主要任务是对前面设计的一种优化,前面的步骤设计的东西主要针对的是功能和逻辑的正确性,而没有考虑到片上资源的利用情况以及时间的延迟等等,所以这个阶段就是要优化设计的占用资源,提高芯片资源的利用率,减少资源的浪费,还有就是对降低后期的生产成本,除此之外对结构设计和布线的优化,从而减少系统的能耗,对设计延迟的评估改进从而提高系统的速度。此阶段完成后生产门级网表文件。

布局布线:这个阶段任务主要是对设计适配、约束和工程设置,之前设计的文件只是单独的文件,需要通过将之前的工程逻辑与当前的芯片资源一一对应,并且依据约束条件选择最佳方案对应。

时序仿真:因为之前的仿真只对逻辑功能做的分析,而时间硬件和逻辑仿真理想结果会有一定差异,因为硬件电路会有一些延迟如门级延迟等,所以这个阶段需要加入时序参数约束再做一次时序仿真,验证时序是否是我预期的一致,当不满足预期的设计要求返回修改。

下载调试:前面设计已经对逻辑和时序验证,但都是仿真,所以这个阶段是要把设计的软件和硬件一起烧录到硬件目标板里面调试,看是否是所预期的结果,当不满足预期的设计要求返回修改。

SOPC设计流程如图4-4-7-1

8、NIOS II处理器及NIOS II IDE

(1)NIOS II处理器简介

NIOS II处理是由Altera公司推出的第二代嵌入式处理器软核,采用的是哈佛结构,具有32位指令集,具有3中规格可选,经济模式,标准模式,快速模式。用户可以自己制定rom和ram的大小和种类,内资源又用户自己配置,除此之外,Altera公司提供了处理器的函数接口方案,方便用户开发,用户也可以自己定制自己的函数。

(2)nios处理器特点

灵活性好,用户可以根据自己需要自己需要自己配置资源的大小多少以及自己需要的外设资源,比如ram、rom可以用片内的,也可以配置成片外的,可以配置10个管脚,可以配上几十个管脚,可以只是一个cpu以及所需rom和ram,也可以配置定时器,pio等等。

兼容性好,用户可以根据需要移植操作系统,nios II处理器是32位的,支持32位和16位的复杂指令集和精简指令集

开发容易,周期短,Altera公司官方提供了nios’处理器的资源函数,用户只需查阅一下官方的pdf文档便可以很容易的在上面做软件开发,除此之外,Altera公司官方也提供了各个寄存器地址,用户也可以根据自己需要自己写nios II处理器的函数。

niosII处理器内部结构图如图4-7-2-1

(3)NIOS II IDE

Nios II IDE是一个完善的软件开发工具,是Altera公司专为Nios系统开发设计的一款程序开发软件,软件是根据SOPC buildernios处理器定制工程,的所有的软件程序都可以在上面编写调试,除此之外,此软件上面集成有jtag调试器、程序下载器,很方便用户去调试程序,最特别的地方就是软件上面集成了实时操作系统RTOS——MicroC/OS-II(Micrium)和Nucleus Plus(ATI/Mentor)以太网协议栈TCP/IP大大给用户减少了操作系统移植和以太网移植的时间,操作简单,界面非常友好,进而大大缩短了嵌入式软件开发的周期。本设计采用此软件作为三角波软件程序的开发

五、TLC5615串行D/A转换器的IP核设计

1、Quartus II上面HDL文件的设计

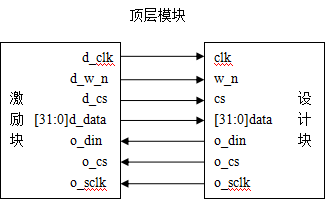

(1)确定接口

根据Avalon总线和设计需要,本设计需要向从设备传入da的数据,所以时钟信号、片选信号、写使能信号、32位写数据信号和片选信号为所需Avalon信号,其次需要输出spi时钟信号、spi片选信号、spi数据信号。

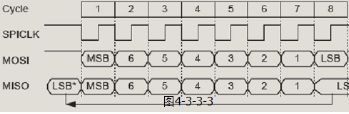

(2)确定时序和传输寄存器原理

图5-1-2-1 TLC5615 工作时序

TLC5615 工作时序如图5-1-2-1所示。可以看出,只有当片选 CS 为低电平时, 串行输入数据才能被移入 16位移位寄存器。当 CS 为低电平时, 在每一个 SCLK 时钟的上升沿将 DIN 的一位数据移入 16 位移寄存器。二进制最高有效位被导前移入。接着,CS 的上升沿将 16 位移位寄存器的 10 位有效数据锁存于 10 位 DAC 寄存器, 供 DAC 电路进行转换; 当片选 CS 为高电平时,串行输入数据不能被移入 16 位移位寄存器。CS 的上升和下降都必须发生在 SCLK 为低电平期间。

我们采用TLC5615的12位工作模式。其中10位是有效位,2位是填充位,填充位补0即可。芯片在片选/CS为低电平时工作。在每个SCLK上升沿将DIN的一位数据移入寄存器中。/CS的上升和下降都必须发生在SCLK为低电平的时候。我们可以根据需要输出的电压,设置一个10位二进制数,计算公式:Vout=VREF*(N/1024) N为10位二进制码。开发板DA芯片VDD=5V,VREF=3.3V

(3)设计IP核的接口

首先根据Avalon接口协议标准以及TLC5615芯片SPI接口定义IP核的接口,Avalon接口必须包含片选,其次要读数据,写数据,地址信号等等,但是非必需,所以我们定义

32位数据输入信号

时钟信号,外部时钟输入50M

IP核片选信号

写使能信号,低电平有效

TLC5615 SPI的时钟信号

TLC5615 SPI的片选信号

TLC5615 SPI的数据信号

如图5-1-3-1

图5-1-3-1 输入输出口定义

(4)设计IP核的时序和逻辑

根据设计要求以及TLC5615的时序图定义了以下寄存器:

分频计数寄存器1:10分频计数寄存器

数据计数寄存器2:16位数据发送计数寄存器

数据计数寄存器3:16位数据发送计数寄存器

10位数据寄存器:保存TLC5615 dac即将传送的数据

TLC5615的片选寄存器

TLC5615的时钟寄存器

TLC5615的单线输出数据寄存器

spi传送状态寄存器:1表示空闲,0表示正在发送数据

如图5-1-3-2

图5-1-3-2 寄存器定义

初始化寄存器:

打开dac的片选,单线数据寄存器置0,分频计数寄存器1、数据计数寄存器2、数据计数寄存器3清零,spi时钟置0,10位数据寄存器清零,发送状态寄存器置1 ,如图5-1-3-3

图5-1-3-3初始化寄存器

外部数据传入IP时序:

当外部传入ip的数据发生改变时执行,当片选信号为低电平且写使能信号为低电平且发送状态寄存器为1的时候外部32位数据的低10位传入10位的数据寄存器,发送状态寄存器置0;当片选信号为高电平或者写使能信号为高电平或者发送状态寄存器为0,数据寄存器不接收外部数据,进入锁存状态如图5-1-3-4

图5-1-3-4 数据传入IP时序代码

时钟分频生成spi时钟:

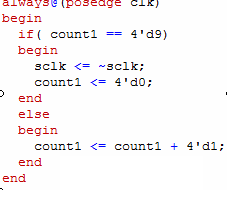

输入时钟50M经过分频计数寄存器1计数10分频得到2.5M的spi时钟信号,如图5-1-3-5

图5-1-3-5 代码时钟分频

片选控制和无效位数据计数发送

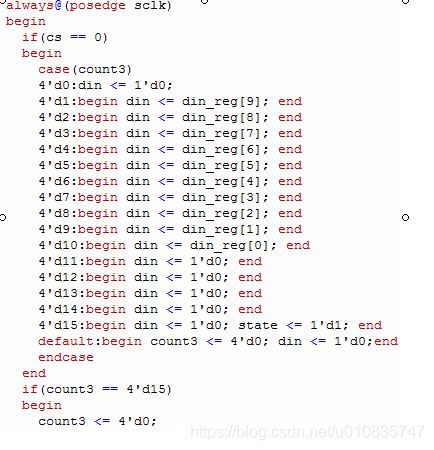

spi时钟的上升沿执行,由数据计数寄存器2累加判断传送当前位数,当发送第13位到16位片选置1即关闭片选,当发送1到12位时,片选置0,即打开片选,如图5-1-3-6

图5-1-3-6片选控制和无效位数据计数发送代码

有效位数据计数发送:

spi时钟的上升沿执行,当ip的片选寄存器为低电平时,由数据计数寄存器3累加判断传送当前位数,第1、12、13、14、16位为无效位发送0,发送最后一位完成后发送状态寄存器置1,进入空闲状态,如图5-1-3-7

图5-1-3-7 有效位数据计数发送代码

2、Modelsim ISE上面对IP的HDL文件进行仿真

(1)确定仿真模型,

由quartusII的设计文件我建立仿真模型,仿真模型如图5-2-1-1所示

图5-2-1-1 仿真模型

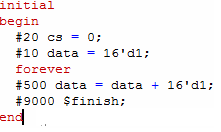

(2)编写testbench激励块HDL文件。

根据所写的IP核编写ip核的测试激励块。根据ip核接口对激励快需要定义以下寄存器和输出线变量:

时钟寄存器:产生时钟用

写使能寄存器:输入使能信号

片选寄存器:输入片选信号

32位的数据寄存器:输入数据

如图5-2-2-1

图5-2-2-1 寄存器定义代码

调用IP核设计文件块:

将时钟、外部寄存器以及线变量连接到测试块,如图5-2-2-2

![]()

图5-2-2-2 调用IP核设计文件块代码

初始化寄存器:

时钟信号置0,关闭片选信号,打开写使能,传入数据0,如图5-2-2-3

图5-2-2-3初始化寄存器代码

产生时钟信号:

由于Modelsim设置的是1ns每个时钟周期,所以这里产生的时钟信号周期是2ns,即2ns的时钟信号,如图5-2-2-4

![]()

5-2-2-4 时钟信号代码

产生仿真时序:

延时20个时钟周期打开片选,再延时10个时钟周期发送数据1,进入循环,每500个时钟周期发送的数据大小自动递增,如图5-2-2-5

图5-2-2-5 仿真时序代码

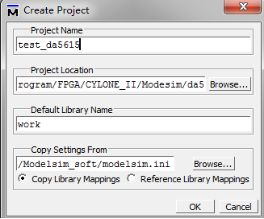

(3)建立仿真工程

打开Modelsim,新建仿真工程,如图5-2-3-1

图5-2-3-1 新建仿真工程

加入设计文件和仿真文件,如图5-2-3-1和图5-2-3-2

图5-2-3-1加入文件

图5-2-3-2加入仿真文件

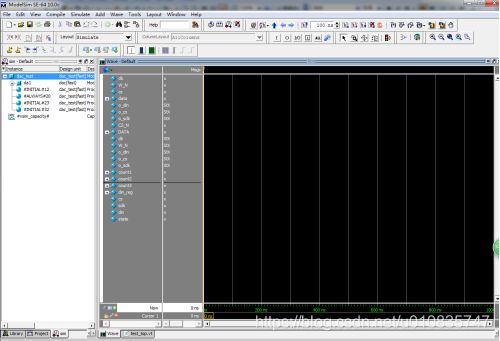

开始仿真,如图5-2-3-3和图5-2-3-4

图5-2-3-3开始仿真

图5-2-3-4仿真界面

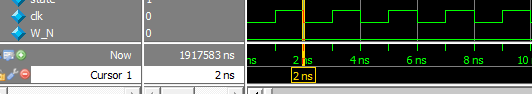

(4)仿真结果

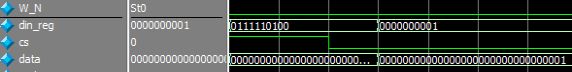

图5-2-4-1仿真截图一

由图5-2-4-1可以知道,产生时钟周期2ns与我们激励程序一致,

图5-2-4-2仿真截图二

由图5-2-4-2可以知道,spi时钟与输入时钟周期存在10倍关系与设计里面输出对输入10分频一致,输入片选和接收到的一致,验证了设计中时钟和片选信号。

图5-2-4-3仿真截图三

由图5-2-4-3可以知道,输出寄存器的数值是在写使能和片选同时选通的情况下才被送入,与设计一致,从而验证了设计

图5-2-4-4仿真截图四

通过仿真结果得出IP核文件设计逻辑是正确的,所以进行下面的步骤

3、IP核封装

在Quartus II里面的SOPC Builder里面:

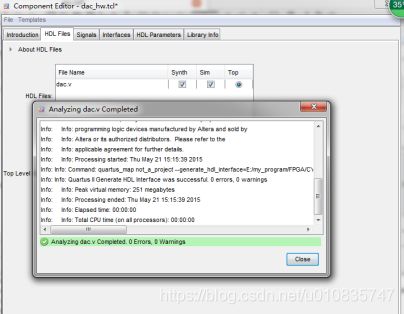

新建器件new compnemet,添加HDL文件,如图5-3-1

图5-3-1添加HDL文件

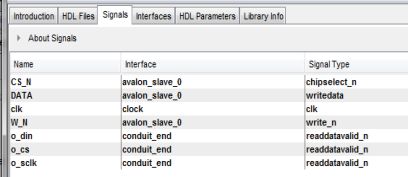

手动修改信号类型,如图图5-3-2

图5-3-2修改信号

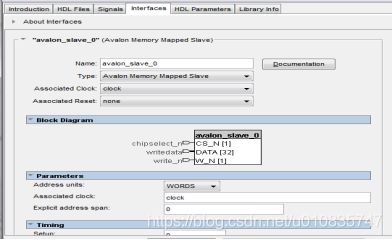

信号之间的连接,如图图5-3-3

图5-3-2修改信号连接

修改显示名字和分组,如图5-3-3

图5-3-3修改名字和分组

至此,IP核封装完成

六、D/A接口IP核在SOPC里面的应用

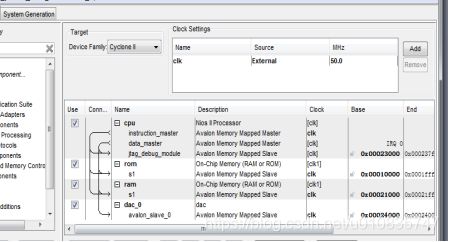

1、构建SOPC系统

添加CPU:在左侧菜单里面找到Nios II Processor,添加进工程,选择经济型cpu,和精简型jtag,完成并修改名字为cpu

添加rom:在菜单里面找到On Chip ROM Or RAM,添加进工程,选择rom参数,修改大小为8192即8K,完成并修改名字为rom

添加ram:在菜单里面找到On Chip ROM Or RAM,添加进工程,选择ram参数,修改大小为2048即2K,并去掉从外部烧录程序的选项,完成并修改名字为ram

添加TLC5615的IP核:在菜单里面找到刚刚添加的IP核,添加进工程,完成

设置CPU起始指针为ram,复位指针为rom

在system选项里面,分配基地址和分配中断号,然后编译,如图6-1-1

图6-1-1 构建sopc系统图

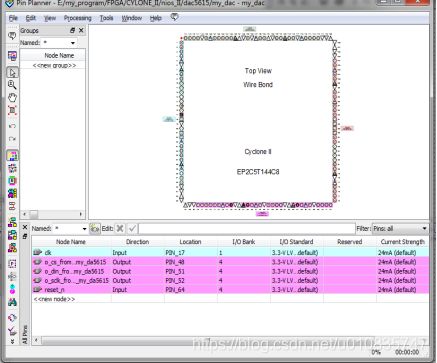

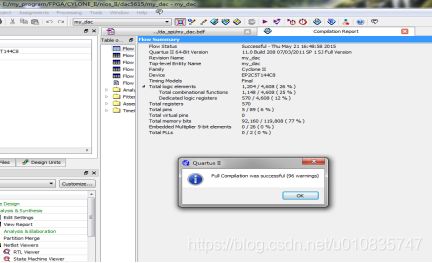

2、在Quartus II里面配置管脚约束生成硬件配置信息

在quartusII里面的原理图上添加刚刚所生成的SOPC系统的原理图,管脚约束,分析编译然后编译,至此硬件设计完成,SOPC系统图如图6-2-1,管脚约束如图6-2-2,图6-2-3编译

图6-2-1 SOPC系统图

图6-2-2管脚约束

图6-2-2编译

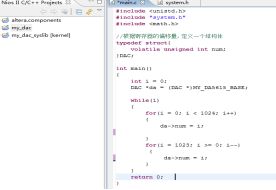

3、Nios II IDE里面三角波程序设计

(1)三角波原理

三角波:英文Triangle wave,是一种非正弦的波形,它的名字来源于波形的形状,三角波的波形形状就是一个三角形,主要用在CRT作显示器件的扫描电路,例如示波器电路、显像管电路、显示器等。CRT是由许多点组成的.要形成光栅就要有电子束轰击这些发光点.扫描电路分,水平和垂直扫描两种。可以一行或一帧的对CRT进行扫描,电子束从第一行或帧的一端开始扫到另一端,马上返回扫第二行或第二帧…三角波的特点,是电压渐渐增大突然降到零.正好适合用于扫描电路中,并且是连续周期性的,硬件实现方法是用恒流源对电容充电,电容的电压会成三角波变化,本设计采用for循环产生一增一减的线段进行拼接连续输出

(2)建立Nios II工程

打开niosII IDE

新建niosII应用程序工程:file—new—Nios II C/C++ Applacation

给工程命名,链接SOPC builder生成的PTF文件,选择空白工程,如图6-3-2-1

图6-3-2-1建立nios II工程

添加源程序文件:file—new—source file,命名,如图6-3-2-2

图6-3-2-2建立c文件

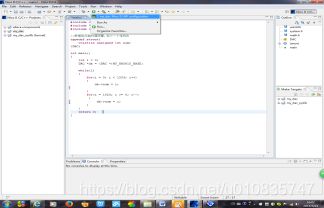

在源文件上面编写软件程序,如图6-3-2-3

图6-3-2-3 编写c程序

首先定义一个da数据结构体,

然后将da数据寄存器地址映射到结构体

初始化寄存器

进入超级循环while(1)

使用两个for循环递增递减生成三角波程序

如图6-3-2-4

图6-3-2-4三角波代码

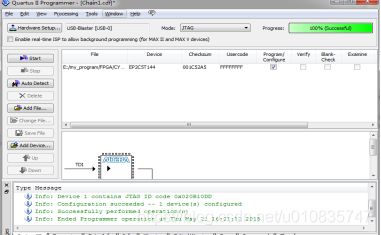

编译,连接好硬件,通过jtag口烧写软件程序和硬件软核程序到目标板,下载硬件到目标板如图,下载软件到目标板如图6-3-2-5和图6-3-2-6

图6-3-2-5 下载硬件信息到目标环境

图6-3-2-6下载软件程序到目标环境

(3)设计结果

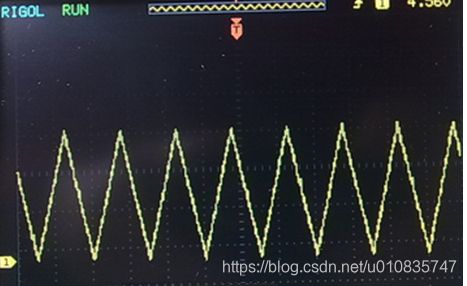

图6-3-3-1示波器结果

通过观察示波器中的三角波波形验证了本设计ip核在SOPC系统里面正常运行,如图6-3-3-1示波器采集到的三角波。

七、结论

通过本文提出nios ii处理器的串行D/A转换接口的设计实现方法,介绍了FPGA设计中采用的所有技术,以及FPGA设计的流程细节,基于采用verilog HDL语言编写IP和驱动通过方案比较确认是最合适的解决方法,采用单片机、单片机与CPLD、CPLD、FPGA几种方案进行对比证明出当前方案的优越性,通过quartusII设计出TLC5615 D/A转换IP核的.V文件,通过Moldelsim仿真工具编写testbench激励块程序链接所编写的HDL文件仿真出波形,通过仿真波形结果的分析,证明了TLC5615的IP核文件逻辑设计的正确性。然后通过硬件开发工具Quartus II里面的SOPC builder工具软件构建SOPC系统,将TLC5615的HDL文件封装成IP核并添加进SOPC系统,通过Quartus II将原理图文件编译分配管脚再编译完成以后烧录到硬件,用niosII开发工具连接Quartus II编译生成的处理器ptf文件创建专用工程,并且在上面添加编写三角波的C语言源程序编译,然后将软件程序和硬件程序一起烧写到FPGA开发板调试,将示波器探头接触到TLC5615的输出脚观察示波器上面显示的三角波波形得出设计的TLC5615的IP核设计以及软件程序的正确性。

八、结束语

时间一晃大学四年就快结束了,回想大学四年学的东西也不少,特别是从大二暑假的电子设计大赛开始,参加一系列的电子设计比赛,去了飞思卡尔智能汽车设计大赛,合泰杯单片机设计大赛等等,收货非常得多,接触也非常的多,陆陆续续接触了很多细心指导的老师、很多志同道合的同学、很多技、很多元器件。还有一个多月就要离校了,首先要感谢曾经在带队的指导老师,特别是晏康老师、文远熔老师和刘宵慧三位老师,感谢你们在比赛的时候细节指导。

这个毕业设计从去年到现在也差不多半年多了,通过这半年的毕业设计让我在FPGA上面收获很多。同时也感谢学学校给我们提供这样一个学习平台,让我们可以收货更多,其次也非常感谢文远熔老师在这次毕业设计上的细心指点,让我对FPGA设计流程有了深刻的认识,对FPGA有行业有了一定了解。

最后,感谢重庆工商大学,让我们大家在这里相遇,在一起学习,一起玩耍,一起收获,相信它在以后路上会越来越强大。

参考文献

[1]美Samir Palnikar,Verilog HDL数字设计与综合(第二版),北京:电子工业出版,2009

[2]美Janick Bergeron,编写测试平台(第二版),北京:电子工业出版社,2006

[3]美Stephen Prata,C Primer Plus(第五版),北京:人民邮电出版社,2008

[4]美Michael D.Ciletti,Verilog HDL高级数字设计(第二版),北京:电子工业出版社,2014

[5]杨军,张伟平,面向SOPC的FPGA设计与应用,北京:科学出版社,2012

九、附录

1、TLC5615的IP核Verilog HDL文件

2、testbench测试激励块程序文件

3、niosII IDE三角波C语言源程序文件