L12D9 ARM汇编指令集

一、状态寄存器传送指令

状态寄存器传送指令:访问(读写)CPSR寄存器

除了状态寄存器传送指令,其他指令都不能更改CPSR,防止系统崩溃

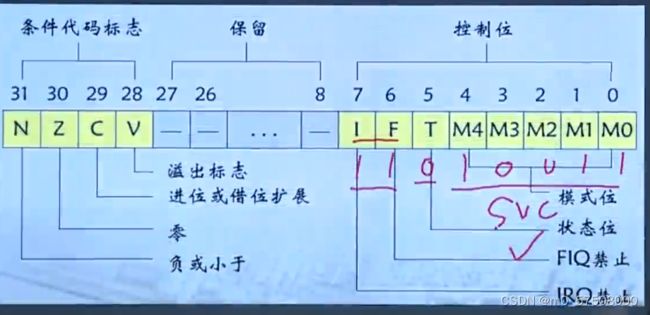

CPU刚上电之后,FIQ、RIQ默认为1,执行核心程序,CPU不希望被中断,此时处于SVC模式。

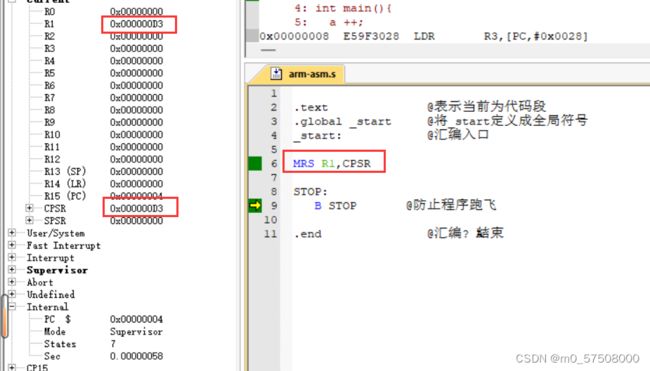

(一)读CPSR指令 MRS

MRS R1,CPSR0x000000D3处于CPSR模式,FIQ、RIQ为1

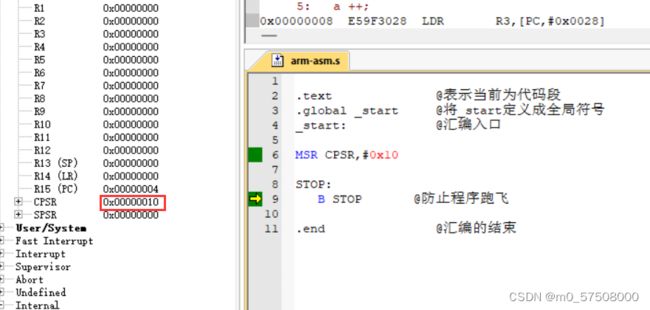

(二)写CPSR指令 MSR

MSR CPSR,#0x100x00000010 用户模式,FIQ、RIQ为0

(三)CPU模式的优先级

SVC模式特权比USER模式大,所以可以通过SVC模式进入USER模式,但是不能人为修改从USER模式到SVC模式

(四)C语言中的应用

C语言中一般没有直接代码去修改CPU的模式。

当系统启动完成后,打开应用APP,系统会自动切换CPSR模式;在进行系统调用的时候,系统进入内核模式,CPU切换到SVC模式,完成对磁盘的读写,返回到程序,系统切换成USER模式,因此状态寄存器传送指令,实际上在系统中频繁使用。

二、软中断指令

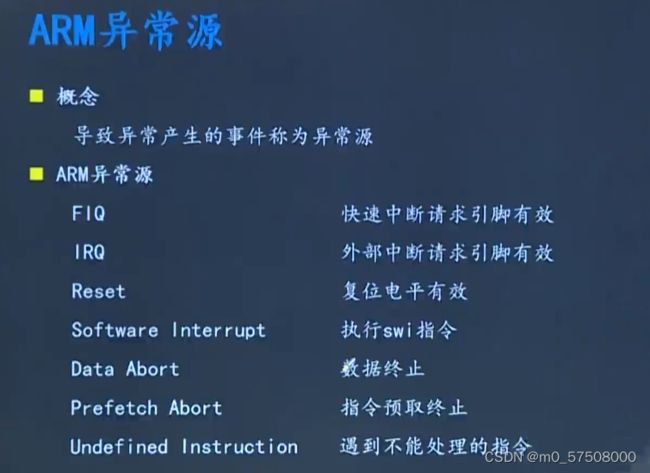

(一)ARM异常源

FIQ、RIQ是硬件中断,按键、网卡等,与之对应的是软中断,由软件或者一条指令产生。

(二)ARM异常模式

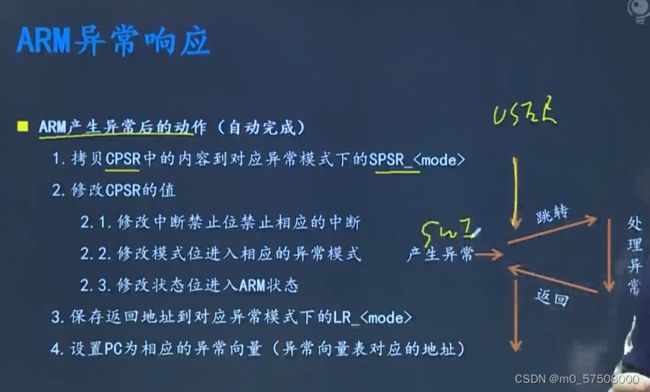

(三)ARM异常响应

异常响应是由CPU自动完成,设置PC为相应的异常向量。

(四)异常返回

(五)软中断指令 SWI

软中断过程基本遵循中断流程

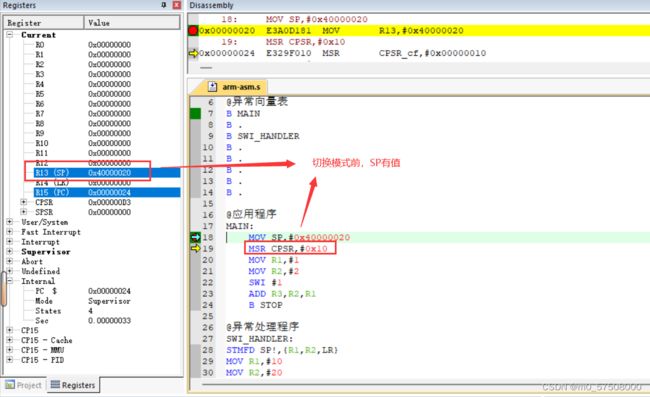

@异常向量表

B MAIN

B .

B SWI_HANDLER

B .

B .

B .

B .

B .

@应用程序

MAIN:

MOV SP,#0x40000020

MSR CPSR,#0x10

MOV R1,#1

MOV R2,#2

SWI #1

ADD R3,R2,R1

B STOP

@异常处理程序

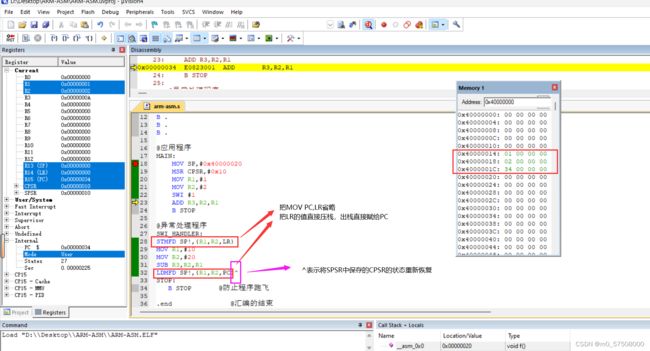

SWI_HANDLER:

STMFD SP!,{R1,R2,LR}

MOV R1,#10

MOV R2,#20

SUB R3,R2,R1

LDMFD SP!,{R1,R2,PC}^

执行流程注意事项

1、CPU在不同模式的SP

CPU在不同模式的SP不相同,可以分别设置,在软中断中,设置SP内存指针要在进入用户模式之前,因为执行软中断时的压栈操作在SVC模式,因为要在复位之后先设置SP指针。

2、执行软中断,CPU进入异常处理模式

当系统启动完成后,打开应用APP,系统会自动切换CPSR模式;在进行系统调用的时候,系统进入内核模式,CPU切换到SVC模式,完成对磁盘的读写,返回到程序,系统切换成USER模式,因此状态寄存器传送指令,实际上在系统中频繁使用。

软中断指令后面会跟不同的参数,不同参数代表着不同类型的系统调用,系统调用分为对磁盘读写、网卡读写等。

例:SWI_HANDLER

三、协处理器指令

协处理器指令是控制协处理器的指令

协处理器也是一种处理器,ARM最多可以添加16个协处理器,协处理器可以执行一些ARM不能执行的指令,例如图像处理等,以ARM为主,协处理器为辅。

三星等半导体场也会根据自己的需求设计协处理器,例如手机SOC,需要添加处理手机特殊指令的协处理器,视频处理器需要添加处理视频指令的协处理器。

(一)常用的协处理器

1、浮点型协处理器 FPU

2、管理存储器协处理器 CP15

高速缓存

重新设置异常向量表的位置:例可以修改软中断处理向量SWI在内存中的地址,进行重新定位

MMU:管理物理内存和虚拟内存之间的转换关系,进程使用物理内存,内存分配小,甚至产生地址越界,Linux使用虚拟内存,每个进程分配4G,进程之间使用的内存是独立的。

(二)协处理器指令

1、协处理器数据运算指令

CDP

2、协处理器访问内存指令

1)STC 将协处理器中的数据存储到存储器

2)LDC 将存储器中的数据读取到协处理器

3、协处理器寄存器传送指令

1)MRC 将协处理器中寄存器的数据传送到ARM处理器中的寄存器

2)MCR 将ARM处理器寄存器中的数据传送到协处理器中的寄存器

四、伪指令

指令:能够编译生成一条32位的机器码,且能被CPU识别和执行

伪指令:本身不是指令,编译器可以将其替换成若干条指令

例:3*3 -> 3+3+3

(一)NOP 空指令

单片机开发,什么指令都不做,但是消耗一个CPU指令的执行时间

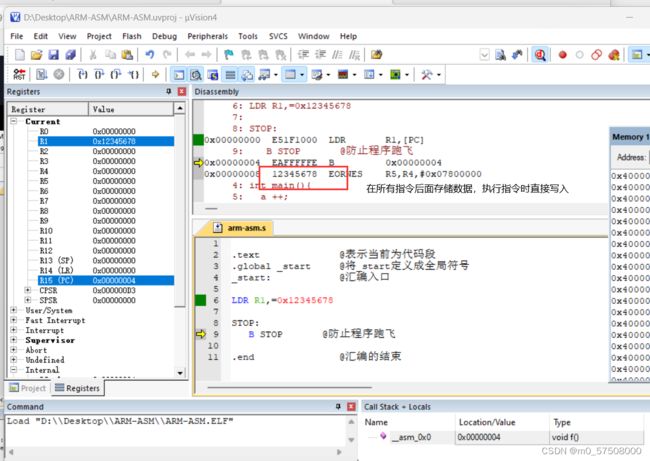

(二)LDR

ARM指令集中最特殊的一条指令

1、可以做指令

LDR R1,[R2]

@将R1的内容写入R2地址指针指向的地址2、可以做伪指针

LDR R1,=0x12345678

@可以将任意一个32位数据写入寄存器

LDR R1,=STOP

@把STOP的地址给R1LDR R1,STOP

@将STOP地址中的内容写入R1寄存器五、作业

1.编程实现通过状态寄存器传送指令,将ARM处理器的模式修改成USER模式并将FIQ与IRQ使能

2.简述伪指令和指令的本质区别是什么

1、MSR CPSR,#0x10

2、指令可以直接被CPU识别和执行,伪指令本身不是指令,编译器可以将其替换成若干条指令。