2020年vivo数字IC设计/芯片设计笔试题解析(1)

单选1~17题,给出答案和分析。

PDF版可在【FPGA探索者】公众号回复【vivo笔试1】获取。

2023届FPGA/PGA/数字IC实习秋招群:676475325

1. 原码、补码、反码

1. 十进制数-1,用4位二进制表示的原码、补码、反码分别是()

A. 1001B0111B1110B

B. 1111B0111B1000B

C. 1111B1110B1000B

D. 1001B1111B1110B

答案:D

解析:

有符号数表示,正数的原码、反码、补码一样,重点是负数采用补码表示。

(1)4位二进制表示负数,最高位是符号位,负数的最高位是1,非负数的的最高位为0;

(2)还剩三位表示数据大小,3 bit的1是3’b001,考虑符号位4’b1001,负数要用补码表示,补码是反码+1;

(3)反码:3’b110,考虑符号位为4’b1110;

(4)补码:3’b110+3’b001 = 3’b111;

(5)补码加上符号位:4’b1111;

重点:原码取反得到反码时,是去掉符号位的其他位取反,最后再补上符号位;

2. 验证覆盖率

2. 下面哪种不属于验证覆盖率

A. 状态覆盖率

B. 翻转覆盖率

C. 条件覆盖率

D. 循环覆盖率

答案:D

解析:

验证覆盖率:代码覆盖率+功能覆盖率

代码覆盖率有:语句(行)覆盖率、状态(状态机)覆盖率、翻转覆盖率、条件覆盖率、分支覆盖率等;

功能覆盖率需要设置覆盖点、覆盖组等;

3. 跨时钟域

3. 下面哪个不属于跨时钟域数据传递的基本方法

A. 使用握手协议

B. 使用多级触发器缓冲

C. 信号通路上插入islocation

D. 使用FIFO

答案:C

解析:

C中的isolation的用途:电源上的隔离,低功耗用途

单bit:

慢——>快:打拍;

快——>慢:握手;

多bit:

异步FIFO,握手,DMUX;

连续变化的地址数据可以用格雷码;

4. 低功耗问题

4. 下列功耗措施哪个可以降低峰值功耗?

A. 静态模块级clock gating

B. memory shut down

C. power gating

D. 大幅度提高HVT比例

答案:D

解析:

功耗 = 静态功耗+ 动态功耗;峰值功耗是运行中的瞬时最大功耗,主要是动态功耗;

A. 明显是降低静态功耗;

B. 存储器关断技术,在不使用存储器的时候让存储器低功耗,降低静态功耗;

C. 电源关断技术,与静态功耗有关;

D. HVT是高阈值电压晶体管(High Voltage Threshold),在供电电压一定的情况下,高阈值的晶体管开启的慢,相应的降低了数据的翻转率,降低动态功耗;并且高阈值晶体管还降低了漏电流,降低静态功耗;

参考:数字IC笔试题(7)——低功耗设计【静态功耗】【动态功耗】

5. FIFO深度计算

5. 有一个FIFO设计,输入时钟100 MHz,输出时钟80 MHz,输入数据模式是固定的,其中1000个时钟中有800个时钟传输连续数据,另外200个空闲,请问为了避免FIFO下溢/上溢,最小深度是多少

A 320

B 80

C 160

D 200

答案:C

解析:

(1)因为题目说的是“输入数据模式是固定的”,所以不用考虑“背靠背”情况,即不考虑在2000个时钟里有1600个时钟连续传输数据,只考虑1000个时钟里连续有800个时钟传数据;

(2)在连续传输的800个时钟里,写入100MHz,每个写入时钟周期是1 / (100MHz) = 10 ns,共需要800 / (100 MHz) = 800 * 10 ns;

(3)读出时钟80MHz,读出时钟周期1 / (80MHz) = 12.5 ns,在写入800个数据的 800*10 ns的时间段内,能够读出 800*10 / 12.5 = 640个;

(4)需要FIFO深度:800-640 = 160个;

简便计算:

数据量 * (1 - 读时钟频率 / 写时钟频率)

800 * (1-80MHz/100MHz)=800*(1-4/5)=800*1/5=160

参考:FIFO深度计算总结

数字IC笔试题(12)——FIFO深度计算【异步FIFO】【同步FIFO】

6. 跨时钟域、格雷码

6. 假设一个3 bit计数器(计数范围0-6),工作在58 MHz时钟域下,要把此计数器的值传递到另一个异步100 MHz时钟域,以下不正确的是

A 使用异步FIFO

B 锁存+握手信号

C 使用格雷码

D 使用DMUX电路

答案:C

解析:

计数值,连续变化的计数值,多bit:

(1)异步FIFO没问题,单bit、多bit、时钟快慢、数据类型不论,通吃;

(2)锁存+握手没问题,单bit、多bit均可,时钟快慢均可,典型握手例子:AXI总线;

(3)格雷码看似没问题,实际有问题,问题出在计数值是0~6,奇数个计数值,没办法保证格雷码编码后相邻数据仅1 bit不同,这里0计数到6再回到0重新计数,0和6用格雷码表示时不止1位不同;

如果题目是计数范围0~7,在格雷码没问题;

(4)DMUX没问题,主要利用单bit的跨时钟实现多bit的跨时钟;

7. 有符号数加法、补码

7. X和Y均为补码表示的二进制,其中X=10010010B,Y=10001011B,下列选项中X+Y正确的是

A. 110011101B

B. 011100011B

C. 111100010B

D. 100011101B

答案:D

解析:

有符号数+有符号数,可以用位拼接符做符号位扩展以后再加;

(1)X = 8’b1001_0010 = -110;

(2)Y = 8’b1000_1011 = -117;

(3)X+Y = {X[7], X} + {Y[7], Y} = 9’b1_1001_0010 + 9’b1_1000_1011 = 9’b1_0001_1101 = -227;

第二种解法比较复杂:把两个有符号数都转换成十进制,加完得到-227,再转回有符号表示;

8. 时钟相关概念

8. 时钟的占空比指的是

A. 时钟的变化速度

B. 时钟的变化范围

C. 低脉冲的持续时间与脉冲总周期的比值

D. 高脉冲的持续时间与脉冲总周期的比值

答案:D

解析:无需解析,概念问题。

9. 时序问题、最大时钟频率计算

9. D触发器Tsetup=3ns,Thold=1ns,Tck2q=1ns,该D触发器最大可运行时钟频率是

A. 1GHZ

B. 250MHZ

C. 500MHZ

D. 200MHZ

答案:B

解析:

Tclk >= Tsetup + Tck2q = 4 ns;所以最大运行时钟250 MHz。

Thold与时钟的最大频率无关。

10. 低功耗问题

10. 逻辑电路低功耗设计中,无效方法是

A 采用慢速设计

B 减少信号翻转

C 采用较慢速的时钟

D 提高阈值电压

答案:A

解析:

A. 不一定;

B. 降低翻转率,可以降低动态功耗;

C. 降低时钟频率,可以降低动态功耗;

D. 使用高阈值电压晶体管HVT,降低漏电流,可以降低静态功耗;

11. Verilog语法

11. 以下verilog运算符优先级由高到低正确的是

A. ! ,&, ^, |, &&

B. ^, !,&,|,&&

C. !,|,&,&&,^

D. &,|,&&,^,!

答案:A

解析:

12. 低功耗问题

12. 在RTL设计阶段,降低功耗的常用设计方法是

A 门级电路的功耗优化

B 门控时钟

C 降低电路漏电流

D 多阈值电压

答案:A

解析:

以上都是低功耗方法,但是注意题目要求是在“RTL设计阶段”,所以是B,在代码设计时插入门控时钟。

A. 门级电路的功耗优化(Gate Level Power Optimization),对门级网表层次优化,也叫体系结构级,主要有电源门控、多阈值、多电压、异步设计等;

B. RTL级:门控时钟(对时钟的使能),信号使能(对数据的使能),流水线,状态机编码(格雷码、独热码编码)等;

数字IC笔试题(7)——低功耗设计【静态功耗】【动态功耗】

13. Verilog语法

13. 下面哪个不是循环关键字

A. repeat

B. forever

C. while

D. fork

答案:D

解析:

fork...join,注意与begin...end的区别

参考:Verilog 的块语句 fork...join 和 begin...end

14. 形式验证

14. netlist(网表)一般通过什么手段进行验证其正确性

A. 随机验证

B. RTL验证

C. 形式验证

D. 网表验证

答案:C

解析:

形式验证+静态时序分析

功能上:形式验证

时序上:STA静态时序分析

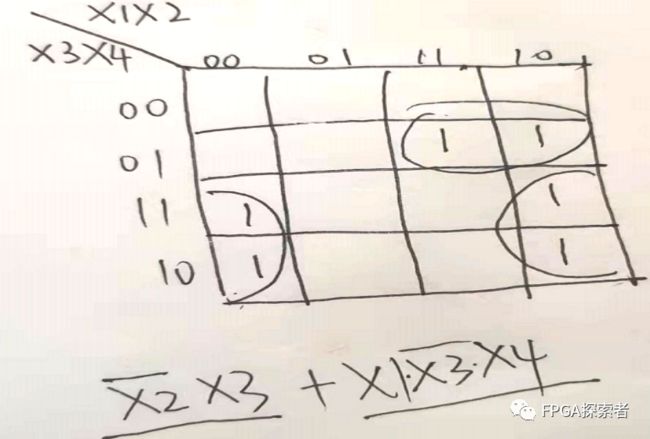

15. 数字电路基础、真值表、卡诺图

15.下图为组合逻辑Y=f(x1,x2,x3,x4)的真值表,请根据真值表选择Y的逻辑表达式

A. (~x2)x3 + x3x4;

B. (~x2)x3 + x1x3x4;

C. x2x3 + x1(~x3)x4;

D. (~x2)x3 + x1(~x3)x4;

答案:D

解析:

卡诺图化简

参考:来看个联发科秋招的大题(5)——逻辑化简、最小项、卡诺图、反演律、0-1律

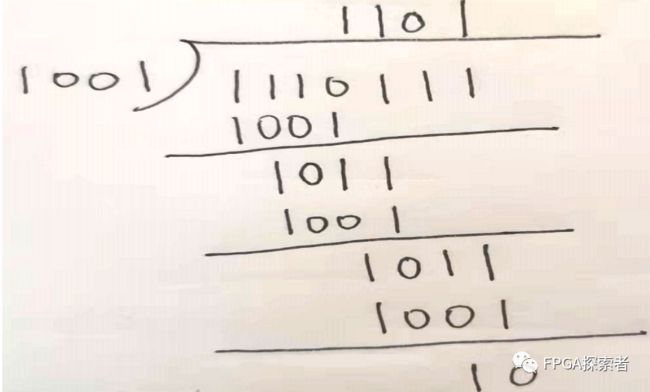

16. 无符号数除法

16.无符号二进制除法1110111B/1001B的结果是

A 商:1101B , 余数:110B

B 商:1101B , 余数:110B

C 商:1101B , 余数:10B

D 商:101B , 余数:10B

答案:C

解析:

实在不会做就换算成十进制去除,然后把商和余数再变到二进制;

17. 组合逻辑竞争冒险

17.组合逻辑电路的冒险现象是由于()引起的;

A. 电路未达到最简

B. 电路存在延时

C. 逻辑门类型不同

D. 电路有多个输出

答案:B

解析:概念问题,无需解析。

参考:组合逻辑竞争冒险,时序逻辑亚稳态【0型冒险和1型冒险及其消除方法】

往期好文:

笔试 | 1bit的半加器、全加器实现

笔试 | Verilog串并转换代码(in_valid不连续)

FPGA/数字IC实用笔试面试刷题汇总

23届FPGA/数字IC秋招备战群