ZYNQ | AXI DMA数据环路测试

利用AXI DMA进行批量数据环路的测试

- 背景

-

- 软硬件平台

- 原理概述

- 工程搭建

-

- 1.新建一个vivado工程

- 2.创建block design

-

- ①zynq ip核的添加与配置

- ②AXI DMA ip核的添加与配置

- ③AXI4-Stream Data FIFO核的添加与配置

- ④让vivado自行添加余下ip核

- ⑤连接未连接的部分

- ⑥可选:添加ILA ip核观察DMA的2个中断信号

- 3.新建一个SDK工程

- 4.放入源码

- 5.验证测试

- 参考文档

背景

由于最近项目需要使用到AXI DMA来进行数据的传输,于是搭建了一个AXI DMA的环路来对AXI协议和DMA进行学习。

软硬件平台

软件平台:vivado2018.3 SDK开发套件

硬件平台:米联客MZ702N

原理概述

本实验通过PS端的ARM先将数据发送给DDR,然后PS端控制DMA通过数据通道读取DDR中的数据,DMA将读取到的数据传给FIFO,FIFO又将数据传输给DMA,PS控制DMA通过数据通道将数据写入DDR中,控制DMA对DDR数据进行读写和校验,完成环路测试,然后进行传输校验,当接收与发送的数据不一致的时候,进行报错。

工程搭建

1.新建一个vivado工程

2.创建block design

①zynq ip核的添加与配置

点击上图中右侧的+,输入zynq,双击添加zynq ip核。

添加完后,双击zynq ip核,进行如下配置。

配置结束后点击OK,可以看到下图界面。

点击Run Block Automation,可以看出引出了DDR和FIXED_IO,手动连接FCLK_CLK0和M_AXI_GP0_ACLK。

至此,zynq ip和的配置结束。

②AXI DMA ip核的添加与配置

该ip核的添加方式仿照添加zynq ip核的方式,点击+,输入AXI DMA,双击添加ip核。

双击ip核,按下图配置。

③AXI4-Stream Data FIFO核的添加与配置

点击+,输入AXI4-Stream Data FIFO,双击添加ip核。

④让vivado自行添加余下ip核

必要的ip已经添加完毕,剩下的可以通过点击Run Connection Automation来让vivado自行添加(当然你也可以手动添加), 勾选Run Connection Automation界面中的All Automation,点击OK,vivado即刻为你连线。

小技巧:Regenerate Layout,没事就 Regenerate Layout 一下

上图即为Regenerate Layout后的block design。

可以通过在上图空白处点击右键 > Regenerate Layout来实现重新排线,使得block design变得整洁。

⑤连接未连接的部分

由于本实验是进行回环测试,所以需要将 AXI4-Stream Data FIFO 的 一些端口连接到 AXI DMA 的一些端口,如下表所示:

| S_AXIS(FIFO) | 连接到 | M_AXIS_MM2S(AXI DMA) |

| M_AXIS(FIFO) | 连接到 | S_AXIS_S2MM(AXI DMA) |

| s_axis_aresetn(FIFO) | 连接到 | peripheral aresetn(Processor System Reset) |

| s_axis_aclk | 连接到 | FCKL0(zynq ip) |

连接完成后如下图所示:

现在还剩最后的中断部分没有连接,我们把DMA的2个中断信号,通过concat ip连接到zynq ip核,concat ip如下:

concat ip配置如下:

连接方法如下表所示:

| mm2s_introut | 连接到 | in0 |

| s2mm_introut | 连接到 | in1 |

| dout | 连接到 | IRQ_F2P |

⑥可选:添加ILA ip核观察DMA的2个中断信号

我们通过添加ILA ip来观察DMA的中断信号mm2s_introut和s2mm_introut,点击+,输入ILA,双击添加ip核,ip核如下:

| clk | 连接到 | FCLK_CLK0(zynq ip) |

| probe1 | 连接到 | s2mm_introut(DMA) |

| probe0 | 连接到 | mm2s_introut(DMA) |

连接完成后如下图:

至此就完成了工程框架的搭建。保存BD工程,先点击图中序号①处的图标进行验证,验证操作会对整个BD工程进行验证以及调整,验证成功后,点击左侧BD工程 > 右键 > Generate Output Products,成功后,点击 Create HDLWrapper,成功后,生成bit流文件。

生成bit流文件后,点击菜单栏中的File > Export >Export Handware,然后点击Launch SDK,然后进入sdk开发部分。

3.新建一个SDK工程

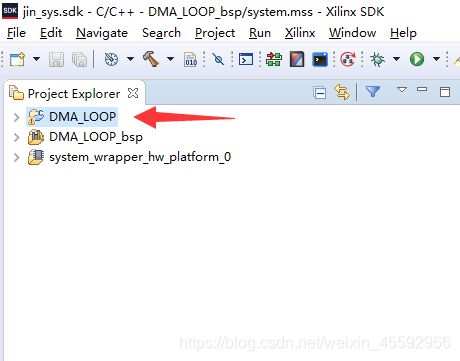

打开SDK软件后,点击菜单栏中的File > New >Application Project,新建一个工程。本文工程名为DMA_LOOP。

点击Next,选择Empty Application >Finish ,工程创建完毕。

4.放入源码

将米联客提供例程中的SDK工程的源文件复制。

打开SDK,点击SDK工程中src右键粘贴,软件会自动编译。

粘贴完后可见到下图所示。

5.验证测试

step1:在SDK中,点击DMA_LOOP文件夹,右键 >Debug As>Debug Configurations > 双击序号① > 勾选序号②③ > 点击Apply ,完成到这步时候,连接好FPGA的电源,串口线(用来打印信息),jtag线(用来下载bit流文件到板子上),打开电源,点击Debug,之后会跳出Debug调试界面。

step2:在Debug调试界面连接好串口显示(SDK Terminal),点击下图右侧加号,选择好串口对应的com号和波特率,点击OK。

显示下图即为串口连接成功。

小tips:串口号可以在我的电脑,右键管理 >设备管理器中的端口选项中查看。

step3:设置ila触发。在vivado工程中点击Open Target>Auto Connect

连接成功后如下图:

设置触发条件、观察信号。

(1)设置波形偏移500。

Settings >Trigger position in window:500

(2)Trigger Setup > 点击+添加触发信号axi_dma_0_mm2s_introut,设置Value为R。如图所示。

(3)点击序号⑤处,使得Ila处在等待触发状态。

step4:SDK中点击运行

当中断触发的时,VIVAIDO中Hardware Manager出现捕捉波形,如下图所示:

SDK端显示:

step5:观察数据

打开Memory:Window >Show View > Memory

点击添加要观察的数据的地址,可以通过该地址来观察内存中的数据,地址为0x13000000

点击加号,输入0x13000000

为了观察一次收发数据:设置断点,重新让收发程序跑一次。

重新运行一次程序 ,收发一次,从内存中读取的数据如图:

发送量是2047。接收数据一致,测试结束。可以看到第一个数据是0x0c,后面是依次加1,一次接收的数据量是2047。发送数据也是0x0c后面依次加1,至此AXI DMA数据回环测试结束。

参考文档

米联客XILINX_ZYNQ裸机篇2019版