Vivado的安装以及使用

零. Vivado简要介绍

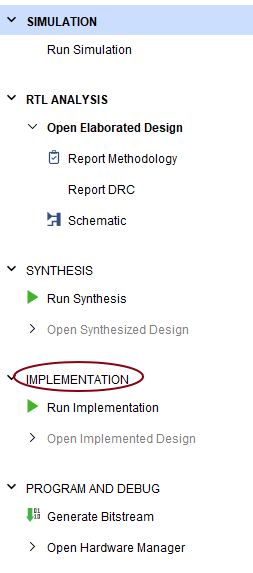

Vivado是FPGA厂商赛灵思提供的一款EDA(Electronic Design Automation)工具. 在电子设计自动化方面, 其主要提供了四种功能: RTL代码编写, 功能仿真, 综合(synthesis)以及实现(implementation).

- 其中, RTL代码编写用于编写设计的HDL描述(利用VHDL和System Verilog两种语言);

- 功能仿真用于测试编写出的代码功能是否符合预期, 需要编写相关的testbench文件;

- 综合用于讲RTL级描述转换为门级网表(门级网表是指设计的门级实现,包含门级元件和元件之间的连接, 从而更接近底层设计);

- 实现用于将门级网表转换为可以下载到FPGA开发板上的比特流.

一. vivado的安装

Vivado的安装已经有好多文章介绍过, 在这里给出一篇文章

https://blog.csdn.net/taowei1314520/article/details/74860356

二. 使用vivado完成一个小设计-计数器

在这里我们以一个4进制计数器的设计为例, 讲解我们如何使用Vivado进行工程设计

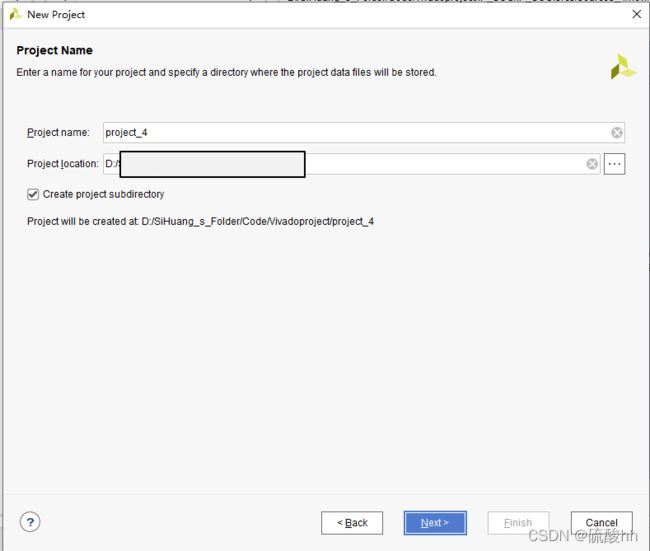

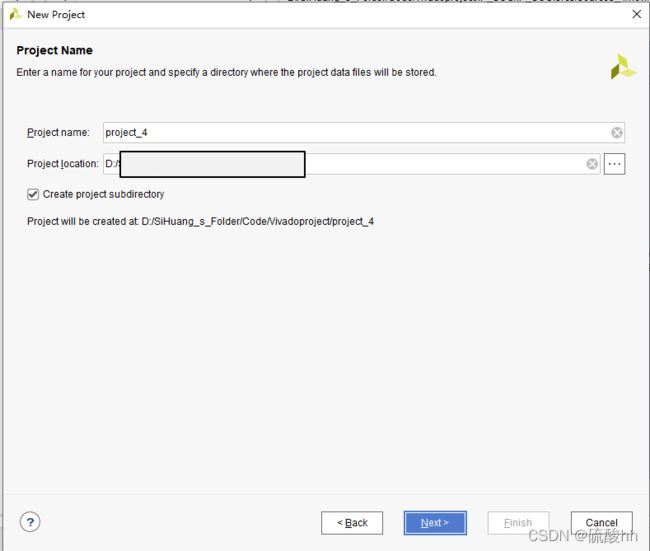

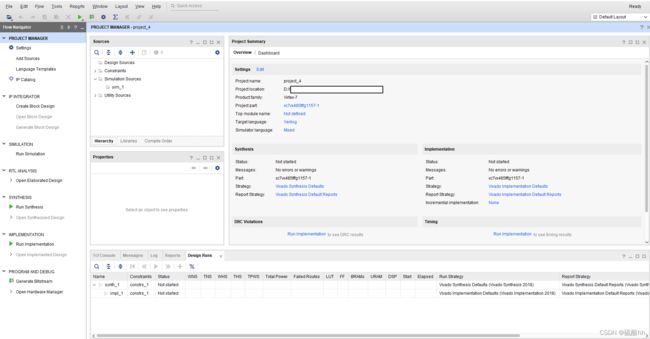

1. 新建工程

在菜单中点击file->project->new新建project

新建project的时候注意选择合适的存放路径, 然后点击next; 选择RTL Project, 点击next; 选择对应的开发板, 点击next; 点击finish, 完成工程的新建.

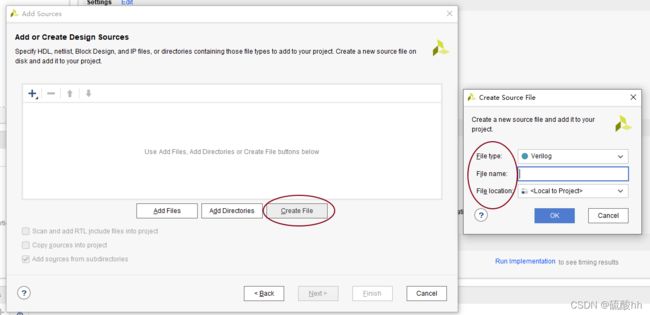

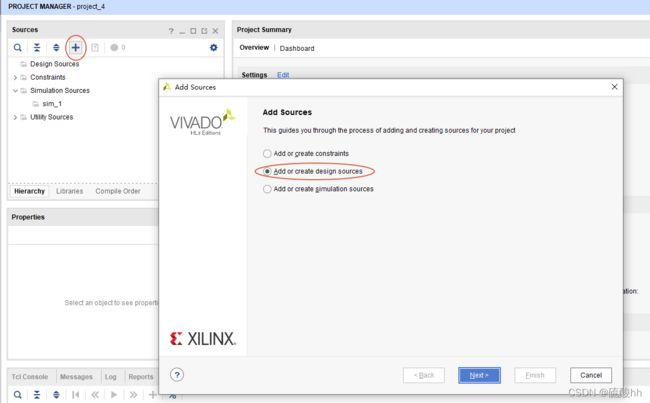

- 新建设计文件

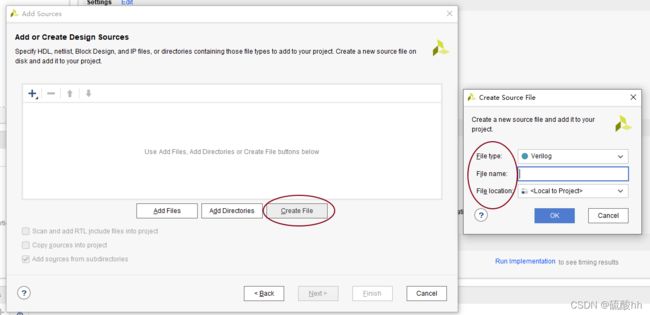

在界面中找到"Source"框, 点击"+", 选择"Add or create design sources", 点击next.

点击Creat file, 指定语言类型, 文件名字, 文件存放的位置, 完成设计文件的新建.

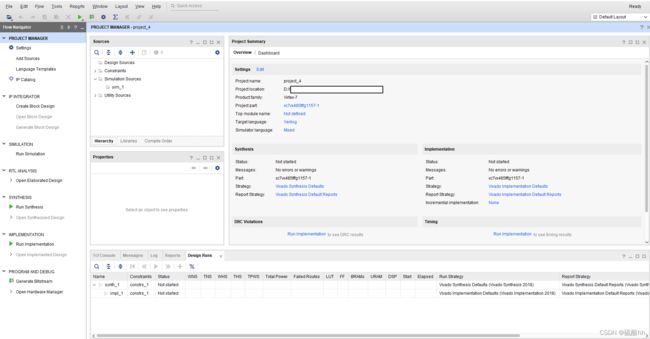

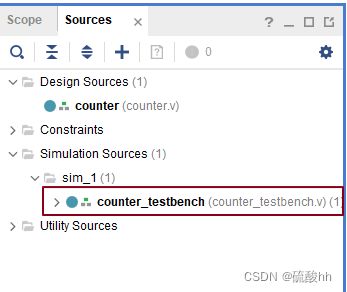

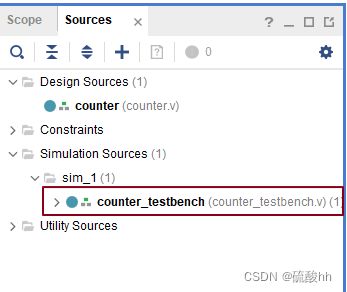

新建file之后的界面, 如下图, 双击Source的设计文件(在这里, 我命名为counter), 即可打开, 进行编辑.

- 完成设计文件的编写

这里以一个四进制的计数器为例, 代码如下所示.

module counter

#( parameter WIDTH = 4)

(

input clk,

input preset,

output reg [WIDTH-1:0] count,

output reg full

);

always @ (posedge clk or negedge preset) begin

if(~preset)begin

count <= 0;

end

else begin

count <= count+1;

end

end

always@(*)begin

full = (count==2**WIDTH-1);

end

endmodule

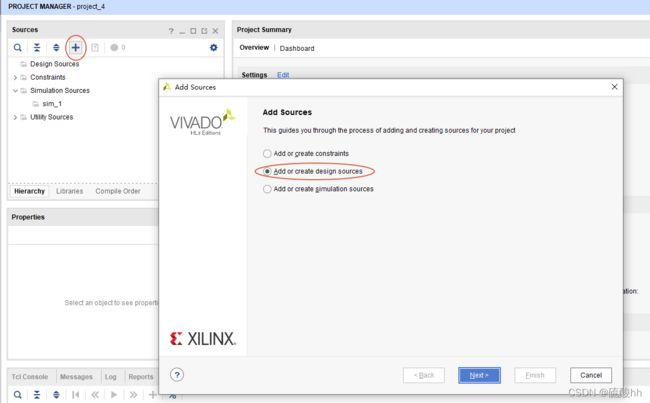

- 新建仿真文件

与新建设计文件类似

- 在界面中找到"Source"框, 点击"+", 选择"Add or create simulation sources", 点击next.

- 点击Creat file, 指定语言类型, 文件名字, 文件存放的位置, 完成仿真文件的新建.

- 双击Source窗口下面, "Simulation Sources"下的设计文件(在这里, 我命名为counter), 即可打开, 进行编辑.

- 完成仿真文件的编写

该四进制的计数器的tesetbenc文件如下:

`timescale 1ns / 1ps

module counter_testbench

#(parameter WIDTH=4)(

);

reg clk;

reg reset;

wire [WIDTH-1:0] count;

wire full;

initial begin

clk = 0;

reset = 1;

#25 reset = 0;

#25 reset = 1;

end

always begin

# 5 clk = ~clk;

end

always begin

#100;

if ($time >= 10000) $finish ;

end

counter c1(

.clk(clk),

.preset(reset),

.count(count),

.full(full)

);

endmodule

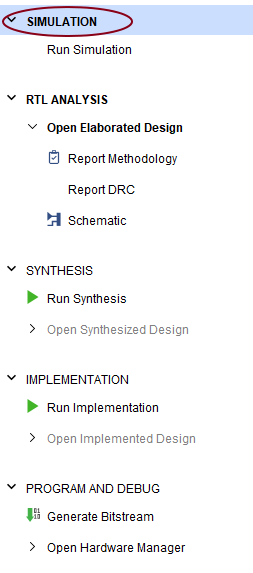

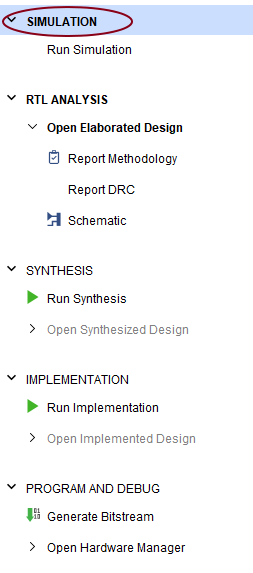

- 点击"Run Simulation"进行功能仿真

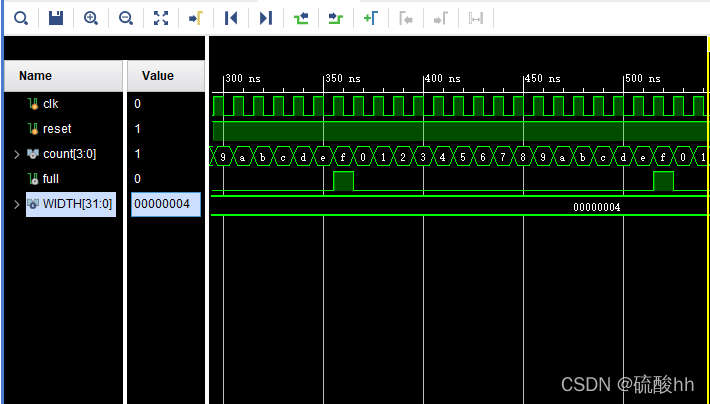

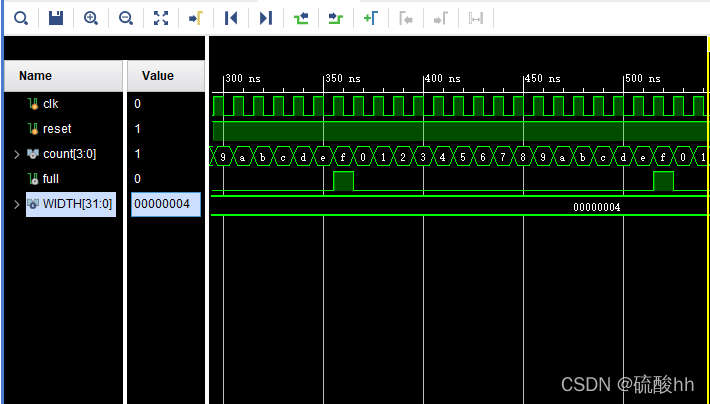

仿真结果如下图所示, 可见, 该计数器功能正常

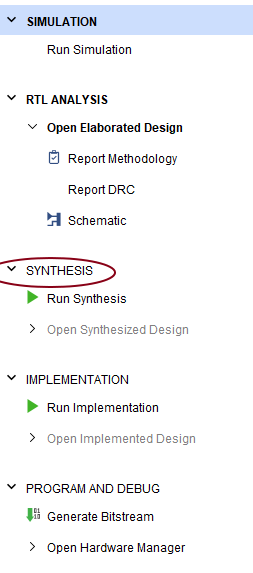

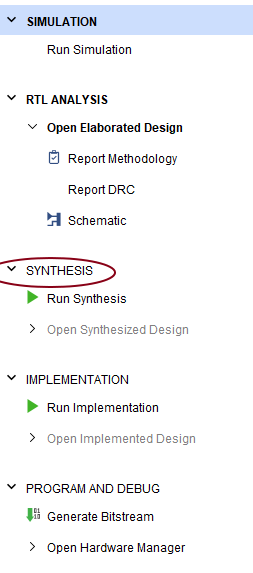

- 点击SYTHESIS按钮, 进行综合, 以获得对应门级网表

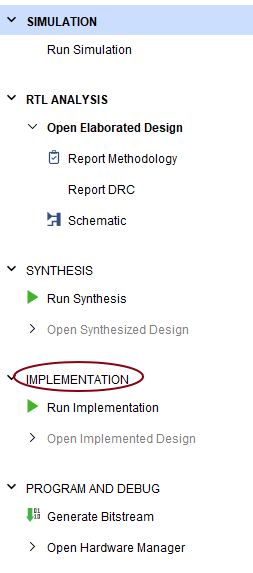

- 点击IMPLEMENTATUON按钮, 进行实现, 以获得比特流

三. 使用vivado过程中可能遇到的问题(持续更新中)

- 功能仿真时显示(current time: 0fs)

遇到这个问题, 点击结束仿真, 会跳到出现问题的那一行

可能原因:

- 在设计文件中, always没有加敏感信号列表

- 循环为死循环, 缺少跳出循环的条件

- 功能仿真时, 输出信号均为X

可能原因:

- reset信号没有连接上, 在写异步复位时候一定要严格按照以下格式(if 和 else)

always @ (posedge clk or negedge preset) begin

if(~preset)begin

count <= 0;

end

else begin

count <= count+1;

end

end

四. 扩展阅读资料

上面只是简单介绍了Vivado的部分内容, 想要更加详细, 更加具体地了解Vivado的使用, 还可以阅读Vivado的官方用户手册.查找地址: https://china.xilinx.com/products/design-tools/vivado.html#resources