TEE侧信道综述(源于论文)

目录

- 可信执行环境软件侧信道攻击研究综述(笔记)

- 典型的TEE架构

- 软件侧信道攻击的3个通用步骤

- CPU 执行指令的过程

- 微体系结构组件划分

- 侧信道攻击

-

- 瞬态执行攻击

- 分支预测攻击

- TLB侧信道攻击

- cache侧信道攻击

- 基于page table的侧信道攻击

- 基于DRAM的侧信道攻击

- 组合攻击

- 威胁模型

-

- 用户级攻击者

- 内核级攻击者

- 物理攻击者

- 防御

-

- 瞬态执行侧信道防御措施

-

- 硬件层面

- 软件层面

- 分支预测侧信道防御措施

-

- 硬件层面

- 软件层面

- TLB侧信道防御措施

-

- 硬件层面

- 软件层面

- cache侧信道防御措施

-

- 硬件层面

- 软件层面

- 基于page table的侧信道防御措施

-

- 硬件层面

- 软件层面

- 基于DRAM的侧信道防御措施

-

- 硬件层面

- 软件层面

- 组合攻击的防御措施

-

- 硬件层面

- 软件层面

可信执行环境软件侧信道攻击研究综述(笔记)

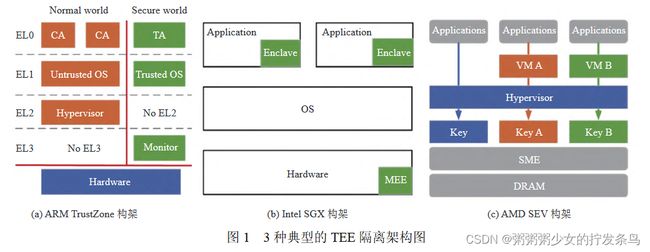

典型的TEE架构

软件侧信道攻击的3个通用步骤

(1)硬件分析阶段, 分析处理器硬件层面存在的安全缺陷, 找到能泄露受害者机密信息的微体系结构组件;

(2)攻击构建阶段, 利用软件方式构建攻击, 将硬件安全缺陷泄露的机密信息提取到不同的微体系结构组件中;

(3)提取机密信息阶段, 根据不同的微体系结构组件, 构建对应的侧信道攻击, 以微体系结构状态的形式(例如, cache侧信道攻击中的时间信息)提取机密信息.

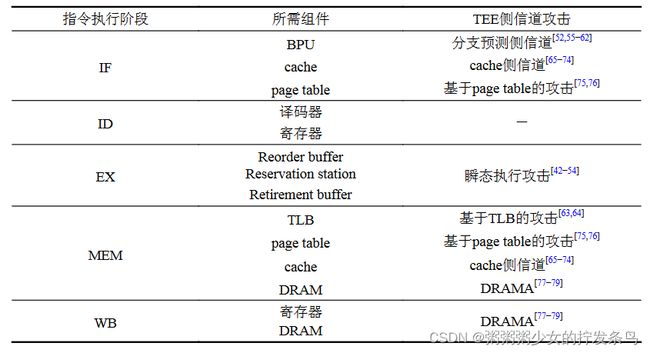

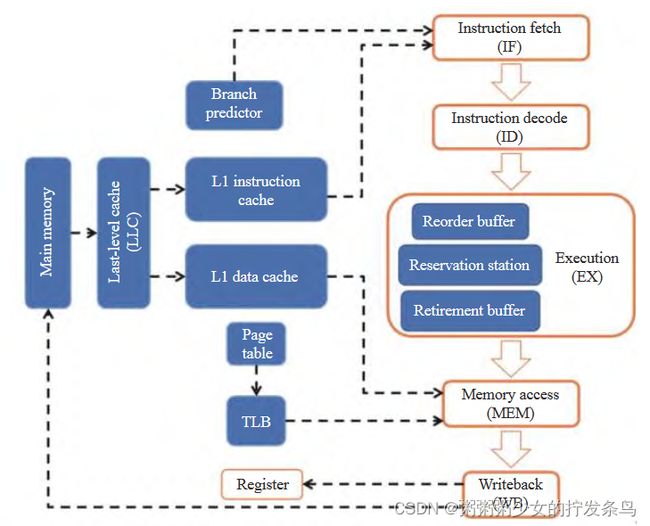

CPU 执行指令的过程

现代CPU 执行指令的过程一般分为5个阶段: 取指令(instruction fetch, IF)、指令译码(instruction decode, ID)、指令执行 (execution, EX)、内存访问(memory access, MEM)和结果写回(writeback, WB).

IF阶段CPU将一条指令从内存中取到指令寄存器, 此过程中可能涉及到的组件有cache、分支预测单元(branch prediction unit, BPU).

取出指令之后, 计算机进入ID阶段, 在该阶段, 指令译码器对取出的指令进行翻译, 识别并区分出不同的指令, 此阶段尚未发现侧信道漏洞.

当指令译码完成之后, 接着进入EX阶段, 此阶段会完成指令的具体任务, 此过程可能涉及到的组件有瞬态执行相关部件(如, reorder buffer, reservation station以及retirement buffer). 根据指令需要, 有可能要访问内存, 读取操作数,

这样就进入了内存访问(MEM)阶段, 此阶段可能涉及到的组件有TLB、page table、cache、 DRAM等.

WB阶段会把EX阶段的运行结果写回到CPU的内部寄存器或内存中.

目前已经发现的TEE软件侧信道攻击方法包括: 瞬态执行攻击、分支预测攻击、基于TLB的攻击、cache侧信道攻击、 基于page fault的攻击和基于DRAM的攻击等, 与这些攻击对应的组件有: 重排序缓冲区、预留站、退休缓冲区、 分支预测器、TLB、cache、page table和DRAM.

微体系结构组件划分

CPU内部的优化组件、分支预测器、存储结构和操作系统功能组件这4类

那么软件侧信道攻击技术与这4类微体系结构组件之间的关系如下:

瞬态执行攻击依赖CPU内部的优化组件

分支预测攻击利用分支预测器泄露机密信息

TLB侧信道攻击、cache侧信道攻击和基于DRAM的侧信道攻击与存储结构相关

基于page table的侧信道攻击通过操作系统功能组件获取机密信息

组合攻击实质上是物理攻击与软件侧信道攻击相结合形成的攻击手段

侧信道攻击

瞬态执行攻击

现代处理器中微体系结构层面的优化组件(例如, 重排序缓冲区)可以泄露体系结构层面无法访问的信息; 攻击者通过构建数据提取或数据注入两种软件侧信道攻击方法, 将机密信息提取到微体系结构组件中; 最后, 根据不同的微体系结构组件, 构建基于微体系结构的侧信道攻击提取机密信息. 常见的瞬态执行攻击有Meltdown-type的数据提取攻击、Spectre-type的分支诱导攻击以及基于逆向推测性执行(reversely speculative execution)的数据注入攻击.

Meltdown-type攻击利用了处理器乱序执行(out-of-order execution, OoOE)的能力提取体系结构层面无法访问的数据。基于Meltdown-type的数据提取攻击有Foreshadow攻击、ZombieLoad攻击和RIDL攻击, 它们利用处理器在约束条件下(例如, 发生页面错误或微码辅助)会瞬态读取L1D cache或行填充缓冲区(line-fill buffer, LFB)中的旧值(stale value)的特点, 从而提取受害者机密信息。

Spectre-type攻击利用了处理器推测执行(speculation execution)的能力诱导受害者分支偏离正确的执行路径。基于Spectre-type的分支诱导攻击[50−53]包括SgxPectre攻击和SpectreRSB攻击: SgxPectre攻击利用了处理器中分支预测单元在不同安全域上共享的特点, 使得攻击者容易诱导受害者分支的执行路径, 从而导致推测性执行攻击; SpectreRSB则利用返回堆栈缓冲区(return stack buffer, RSB)在不同安全域上共享的特点, 通过不受信任的攻击者操纵RSB使得执行飞地时发生错误推测从而导致推测性执行攻击。

逆向推测性执行攻击将攻击者控制的数据注入到微体系结构数据缓冲区或预测器中进而提取机密信息.基于逆向推测性执行的数据注入攻击有加载值注入(load value injection, LVI)攻击, 它利用处理器在约束条件下(例如, 页面偏移量相同)会导致瞬态转发L1D cache、LFB、存储缓冲区(store buffer, SB)中stale value的特 点, 从而开发了逆向推测性的数据注入攻击.

分支预测攻击

现代计算机按照流水线方式执行指令. 处理器在处理分支指令时, ID阶段才能知道该指令是否为条件分支指令, 待分支指令通过了EX阶段才会把下一条指令送入流水线的IF阶段, 这大大降低了处理器的处理效率. 分支预测是现代处理器在程序分支指令执行前预测其结构的一种机制, 采用分支预测, 处理器会提前预测分支的走向, 并且基于预测结果进行后续的取指和译码工作. 然而, 在上下文切换期间, 分支预测器BPU并不会被处理器刷新. 也就是说, BPU中可能保留有隔离架构的机密信息, 这些信息会被攻击者以软件侧信道方式窃取, 从而导致严重的安全隐患。

在现代处理器中, BPU一般由两部分组成, 分别是BTB和定向分支预测器(directional branch predictor): BTB 预测分支的目标地址, 定向分支预测器预测分支的方向(taken或not taken). BTB和定向分支预测器都能泄露隔离架构的机密信息.

在上下文切换期间, 隔离架构不会刷新分支预测器BPU, 因此BPU中遗留了与受害者相关的机密信息; 攻击者以软件形式将BPU中受害者的分支信息显式地缓存在其他攻击者能够访问的微体系结构组件中; 通过构建基于微体系结构的侧信道攻击提取受害者的分支信息, 将分支信息与受害者源码中的各种分支结构相互对比, 攻击者可以推断出TEE中受害者细粒度的控制流. 常见的分支预测攻击有基于分支目标缓冲区的“Branch Shadowing”攻击和基于定向分支预测器的BranchScope攻击.

TLB侧信道攻击

现代处理器利用转换后备缓冲区 (translation lookaside buffer, TLB)来缓存虚拟地址与物理地址之间的转换关系. 在某些设计中, TLB是竞争性共享的微体系结构资源, 而任何竞争性共享的资源都能产生侧信道.

由于TLB组件能够在攻击者和受害者之间共享, 因此TLB在理论上存在TEE软件侧信道漏洞. 攻击者通过监视隔离架构上下文切换期间TLB条目的变化, 可以推断出受害者访问的TLB条目.

cache侧信道攻击

在现代的CPU架构中, 处理器的处理能力和内存访问之间的速度不匹配, 这个问题严重制约了计算机处理能 力的提高. 缓存的出现就是为了匹配CPU和内存之间的速度问题, 即计算机把处理器最近用过的数据存在 cache中, 当处理器再次访问该数据时可以在cache中直接获取. 基于cache的攻击大都利用了传统cache侧信道 攻击技术, 通过测量受害者的执行时间或监视受害者在执行期间的访问轨迹等方法来获取机密信息

隔离架构中的cache软件侧信道攻击类似于在普通处理器(即, 通用执行环境)中 的cache侧信道攻击, 当受害者执行完毕之后, 会将数据遗留在cache中; 攻击者通过测量系统事件发生的时间 (例如, cache hit/cache miss的时间)或监视受害者在执行期间的访问轨迹等方法来获取隔离架构的机密信息. 常见的cache侧信道攻击有Prime+Count攻击、缓存定时攻击(cache-timing attack)、CacheZoom攻击等.

基于page table的侧信道攻击

当应用程序访问物理内存时, CPU会发出逻辑地址(虚拟地址)交由MMU进行内存寻址, 找到物理内存上的内容. 当要访问的页面不在内存中时, 处理器发生page fault, 由OS负责将缺失的部分装入物理内存. 基于page table的攻击大都针对Intel SGX隔离架构. 在SGX中, 内存管理留给了不可信的OS, OS可以在enclave执行的任 意时刻强制设置飞地页面为不可访问. 此时, enclave对该页面的任何访问都会触发page fault, 攻击者根据发生 page fault的飞地页面可以获取与机密信息有关的enclave控制流和数据访问模式.

攻击者通过操纵受害者的页表条目(page table entry, PTE)的某些标志位可以泄露其控制流和数据访问模式, 这类攻击的应用场景一般是Intel SGX. 首先, 根攻击者操纵受害者飞地的PTE的某些标志位(例如, “present”标志位), 使得受害者飞地再次访问该页时发生page fault; 然后, 受害者飞地执行完后, 攻击者通过是否发生page fault来判断受害者飞地是否访问过上述被操纵的页, 以此推断受害者飞地与机密信息相关的数据流访问模式. 常见的基于page table的攻击有Controlled-Channel攻击、SPM攻击等.

基于DRAM的侧信道攻击

基于DRAM的攻击与DRAM本身的结构有关. DRAM通常由多个channel组成, 一个channel被分为许多 个DIMM, 每个DIMM通常有两个rank, 不同rank上有许多DRAM chip, 每个chip可以分为多个bank, 一个 bank可以看成一个矩阵的形式, 每个bank中都有一个row buffer用来缓存最近访问过的某个row. 其中每个row 通常为8 KB, 可以由两个4 KB的页共享. 同一个bank中的row是否位于row buffer中会给内存访问造成时间差 异, 根据时间差异极容易判断出当前受害者的内存访问情况

DRAM中row buffer的作用类似于cache, 攻击者利用row buffer造成的内存访问的时间差推断受害者的内存访问信息. 在Intel SGX中, 飞地的所有信息被存储在处理器保留内存PRM中的安全页面缓存EPC中, 飞地外部的应用程序无法访问EPC. 因此, 要在隔离架构中构建基于DRAM的侧信道攻击, 攻击者和受害者必须满足共享同一个DRAM row的条件. 常见的基于DRAM的侧信道攻击有cache-DRAM攻击.

组合攻击

除了基于微体系结构的侧信道之外, 研究人员将其他类型的攻击与微体系结构攻击相结合, 构成一种新颖的组合攻击. 这类攻击吸收了微体系结构攻击的优势, 足以攻破当前TEE隔离架构而泄露大量敏感信息. 组合攻击最典型的例子就是将物理攻击与cache侧信道攻击相结合从而破坏了Intel SGX的Membuster攻击.

组合攻击是微体系结构攻击与其他攻击相结合而形成的攻击手段, 例如, 缓存侧信道攻击与总线监听技术相结合. 常见的组合攻击有Membuster攻击.

威胁模型

可信执行环境通过减少可信计算基(trusted computing base, TCB)限制安全敏感的应用程序与恶意应用程序之间的交互, 从而保证计算设备在隔离的可信执行环境中存储和处理机密信息.

TEE中的TCB通常仅包含CPU或少量代码. 在ARM TrustZone中, CPU、可信操作系统和监视器Monitor是可信的组件, 除上述组件之外, 其余组件均被视为受攻击者控制而被排除在TCB之外.

Intel SGX的可信计算基更小, 仅包括CPU, 除CPU之外的其他所有组件都不可信. 尽管通过减小可信执行环境的TCB可以减少TEE中的软件漏洞, 但无法抵御TEE软件侧信道攻击.

当前针对TEE的软件侧信道攻击中, 包含3类不同能力的攻击者, 分别是用户级攻击者、内核级攻击者以及物理攻击者.

用户级攻击者不需要具备任何特权级权限, 仅通过用户层的恶意应用程序就能发起攻击;

内核级攻击者要求获得系统内核层的权限以执行特权攻击;

物理攻击者则需要将攻击设备物理接触目标设备.

用户级攻击者

用户级攻击者通常是一个无特权的应用程序, 它不必具备任何特权级的权限, 通过执行一段恶意代码或执行系统调用就能将受害者机密信息泄露到微体系结构中. 用户级攻击者的一个显 著特点是: 攻击者只需运行非特权代码, 就能破坏TEE中不同特权级和地址空间之间的内存隔离. Foreshadow攻击、ZombieLoad攻击、RIDL攻击和DRAMA攻击都是用户级攻击者.

以Foreshadow攻击为例, 飞地外的恶意应 用程序利用“mprotect”系统调用清除飞地PTE中的当前位, 从而使对该页的任何访问都导致page fault, 操作系统捕获到该page fault之后转向执行异常处理函数, 系统执行异常处理函数的这段时间给攻击者创造了一个乱序执行的窗口.

内核级攻击者

内核级攻击者通常会控制目标设备的特权级软件, 通过调用操作系统提供的特权指令和内核功能对可信应用程序发起攻击. 内核级攻击者的特点是需要控制操作系统内核. 常见的内核级攻击者有SgxPectre攻击、LVI攻击、Branch Shadowing攻击、BranchScope攻击、Prime+Count缓存侧信道攻击、 CacheZoom攻击、Controlled-Channel攻击、SPM攻击等.

以Branch Shadowing攻击为例, 攻击者是恶意的操作系统, 它通过操纵飞地进程的虚拟地址空间, 可以创建与目标飞地中分支指令相冲突的分支影子指令. 在受害者飞地运行期间, 攻击者通过频繁中断目标飞地的执行以运行分支影子代码, 从而推测出受害者内部细粒度的控制流.

物理攻击者

物理攻击者需要攻击设备能够物理探测被攻击设备的硬件, 然后利用收集到的信息推断受害者的机密信息。物理攻击者与上述两类攻击者的不同之处在于: 用户级攻击者和内核级攻击者都是软件攻击, 而物理攻击者需要利用物理器件探测设备的信息. 典型的物理攻击者是Membuster攻击, 它通过收集受害者执行过程中DRAM产生的信号变化, 对Intel SGX的寻址算法进行逆向工程, 再利用cache侧信道攻击获取飞地的细粒度机密信息.

防御

针对TEE软件侧信道攻击的防御措施可以从硬件层面和软件层面两方面考虑. TEE软件侧信道攻击大都利用了微体系结构组件的优化功能, 因此重新设计硬件结构能从根本上解决TEE软件侧信道攻击带来的问题.

然而, 硬件层面的防御措施短期内无法部署到计算设备中, 因此安全研究人员提出了一些软件层面的防御措施, 用于短期内部署到计算设备中来缓解TEE侧信道攻击.

瞬态执行侧信道防御措施

由于瞬态执行攻击滥用了现代处理器中用于提升计算效率的微体系结构组件, 因此软件层面的对策(例如在瞬态执行指令之后插入lfence屏障)或硬件层面的微码更新无法彻底抵御瞬态执行攻击, 硬件层面通过更改处理器硅片结构等措施能从根本上抵御瞬态执行侧信道攻击.

硬件层面

(1) 更新微码: 通过发布微码更新, 可以对具有瞬态执行漏洞的硬件打补丁. 例如, 通过在飞地退出时刷新L1 cache可以抵御Foreshadow攻击、通过刷新行填充缓冲区并在刷新操作完成之后增加一个lfence屏障可以抵御ZombieLoad攻击和RIDL攻击、带有微码补丁的Intel处理器会在进入或恢复飞地时刷新分支目标缓冲区从而抵御SgxPectre攻击.

(2) 硅片级更改: 在硅片级别重新设计处理器以禁止瞬态执行指令进行瞬态计算, 从而使得错误加载不会瞬态转发任何数据. 该方案可以从根本上解决当前处理器中一些优化技术带来的侧信道, 从而保护TEE隔离架构免受瞬态执行的影响. 这是一种长期解决方案, 其特点在于能从根本上解决瞬态执行侧信道, 缺点是短期内无法部署.

(3) 修改分支预测器: SpecCFI通过在BTB条目中增加一个与目标地址相关的CFI (control-flow integrity)标签或划分出一块内存区域充当影子调用堆栈(shadow call stack, SCS), 从而抵御基于BTB和基于RSB的Spectretype攻击.

软件层面

基于编译器的软件防御措施可以缓解LVI攻击. 通过分析飞地源码, 在每条瞬态执行指令之后插入lfence屏障, 可以序列化处理器流水线. 这能确保瞬态执行指令加载的值不是攻击者控制的注入值, 而是体系结构上正确的值.

分支预测侧信道防御措施

分支预测侧信道攻击滥用了现代处理器中的分支预测单元, 硬件层面通过修改BPU结构或更新微码以使安全域上下文切换期间刷新BPU能从根本上抵御此攻击, 而软件层面通过消除受害者源码中的条件分支指令能缓 解此攻击.

硬件层面

(1) 更新微码: 通过更新微码使得受害者飞地在上下文切换期间刷新BPU中与受害者机密信息相关的 分支信息.

(2) 修改BPU结构: 通过修改BPU的结构缓解分支预测攻击可以从两方面考虑: 第一, 对BPU进行分区. 分区之后, 攻击者无法访问与受害者有关的BPU条目, 从而无法探测受害者的分支信息; 第二, 静态预测安全敏感的分支. 将受害者源码中的所有安全敏感的分支标记出来, 这些分支只能被静态预测且每次预测之后不能更新BPU条目, 这样BPU中永远不会出现与安全敏感的分支相关的信息, 从而抵御分支预测侧信道攻击.

软件层面

(1) Zigzagger技术: 利用Zigzagger技术[56]可以缓解Branch Shadowing攻击. Zigzagger技术利用CMOV指令将受害者源码中的条件分支转换为Zigzagger蹦床(trampoline)中的无条件分支, 经过蹦床多次跳转才能到达目标地址. 与条件分支相比, 无条件分支的执行难以被攻击者分辨.

(2) if-conversion技术: 基于编译器的if-conversion技术通过在受害者程序中消除条件分支以抵御分支预测攻击. 与Zigzagger类似, if-conversion也使用CMOV指令将条件分支指令转换为顺序执行的代码, 通过消除条件分支结果对机密信息的依赖性来保护敏感数据. 利用if-conversion删除条件分支指令可以缓解BranchScope攻击.

(3) 禁用性能计数器: 通过禁用高精度的性能计数器等方法可以使攻击者难以准确读取受害者的执行时间, 从而无法判断分支执行的方向.

TLB侧信道防御措施

中国科学院信息工程研究所的研究团队在基于page table的SPM攻击中利用了TLB刷新技术, 在受害者飞地每次内存访问之后利用超线程技术刷新TLB, 从而提高SPM攻击的成功率和准确性. 因此, 硬件层面可以通过重新设计TLB结构抵御此侧信道攻击, 软件层面通过禁用超线程技术可以防止攻击者刷新TLB.

硬件层面

通过更改TLB硬件结构[82]能够抵御大多数TLB侧信道攻击, 例如, 根据不同安全域对TLB进行分区.

软件层面

攻击者利用超线程技术可以监视受害者飞地已访问的TLB条目或通过刷新TLB为其他类型的攻击(SPM攻击)创造条件, 因此可以禁用超线程技术以防止攻击者对TLB进行恶意操作, 从而缓解TLB侧信道漏洞.

cache侧信道防御措施

TEE隔离架构中cache侧信道攻击十分普遍, 也有许多针对该攻击的防御措施, 其中硬件层面的防御措施能从根本上抵御cache侧信道漏洞, 例如分区技术和随机化技术等; 软件层面的对策包括时间差消除技术、隔离技术以及检测技术.

硬件层面

(1) cache分区: 对缓存分区将使得攻击者与受害者无法共享cache行, 从而提供强大的隔离缓存机制来抵抗缓存侧信道攻击, 这类防御措施有STEALTHMEM的cache行锁定技术、基于cache组分区的页面着色技 术 (page coloring)、基于缓存way分区的缓存分配技术 (cache allocation technology, CAT)、Catalyst技术、DAWG (dynamically allocated way guard)技术和缓存分区锁定(partition-locked cache, PLcache)技术等.

(2) 随机化(randomization)技术: 将内存到缓存之间的映射关系随机化可以增加攻击者找到与受害者地址相冲突的cache组的难度, 这类防御措施有随机排列缓存(random-permutation cache, RPcache)技术和ScatterCache技术等.

软件层面

(1) 时间差消除技术: cache侧信道攻击会根据受害者访问内存的时间差异来推断机密信息, 因此可以利用时间差消除技术(例如, 注入噪声)阻止攻击者测量受害者内存访问的时间. 这类防御措施包括噪声注入技术、禁用高精度计时器、恒定时间(constant-time)技术等.

(2) 基于检测的技术: cache侧信道攻击可以导致大量的缓存未命中等系统事件发生, 利用性能计数器检测系统事件(例如, cache hit或cache miss)能够判断cache侧信道攻击是否发生.

(3) 基于隔离的技术: SmokeBomb技术[95]是一种典型的基于隔离的技术, 它利用软件缓存锁定技术将L1缓存作为每个进程的私有空间, 只用于安全敏感的操作, 从而防止攻击者通过测量受害者访问时间获取机密信息.

基于page table的侧信道防御措施

基于page table的侧信道攻击利用页表PTE的标志位泄露受害者的内存访问模式. 硬件层面通过硬件隔离技术抵御此攻击, 软件层面的防御措施主要包括软件隔离技术、检测技术、重写源码以及Heisenberg技术等.

硬件层面

硬件层面的防御措施主要是硬件隔离技术, 硬件隔离技术通过重新设计硬件使得安全敏感的页 面访问模式对恶意的操作系统不可见, 从而抵御基于page table的侧信道攻击. 这类防御措施包括自分页(selfpaging)技术和Sanctum技术。这两种技术都可以为SGX飞地提供独立的page table.

软件层面

(1) 软件隔离技术: 利用编译器技术将所有依赖于机密信息的执行隔离保护, 使得恶意应用程序无法探测受害者飞地的内存访问模式. 这类防御措施主要有T-SGX技术和确定性复用(deterministic multiplexing)技术: T-SGX 技术利用硬件事务内存(transactional memory)隔离保护受害者飞地; 确定性复用技术将依赖于机密信息的代码和数据放在一个代码页中顺序执行, 从而导致攻击者检测到的page fault序列全部相同.

(2) 基于检测的技术: 基于page table的侧信道攻击会出现大量的AEX, 因此可以通过检测AEX发生的频率 来抵御该攻击. 这类防御措施主要有Déjà Vu技术.

(3) 重写源码: 受害者源码中存在依赖于机密信息的内存访问指令, 通过重写可信应用程序代码可以消除或隐藏内存访问模式对敏感数据的依赖性.

(4) Heisenberg技术: Heisenberg技术可以全面抵御基于page table的侧信道攻击, 该技术要求TLB在恢复 飞地执行时预加载目标飞地的页面转换关系, 使得飞地在内存访问时不会出现页表遍历, 从而防止发生page fault 以抵御基于page table的侧信道攻击.

基于DRAM的侧信道防御措施

由于计算机DRAM中的row buffer会对内存访问造成时间差异, 因此只能从硬件层面消除基于DRAM的侧信道漏洞. 软件层面通过检测系统事件或注入噪声等方法可以检测或缓解该攻击.

硬件层面

通过更改DRAM和处理器架构可以从根本上解决基于DRAM的侧信道攻击.

软件层面

(1) 基于检测的技术: 基于DRAM的侧信道攻击会产生大量的缓存未命中, 因此通过性能计数器检测系统事件可以检测该攻击.

(2) 时间差消除技术: 与cache侧信道攻击类似, 基于DRAM的侧信道攻击也需要测量不同内存访问之间的时间差异才能推断受害者的机密信息, 因此, 可以通过禁用高精度的计时器或向攻击过程中注入噪声使测量结果精度下降, 从而缓解该攻击.

组合攻击的防御措施

Membuster攻击是物理攻击与软件侧信道攻击的结合, 因此其防御措施可以从两个方面着手: 一方面通过修改硬件等对策使得物理攻击难以窃取受害者的物理地址, 另一方面利用ORAM技术隐藏受害者的内存访问模式.

硬件层面

硬件层面必须要更改DRAM和CPU架构以实现对数据总线和地址总线的加密.

软件层面

利用ORAM (oblivious RAM)技术来隐藏CPU的实际内存访问模式.