一文说清DC-DC BUCK电路(非常详细)

目录

摘要

BUCK原理

DC-DC芯片框图

自举电容

输出电感

输出电容和纹波

损耗

总结

摘要

DC-DC BUCK,是硬件工程师工作中使用频率非常高的电路,可以这么说,只要板子不是迷你型的,十有八九都有DC-DC。因此,对它的了解与学习是重中之重,也是考验一个硬件工程师对MOS管,电感,电容这些基本元器件的特性与使用方法的掌握程度。

本文将详细对DC-DC BUCK拓扑,进一步到DCDC芯片实际框图的各部分原理与参数选择等进行较为详细的说明,逻辑推论主要以工程推论为主,公式计算为辅,对实践设计有学习意义。

本文主要做知识记录与学习分享,部分图片源于网上。

BUCK原理

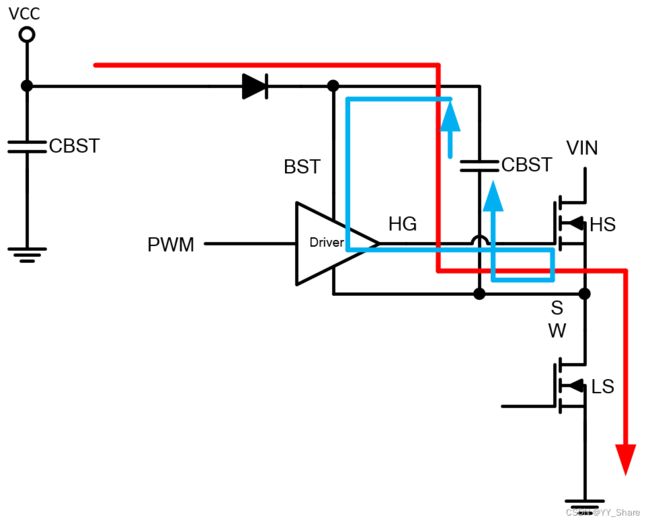

如下图是同步BUCK的拓扑:

1、当Q1导通,Q2关闭,SW端电压为输入电压VIN,VIN给电感L1充电,电感电流增加,VIN=VL+VOUT,此时电感电压左正右负。电流方向为图示蓝色回路。

2、当Q1关闭,Q2打开,由于电感电流不能突变,电流按照下图红线路径形成回路,给负载供电,此时电感电流下降。电感电压左负右正。

根据伏秒法则等推导,同步BUCK得出一个比较重要的公式:

VIN*D=VOUT

简单地说,占空比跟输入输出的电压有直接关系,相对而言,如果输出电压越低,占空比就越低,理解起来就是,因为输出电压低,所以需要打开上MOS管对电感充电的时间就更少了!

(这里要注意,这个只是在完美条件下测出来的理论值,实际会因为有损耗等情况,与理论值有差别)

根据上图拓扑,得出下图波形

a、当Q1打开,Q2关闭,Vsw为高,IQ1增加,IQ2为零,电感电流增加。

b‘、当Q1关闭,Q2打开,Vsw为低,IQ1为零,IQ2减小,电感电流减小。

c、整个稳态过程,电感电流不断增加减少。

d、我们常将上管打开的时间称为Ton,其关闭的时间为Toff。两者相加是一个周期。

这里放一个有意思的仿真波形,绿色为电感左端SW电压信号,红色为输出电压信号。

当没有输出电容,但是有负载的时候,可以看到输出电压的波动随着SW开关的变化,SW为高时,VIN给电感充能,输出电压增加;SW为低时,电感消耗自身能量,输出电压变低。

DC-DC芯片框图

BUCK拓扑图,比较简单,我们结合实际DC-DC芯片框图,进行较为深入的说明。

在DC-DC芯片框图中,还是有那两个MOS管,电感,电容,多了一些 Driver,Controller等逻辑电路。

简单的说,就是利用电感储能,电流不能突变的原理,通过PWM控制 HS Driver和LS Driver进一步控制高边MOS和低边MOS的打开和关闭,调节输出的功能。

按照功能,分为逻辑驱动、功率转换、负载、电压采样和反馈补偿。

自举电容

描述

CBOOT,也叫CBST,中文意思是自举电容。

作用

维持High-side MOS的开启状态。(维持这两个字很关键)

工作过程

1、初始状态,LS导通,HS关闭(HS的 PWM输入为低),SW电压为0V,VCC通过二极管对CBST充电至VCC电压(红色路径)。

2、当PWM为高,HG电压升高过程中,HS开始导通,SW电压上升,由于CBST两端存在压差,会同步抬高BST的电压,而driver内部HG和BST连通,HG电压也会跟随BST升高(蓝色电流路径),从而维持HG-SW的压差足够高,保持HS的导通。

选型

最常见的是0.1uF。

1、自举电容不能太小,至少要保证要大于高边MOS所需的导通能量+漏电流+高边Driver消耗电流+自举电容本身的漏电流。

2、自举电容不能太大,如果太大,在对自举电容充电的时候,该周期内无法对自举电容充满,导致上电压偏小,无法使高边MOS导通,输出异常。

设计角度上,耐压需要超过芯片内部VCC电压即可,为DCDC芯片内部LDO输出电压,常见是3.3V。也有的芯片内部不做LDO,需要外部接入VCC的。

输出电感

DCR,这是电感的直流电阻,这个值越小,在电感上的损耗就越少。但是有的芯片会使用电感的DCR进行电流检测,如果有这个功能,这个值就不是越小越好了。

有意思的是,如果DCR比较大,这部分损耗会以电感温度上升的形式表达,这样又会降低电感的感值,增大纹波电流和纹波电压。

饱和电流,通常指电感量下降百分之30的时候所对应的DC电流。

温升电流,通常指电感升温40度时的电流值。

逻辑上电感有个最小值,要大于一个量才能够包容得了纹波电流。

根据电感的特性,电感越大,储能能力越强,对电流的抑制作用越明显,所以纹波会更小,但是动态响应降低。同时,一般来说,电感越大,尺寸越大,DCR越大,电感的损耗增加。

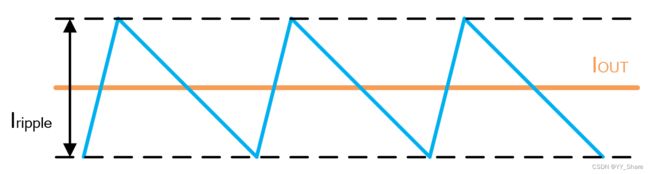

流过电感的电流由交流分量和直流分量组成,交流分量频率跟开关频率一样,会通过电容流入到地,产生响应的输出纹波电压跟ESR相关。

选择电感时要确保饱和电流Isat大于电感电流峰值Ipeak,避免电感饱和,感值下降造成MOS和电感损坏。

其中r是电流纹波率,一般选择0.3~0.5左右。

工作频率

增加频率,会缩短一个周期的时间,纹波电流将减小。

输出电容和纹波

还是这张波形图,没有输出电容,有负载的情况。简单理解,电源纹波产生的根本原因,就是上MOS管开关的过程中,电感电流的波动,进一步导致输出电压的波动。

作用:

储能,滤除电源噪声

选型:

耐压、容值、ESR等参数。

耐压一般需要降额百分之八十;

理论上容值越大,效果越好,但是不同的电容,对于相同频率的阻抗是不一样的,如下图。电容一般选择混搭的方式,即大容值的固态电解电容跟小容值的MLCC组合,以实现全频段都有较低的阻抗。

其他参数相同的情况下,输出电容的ESR越小,输出纹波就越小。从工程应用的角度去理解,就是输出是有纹波电流的,如果ESR越大,在电容这段变化的电压越大,表现出来是纹波的一部分。

前馈电容

前馈电容,为下图中的C7,并联在FB分压电阻的上端。

前馈电容的作用机制,就是利用电容两端电压不能突变的原理,将VOUT的微弱变化及时迅速的反馈到芯片FB引脚,所以其目的是增加芯片的瞬态响应,可以优化纹波。

损耗

开关损耗

开关损耗主要在高边MOS,在开启和关断的过程中,出现电压和电流的交叠区,此时消耗功率:

换句话说就是,MOS管打开是需要时间的,虽然说这个过程对于我们普遍的认知来说很快,但是工程上不能忽略。

开关频率越高,相同时间段内转换的次数就越多,所以开关频率和开关损耗成正比。

而对于下MOS,这个就有点意思了,需要捋一下过程,首先上MOS打开,给电感充能,然后上MOS关闭,进入dead time,此时由下MOS管的体二极管进行续流,dead time时间结束后,下MOS管打开,由于此时下MOS管打开的过程中,VDS电压非常低,可以认为下MOS管的开关损耗非常少。

导通损耗

上下MOS在导通的时候都会存在导通损耗,这个参数跟Rdson有关,因为MOS在导通时不是绝对的零通过电阻,只要有电阻,通过电流,就会有消耗。

这里需要注意,在稳态连续导通模式的时候,电感充电流和放电流的量是一样的,所以上下管的通过电流一样,所以HS和LS导通损耗比跟PWM的占空比有关。如果占空比D为百分之五十,可以认为上下管的导通损耗一样。

但是大部分D都小于百分之五十,所以我们说下管的导通损耗比上管的大。同时,上管主要为开关损耗。

dead time

为了不让上下MOS出现同时导通,将VCC短路到地的情况,两个MOS开关之间存在dead time,下管关闭然后经过dead time的时间,再去打开上管。此时下管的体二极管在dead time时间内续流产生的损耗以及反向恢复时产生的损耗。

体二极管存在导通压降和电流,这部分会产生损耗:

还有反向恢复损耗:

电感损耗

a、线圈损耗

由电感直流电阻DCR产生的,输出电流经过DCR,损耗以热量的形式表达。

线圈损耗可以用如下公式计算:

b、磁芯损耗

磁芯损耗跟磁芯材料相关,很难计算,需要联系电感厂商获取。一般来说,频率越高,磁损越大。

损耗总结

在网上找到一个比较好的图。

开关损耗跟开关频率和栅极电荷Qg有关,而导通损耗跟Rdson有关。

一般来说

High Side MOS 开关损耗大,导通损耗小

Low Side MOS开关损耗小,导通损耗大。

总结

DC-DC BUCK电路,研究透了发现非常有意思,一开始看山是山,然后看山不是山,最后看山又是山,相同的东西,给自己的感觉完全不一样。