VIVADO关于VIO IP核(Virtual Input/Output)的使用

平台:vivado2017.4

最近在验证一个单独的模块时,希望可以在线实时改变内部寄存器的值。经过分析发现,VIVADO的VIO可以完美解决我的这个问题。

下面来看看官方介绍。

VIO它可以实时监控和驱动FPGA内部的信号,输入和输出端口的数量和宽度是可以设置的。因为VIO核心与被监控和驱动的设计是同步的,因此应用于设计的时钟约束也会应用于VIO。

下面我们用VIO来监控模块IIC_JFM24C512的动作。此模块是一个EEPROM控制模块。这里使用VIO来给EEPROM写入数据,和读出数据。

在IP Catalog中搜索VIO。

这里我们分析EEPROM控制模块,我们需要监视的地方就是EEPROM读出的数据,需要控制的是EEPROM读写开始使能,EEPROM读写类型,EEPROM读写字地址,EEPROM需要写入的数据。共计五个端口,输入一个,输出四个。

这里选择输入一个端口,输出四个端口。

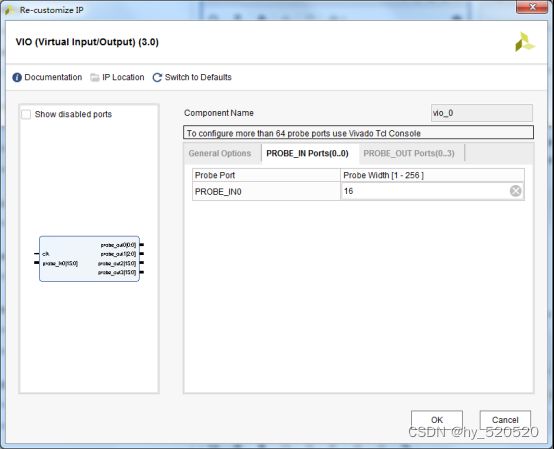

设置输入端口为16位。

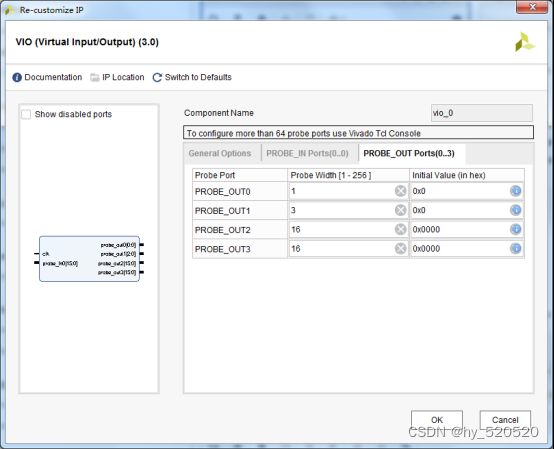

设置输出端口。选择位宽(Probe Width),选择默认值(Initial Value)这里全部设置为零。

在IP source中找到该IP并将代码例化到接口中去。

//------------------------------------------------------------

//------------------------------------------------------------

wire [15:0] iic_wrdat;

wire [15:0] iic_rddat;

wire iic_opt_start;

wire [3:0] iic_opt_type;

wire [15:0] iic_word_addr;

IIC_JFM24C512 u_IIC_JFM24C512(

.iic_word_addr (iic_word_addr ),

.iic_deveice_addr (7'b1010000 ),

.iic_opt_type (iic_opt_type ),

.iic_wrdat (iic_wrdat ),

.iic_rddat (iic_rddat ),

.iic_busy ( ),

.iic_dat (EPM_SDA ),

.iic_clk (EPM_SCL ),

.iic_16byte_en (1'b0 ),

.iic_16wordaddr_en (1'b1 ),

.iic_opt_start (iic_opt_start ),

.rst_n (I_sys_rst_n ),

.clk_ref (I_sys_clk ),

.clk (I_sys_clk ));

//------------------------------------------------------------

//vio

//------------------------------------------------------------

vio_0 your_instance_name (

.clk (I_sys_clk ),// input wire clk

.probe_in0 (iic_rddat ),// input wire [15 : 0] probe_in0

.probe_out0 (iic_opt_start ),// output wire [0 : 0] probe_out0

.probe_out1 (iic_opt_type ),// output wire [2 : 0] probe_out1

.probe_out2 (iic_word_addr ),// output wire [15 : 0] probe_out2

.probe_out3 (iic_wrdat )// output wire [15 : 0] probe_out3

);

//------------------------------------------------------------

//------------------------------------------------------------一般在VIO使用过程中同时可以伴随逻辑分析仪ila一起调试,这里我们在IIC_JFM24C512模块内部例化ILA采集信号。

//----------------------------------------------------------------

//----------------------------------------------------------------

ila_1 u_ila_1 (

.clk(clk), // input wire clk

.probe0(iic_word_addr ), // input wire [15:0] probe0

.probe1(iic_deveice_addr ), // input wire [6:0] probe1

.probe2(iic_opt_type ), // input wire [2:0] probe2

.probe3(iic_wrdat ), // input wire [15:0] probe3

.probe4(iic_rddat ), // input wire [15:0] probe4

.probe5(iic_busy ), // input wire [0:0] probe5

.probe6(iic_dat ), // input wire [0:0] probe6

.probe7(iic_clk ), // input wire [0:0] probe7

.probe8(iic_opt_start ) // input wire [0:0] probe8

);

//----------------------------------------------------------------

//----------------------------------------------------------------好了现在已经将ILA和VIO都添加到模块中区。生成BIT流后下载到板卡,我们上板看看现象。

这是我们添加采集的EEPROM信号。

这是添加的VIO测信号。

下面我们利用VIO向发送读写命令。第一步向地址0写入数据11。

向地址1写入数据22。

向地址2写入数据33。

下面使用读从地址0读出了数据11。