FPGA【紫光语法】

寄存器数据类型:

reg 默认为 1 bit wide,如果超过 1 bit,则需要 range declaration 设置 reg 的位宽

integer 默认位宽为 32 bit,不允许有 range declaration

time 默认位宽为 64 bit,不允许有 range declaration网络类型:

wire signal gate 或 continuous assignment 驱动的 net

tri 多驱动数据类型

tri0 多驱动数据类型,综合时当成 wire 处理

tri1 多驱动数据类型,综合时当成 wire 处理

wand 线与

wor 线或

triand

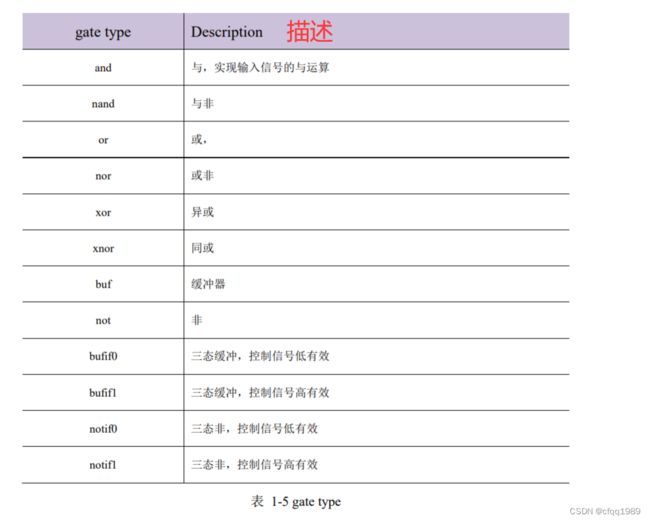

trior 门实例化:

bufif0, bufif1, notif0, notif1, and, nand, or, nor, xor,

xnor, buf, notmodule instantiantion 输入输出:

input, output, inoutparameter 为变量指定常量值

localparam local parameter 参数,不允许值的重写

specparam

genvar generate for 中 index control 的变量always construct, task, functiongenerate/endgenerate

generate if, generate for, generate casecontinuous assignments程序声明:

procedural statements:

Blocking procedural assignments = Nonblocking

procedural assignments <=

begin/end block, if-else-if, case, casex, casez, for,

while, disable, System task($readmemb,

$readmemh)二元运算符:

+, -, *, / 加减乘除

% 取余

** a的b次方【a**b】

<, >, <=, >=, ==, !=

=== 赋值操作

!==

&&, || 逻辑与

&, | 按位与

~| 按位或非

^~, ~^ 按位等价

^ 按位异或

<<, >> 左移

<<<, >>> 算术左移

单目运算符:

+, -, !, &, ~, |, ^, ~&, ~|, ~^

other:

?:, { }, {{ }}编译器指令:

`include, `define, `endif, `ifdef,

`ifndef, `else, `elsif, `undef, `default_nettype