AD9361 介绍 (终)

AD936x 系列快速入口

MGC、Slow AGC、Fast AGC补充: AD9361 补充(上)

通过AD936x Evaluation Software加深了解: AD936x 配置软件介绍 上

文章目录

- 十一、数据接口 LVDS

-

- 11.1 数据路径和时钟信号 LVDS模式

- 11.2 最大时钟速率和信号带宽 LVDS

- 11.3 双端口全双工模式(LVDS)

- 11.4 数据路径时序参数(LVDS)

- 十二、SPI 和 附加接口信号

-

- 12.1 SPI

-

- 12.1.1 SPI_ENB

- 12.1.2 SPI_CLK

- 12.1.3 SPI_DI, SPI_DO和 SPI_DIO

- 12.1.4 SPI数据传输协议

- 12.1.5 单字节数据传输

- 12.1.6 多字节数据传输

- 12.1.7 时序参数

- 12.2 附加接口信号与其他引脚

-

- 12.2.1 附加接口信号

- 12.2.2 其他引脚

十一、数据接口 LVDS

低压差分信号(LVDS)模式下,AD9361数据路径接口使用并行数据总线(P0和P1)在AD9361和BBP之间传输数据样本。总线传输使用简单的硬件握手信令来控制。在LVDS模式下,两条总线(P0和P1)都使用差分LVDS信号。AD9361 LVDS接口便于连接具有LVDS功能的ASIC和FPGA。在噪声环境中,通常使用LVDS接口。

AD9361数据路径,LVDS模式下,数据接口信号如上图所示。

11.1 数据路径和时钟信号 LVDS模式

- DATA_CLK:DATA_CLK是一个差分LVDS信号,AD9361产生,并作为接收数据路径的主时钟提供给BBP。BBP使用该主时钟作为接口数据传输和采样数据基带处理的时序参考。在接收数据期间,DATA_CLK为Rx_D[5:0]信号提供DDR操作的源同步时序。 SDR在LVDS模式下不可用。DATA_CLK的频率取决于系统架构(射频通道数量、过采样程度和带宽模式),通过对AD9361的SPI写来设置。在接口空闲期间,AD9361可以停止DATA_CLK来降低功耗。

- FB_CLK:(BBP驱动 LVDS信号)FB_CLK在发射时为Tx_D[5:0]信号提供DDR操作的源同步时序。BBP可以在接口空闲期间停止FB_CLK来降低功耗。

- Rx_FRAME : (AD9361驱动 LVDS信号) Rx_FRAME高转换时表示帧的开始,可以设置为突发开始时的单个高电平转换,并在整个突发期间保持高电平,也可以设置为在每个帧开始时具有上升沿的脉冲序列(50%占空比)。

- Tx_FRAME: (BBP驱动 LVDS信号)Tx_FRAME高转换表示帧的开始,可以在突发开始时进行单个高电平转换,并在整个突发期间保持高电平,也可以设置在每个帧开始时具有上升沿的脉冲序列(50%占空比)。AD9361一直传输空数据(全零),直到Tx_FRAME开始指示有效数据。

- Rx_D[5:0]: Rx_D[5:0]是一条差分LVDS数据总线,由六个差分对组成。数据以成对数据字的形式在12位数据总线上传输。

- Tx_D[5:0] :Tx_D[5:0]是一条差分LVDS数据总线,由六个差分对组成。数据以成对数据字的形式在12位数据总线上传输。

- ENABLE:ENABLE 由BBP向AD9361驱动,以在TDD模式下提供数据传输突发控制(与TXNRX一起)。BBP置位ENABLE 至少一个DATA_CLK周期,来指示每次突发的开始。再置位最少一个DATA_CLK周期,来指示每次突发的结束。

ENABLE 信号也可以配置为电平模式,在这种模式下,信号的电平(不是脉冲)决定了ENSM何时在状态之间转换。BBP和AD9361分别使用 Rx_FRAME和 Tx_FRAME信号来确定有效数据。

在FDD模式下,ENABLE信号作为单个控制输入来确定ENSM的状态。还有一种独立的 FDD 模式,ENABLE信号可以重新定义为RxON信号,BBP独立控制接收功能,从而节省功耗。 - TXNRX: TXNRX由BBP驱动至AD9361,以在TDD模式下提供数据传输突发控制(和ENABLE一起)。当AD9361将ENABLE信号采样为高电平启动突发脉冲时,TXNRX上的电平也会被采样以确定数据方向。在TDD模式下,TXNRX高电平表示发送突发,TXNRX低电平表示接收突发。TXNRX信号电平必须在整个数据传输突发期间保持不变(有效的逻辑电平)。当ENSM处于ALERT状态时,在TDD模式下,TXNRX上升沿和下降沿直接给相应的合成器上电和断电。

在正常FDD模式下,TXNRX信号被忽略,但必须保持在有效的逻辑电平。独立FDD模式下,TXNRX信号可以重新定义为TxON,BBP独立控制发射功能,从而节省功耗。

11.2 最大时钟速率和信号带宽 LVDS

上表列出的数据比较了LVDS数据总线配置下不同工作模式的最大数据时钟速率和信号带宽。列出了两种情况下的最大射频带宽:使用避免混叠的最小采样速率采样,以及使用2倍过采样采样。在LVDS模式下,最大 DATA_CLK 速率为245.76MHz。该时钟和56 MHz最大模拟滤波器带宽限制了射频通道信号带宽。

UG-570 Rev.0版本 LVDS 模式, 双端口全双工 ,1R1T配置, 最大数据速率(MSPS) 122.88 MSPS

UG-570 Rev.A版本 LVDS 模式, 双端口全双工 ,1R1T配置, 最大数据速率(MSPS) 改为61.44 MSPS

参考ADI论坛回答1,回答2,回答3

该接口可以支持122.88MSPS,但信号路径的其余部分不支持。在Rev.A中修订。

11.3 双端口全双工模式(LVDS)

双端口全双工LVDS模式通过SPI写寄存器来使能。在这种模式下,P0(Tx_D[5:0])和P1(Rx_D[5:0])均为LVDS信号,数据总线(D[11:0])被分成独立的子总线(Rx_D[5:0]和Tx_D[5:0])。每个子总线同时工作,允许BBP和AD9361之间全双工发送和接收数据。

发输数据(Tx_D[5:0])、FB_CLK和Tx_FRAME由BBP驱动,FB_CLK和Tx_D[5:0]、Tx_FRAME之间的建立和保持时间足够以允许AD9361使用FB_CLK捕获Tx_D[5:0]和Tx_FRAME。发送数据采用二进制补码格式,每个数据包中的第一个6位字包含MSB,第二个6位字包含LSB。最大正的采样值为0x7FF,第一个字为0x1F,第二个字为0x3F,最大负值为0x800,第一个字为0x20,第二个字为0x00。Tx_D[5]是每个字的最高有效位,Tx_D[0]是最低有效位。

接收数据(Rx_D[5:0])、DATA_CLK和Rx_FRAME由AD9361驱动,DATA_CLK和Rx_D[5:0]、Rx_FRAME之间的建立和保持时间足够以允许BBP使用DATA_CLK捕获Rx_D[5:0]和Rx_FRAME。接收采样数据采用二进制补码格式,每个数据包中的第一个6位字包含MSB,第二个6位字包含LSB。最大正的采样值为0x7FF,第一个字为0x1F,第二个字为0x3F,最大负的采样值为0x800,第一个字为0x20,第二个字为0x00。Rx_D[5]是每个字中的最高有效位,D[0]是最低有效位。

和CMOS模式中一样,FB_CLK必须从DATA_CLK生成,以便它保持相同的频率和占空比,两个时钟信号之间没有相位关系要求。

I和Q采样数据在每条数据总线上时间交错,对于1R1T系统,I和Q采样以4路交错方式传输:IMSB, QMSB, ILSB, QLSB, …

- 上图中的差分数据用实线和虚线绘制,以说明数据线的差分特性。正支路的实线与差分对的负支路的实线匹配,正支路的虚线与负支路的虚线匹配。

在这种情况下,Tx_FRAME和Rx_FRAME信号与数据切换一致。Tx_FRAME和Rx_FRAME高电平时为IMSB和QMSB,低电平时为ILSB和QLSB。Tx_FRAME和Rx_FRAME随着IMSB再次切换到高电平,指示新帧的开始。

对于2R2T系统,来自射频路径1和2的输入和输出样本以8路交错方式传输:I1 MSB, Q1 MSB, I1 LSB, Q1 LSB, I2 MSB, Q2 MSB, I2 LSB, Q2 LSB, … 在这种情况下,Tx_FRAME和Rx_FRAME信号与数据切换一致。Tx_FRAME和Rx_FRAME高电平时为I1MSB、Q1MSB、I1LSB、Q1LSB,低电平时为I2MSB、Q2MSB、I2LSB和Q2LSB。这些信号通过IAMSB再次切换到高电平,以指示新帧的开始。

- 2R1T和1R2T系统遵循2R2T时序图。

对于2R1T或1R2T配置的系统,时钟频率、总线传输速率和采样周期以及数据捕获时序与2R2T系统的配置相同。但是,在仅使用单个通道的路径中,每个数据组中禁用通道的I-Q数据未被使用。这些未使用的时隙被AD9361忽略。例如,对于使用发射信道1的2R1T系统,发射突发将有四个未使用的时隙:I1 MSB, Q1 MSB, I1 LSB, Q1 LSB, X, X, X, X, …

在这种情况下,Tx_FRAME和Rx_FRAME与数据切换一致,高电平时为I1MSB,Q1MSB,I1LSB,Q1LSB,低电平时为未使用的时隙。这些信号再次以I1MSB切换到高电平,以指示新帧的开始。BBP可以用任意数据值来填充未使用的X时隙。这些值可以是恒定值,也可以重复前面的数据采样值,以降低降低功耗。

LVDS模式不支持以下位:

- Swap Ports—在LVDS模式下,P0是发送端口,P1是接收端口,此配置不能更改。

- Single Port Mode—两个端口在LVDS模式下都启用。

- FDD Full Port—LVDS不支持。

- FDD Alt Word Order——LVDS不支持。

- FDD Swap Bits—LVDS不支持。

11.4 数据路径时序参数(LVDS)

- Tcp: DATA_CLK时钟周期,其最大245.76MHz

- Tmp:DATA_CLK和FB_CLK高和/或低电平的最小脉冲宽度(包括占空比失真、周期抖动、周期抖动和半周期抖动的影响)

- Tstx: Tx_FRAME对FB_CLK下降沿的建立时间

- Thtx:Tx_FRAME对FB_CLK下降沿的保持时间

- Tddrx:从DATA_CLK到 Rx_D[5:0]输出的延迟

- Tddrv:从DATA_CLK到 Rx_FRAME的延迟

LVDS模式接收路径数据端口时序参数图:

LVDS模式发送路径数据端口时序参数图:

TDD LVDS:TDD LVDS的时序表和FDD LVDS 的时序表是一样的。 对于TDD LVDS模式,P0是 TX,P1是RX,不能交换/多路复用。参考ADI论坛

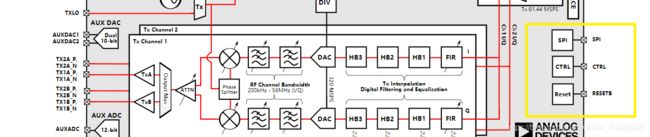

十二、SPI 和 附加接口信号

SPI总线为AD9361的所有数字控制提供了机制。每个SPI寄存器的位宽为8,每个寄存器都包含控制位、状态监测 或 控制器件所有功能的其他设置。

12.1 SPI

可以通过设置SPI配置寄存器中的位来配置SPI总线。这个寄存器是对称的,D6相当于D1,D5相当于D2 (D4和D3未使用)。该器件上电时在默认模式(MSB优先)。对称位被“或”在一起,因此设置一个位会同时设置两个位。当D5和D2清零时,位序为MSB优先,而当这些位被置位时,位序被交换为LSB优先。正确配置后,所有后续寄存器写操作必须遵循所选的格式。

- D6 和 D1—3-Wire SPI :清零时,SPI_DI引脚为输入引脚。置位时,SPI_DI为双向,SPI_DO为高阻态。默认情况下,总线配置为4线接口。如果设置了位D6和位D1,SPI总线配置为三线式接口。

- D5 和 D2—LSB First: 清零时,SPI使用MSB优先格式。置位时,SPI采用LSB优先格式。

- D7 和 D0: 置位时,将所有寄存器异步复位为默认值,在更改其他寄存器之前,必须清除这些位。

12.1.1 SPI_ENB

SPI_ENB是从BBP驱动到AD9361的总线使能信号。SPI_ENB在第一个SPI_CLK上升沿之前被拉低,通常在最后一个SPI_CLK下降沿之后再次被拉高,当SPI_ENB为高电平时,AD9361忽略时钟和数据信号,如果AD9361是SPI总线上唯一的设备,SPI_ENB可以拉低.

当SPI_ENB输入高电平时,SPI_DO和SPI_DI引脚转换为高阻态。在任意通信周期内该信号被驱动为高电平,则该通信周期暂停,直到SPI_ENB被重新驱动为低电平。

12.1.2 SPI_CLK

SPI_CLK是由BBP驱动的AD9361接口参考时钟。它仅在SPI_ENB为低电平时有效。SPI_CLK最大频率为50 MHz。

12.1.3 SPI_DI, SPI_DO和 SPI_DIO

当配置为4线总线时,SPI利用两个数据信号:SPI_DI和SPI_DO。在该配置中,SPI_DI是从BBP驱动到AD9361的数据输入线,SPI_DO是从AD9361到BBP的数据输出线。当配置为三线式总线时,SP_DI用作双向数据信号,既接收串行数据又发送串行数据。在三线配置中,该信号可被称为SP_DIO来做区分。

由BBP和AD9361在SPI_CLK的上升沿发送数据,并在SPI_CLK的下降沿采样。SPI_DI(或SPI_DIO)将控制字段和写入数据字段从BBP传送到AD9361,SPI_DO(或SPI_DIO)将读取数据字段从AD9361返回到BBP。

12.1.4 SPI数据传输协议

AD9361 SPI是一种灵活的串行同步通信总线,支持与许多标准微控制器和微处理器无缝连接。AD9361的控制字段宽度为16位,允许多字节 IO 操作。AD9361不能控制总线上的其他设备,它只能作为从机工作。

通信周期分为两个阶段。第一阶段是控制周期,即向AD9361写入一个控制字。控制字在第二阶段向AD9361串行端口控制器提供有关数据字段传输周期的信息。阶段1控制字段表明即将到来的数据传输是读还是写,还表明了被访问的寄存器地址。

第一阶段16位控制字段包含以下信息:

- W/Rb—Bit 15:指令字的第15位决定了在指令字节写入后是进行读数据传输还是写数据传输。逻辑高表示写操作;逻辑零表示读操作。

- NB2, NB1, NB0—Bits [14:12]:位[14:12]指定在第2阶段IO 操作时传输的字节数

- [D11:D10]—Bits[11:10] :位[11:10]未使用

- [D9:D0]—Bits[9:0]:位[9:0]指定第2阶段期间 IO操作数据传输的起始字节地址(如 0x3DF)。所有字节地址,包括起始地址和内部生成的地址,都被认为是有效的。也就是说,如果一个无效的地址(未定义寄存器)被访问, IO操作继续进行,就好像地址空间是有效的一样。对于写操作,写入的位被丢弃,读操作在输出端得到逻辑0。

12.1.5 单字节数据传输

当NB2、NB1和NB0都为零时,选择单字节数据传输。在这种情况下,地址位后面的八位包含要写入或读取AD9361寄存器的数据。一旦传输完最后一位,数据信号返回空闲状态,SPI_ENB信号变为高电平,结束通信会话。

SPI 单寄存器写操作,值0x55写入寄存器0x15A,三线式总线时,SPI_DO线将被取消

SPI 单寄存器读操作,读取寄存器0x15A,器件返回的值为0x55,三线式总线时,SPI_DI和SPI_DO线将在SPI_DI线上组合

12.1.6 多字节数据传输

在许多情况下,需要多位或多字节协同工作以实现特定功能(如配置AGC和配置数字接口)。

当NB2、NB1和NB0都不为零时,选择多字节数据传输。在这种模式下,要传输的数据的格式和顺序取决于器件是配置为LSB优先还是MSB优先。

对于LSB模式下的多字节数据传输,用户将寄存器地址(最低有效字节)写入到指令字节。SPI内部字节地址发生器在多字节通信时进行递增得到所需的字节。数据按照从低到高的顺序写入,因为字节地址是按照从低到高的顺序生成的。

- LSB优先多字节传输: 要完成4字节写操作,从寄存器0x02A开始,采用LSB优先格式,应用指令字0101 0100 0000_110_1(二进制)。该指令指示AD9361 SPI控制器执行4个字节的写传输,起始字节地址为0x02A。写入第一个数据字节后,内部字节地址生成逻辑递增至0x02B,写入第二个字节后,内部字节地址生成逻辑递增至0x02C,写入第三个字节后,内部字节地址生成逻辑递增至0x02D,写入第四个字节后, IO 通信周期结束,继续下一个指令字。如果不再需要通信,数据信号将返回空闲状态,SPI_CLK变为低电平,SPI_ENB信号变为高电平,结束通信会话。

对于MSB模式下的多字节数据传输,用户将寄存器地址(最高有效字节)写入到指令字节。SPI内部字节地址发生器在多字节通信时进行递减得到所需的字节。数据按照最高到最低的顺序写入,因为字节地址是按照最高到最低的顺序生成的。

- MSB优先多字节传输: 要完成4字节写入,从寄存器0x02A开始,采用MSB优先格式,应用指令字1_011_000000101010(二进制)。该指令指示AD9361 SPI控制器执行4个字节的写传输,起始字节地址为0x02A。写入第一个数据字节后,内部字节地址生成逻辑递减至0x029,写入第二个字节后,内部字节地址生成逻辑递减至0x028,写入第三个字节后,内部字节地址生成逻辑递减至0x027,写入第四个字节后,IO通信周期结束,继续下一个指令字。如果不再需要通信,数据信号将返回空闲状态,SPI_CLK变为低电平,SPI_ENB信号变为高电平,结束通信会话。

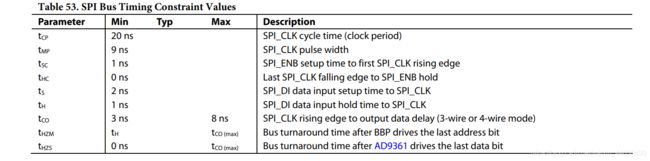

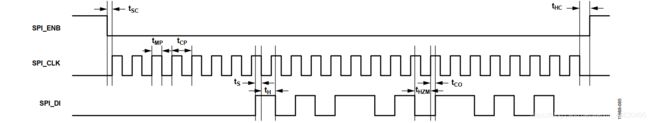

12.1.7 时序参数

- Tcp : SPI_CLK时钟周期

- Tmp : SPI_CLK脉冲宽度

- Tsc : SPI_ENB对第一个SPI_CLK上升沿的建立时间

- Thc : SPI_ENB对最后一个SPI_CLK下降沿的保持时间

- Ts : SPI_DI数据输入对SPI_CLK的建立时间(在12.1.3 下降沿采样)

- Th : SPI_DI数据输入对SPI_CLK的保持时间(在12.1.3 下降沿采样)

- Tco : SPI_CLK上升沿至输出数据延迟(三线或四线模式)

- Thzm : BBP驱动最后一个地址位后的总线周转时间

- Thzs : AD9361驱动最后一个数据位后的总线周转时间

这些参数之间的关系如下图所示,该图显示了标有这些参数的三线式SPI总线读时序图。

12.2 附加接口信号与其他引脚

12.2.1 附加接口信号

- CLOCK_OUT:CLOCK_OUT是一个输出信号,用作BBP的主时钟源。该时钟可配置为外部输入时钟DCXO的缓冲版本或接收数据路径ADC时钟的分频版。频率必须始终小于61.44 MHz。

- CTRL_IN[3:0]: CTRL_IN引脚是四位可编程输入信号,用于手动RX增益和TX衰减控制。

- CTRL_OUT[7:0] : CTRL_OUT引脚是用于实时处理的八位可编程数字输出信号。这些输出包括内部生成的功能和状态位,如锁相环锁定、校准完成和自动增益控制功能。

- EN_AGC :用于自动增益控制(AGC)的手动控制输入。当拉高时,EN_AGC引脚强制AGC解锁,以便对增益设置进行调整。如果未使用EN_AGC引脚,Gain Lock Delay 位必须设为高电平。

- GPO[3:0]: GPO引脚是数字输出,可以配置为监测ENSM状态或用作通用逻辑输出。

- RESETB:RESETB是允许AD9361异步硬件复位的输入信号。逻辑低电平复位器件(所有SPI寄存器复位至默认设置,器件置于 SLEEP 模式)。

- SYNC_IN : 用于同步多个AD9361器件之间数字时钟的输入。若未使用此引脚,则将其接地。

12.2.2 其他引脚

- VDD_INTERFACE:数字I/O引脚, 1.2 V至2.5 V电源(LVDS模式下为1.8 V至2.5 V)。

- TX_MON:发射通道功率监控输入

- TX_LO:外部发射LO输入

- RX_LO:外部接收LO输入

有不对的地方,欢迎大家在评论区指正,非常感谢!