AD936x 配置软件介绍 上(AD936x Evaluation Software)

AD936x 系列快速入口

AD936x 配置软件介绍 中

MGC、Slow AGC、Fast AGC补充: AD9361 补充(上)

文章目录

- 参考资料

- 一、整体介绍

-

- 1.1 Setup

-

- 1.1.1 Project Wizard

- 1.1.2 Load/Save Project

- 1.1.3 Individual Wizard

- 1.1.4 Create Init Script

- 1.2 Receive

- 1.3 Transmit

- 1.4 TX/ALERT/RX

- 1.5 Advanced

-

- 1.5.1 MANUAL CONTROL

- 1.5.2 SCRIPTING

- 二、使用介绍

-

- 2.1 点击Run Project Wizard

- 2.2 RF Wizard

- 2.3 时钟与PLL

- 2.4 采样率与带宽

- 2.5 滤波器

-

- 2.5.1 未勾选Use Custom RxFIR coeffcients file

- 2.5.2 勾选Use Custom RxFIR coeffcients file

- 2.6 数据接口

-

- 软件后续配置在 [AD936x 配置软件介绍 中](https://blog.csdn.net/weixin_44630490/article/details/115404240)

参考资料

- AD936x Evaluation Software V2.1.3 提取码:zwdx

- AD9361 Customer Software Quick Start Guide (见该软件中Documents)

- AD9361 Script Commands(见该软件中Documents)

目的:之前对AD9361有了整体初步认识,通过该软件加深对AD9361的了解,生成配置脚本

一、整体介绍

1.1 Setup

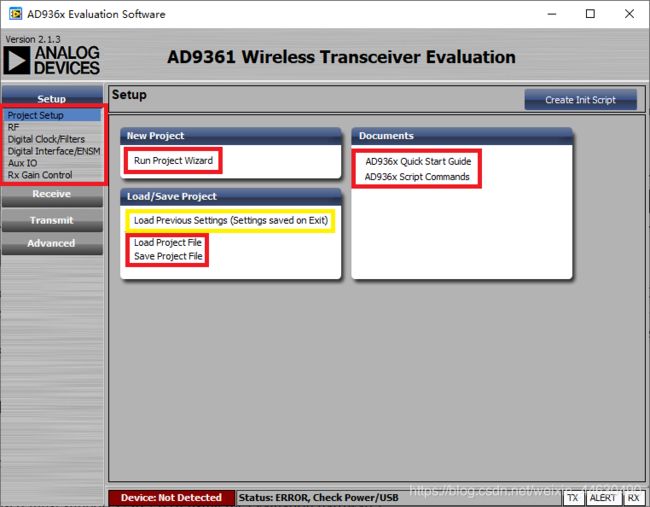

1.1.1 Project Wizard

Run Project Wizard 在AD9361客户软件的 Project Setup 项中,通过一系列的设置向导,可为特定应用配置。Project Wizard涵盖了AD9361设置的主要方面,可以确保软件覆盖AD9361的所有主要设置,包括双工类型(TDD、FDD)、带宽、增益控制、数字滤波器设置等。同时也可以运行一个或多个独立向导来更改单个区域中的配置(例如Aux I/O)。一些向导(如Aux I/O、Rx Gain Control)用于辅助功能,只能通过手动启动该独立向导来访问。

运行Project Wizard后,可以创建初始化脚本和/或用向导中配置的设置对AD9361进行编程(如果连接了硬件)。当前配置可以保存为用户自定义的项目,如上图中Load Project File和Save Project File。

1.1.2 Load/Save Project

- Load Previous Setting

每次软件退出时,软件都会保存当前的所有设置,单击“Load Previous Settings”可以恢复软件退出时保存的配置。 - Load and Save Project File

运行一次 project wizard 后,可以通过单击“Save Project File”将所有可配置设置保存为用户自定义的项目文件。之后单击“Load Project File”将特定的项目文件加载回来。

1.1.3 Individual Wizard

在软件左上角的“Setup”按钮中,可以单独设置AD9361的特定功能。点击其中一个按钮(如“RF”)会运行一个向导,并显示与该功能相关的当前寄存器设置。

1.1.4 Create Init Script

通过Run Project Wizard或Load Project File配置好设置后,按“Create Init Script”按钮会生成一个初始化脚本。脚本可以是 low level—所有寄存器写都显示为SPI写,或者脚本可以是high level—其中一些功能(如设置载波频率)通过它们的功能名称来显示。该脚本可以加载回软件。

1.2 Receive

如果评估硬件已连接,在Project Wizard运行一次/或Load Project File之后,点击“Receive”按钮将打开一个页面,允许将AD9361配置为接收状态,并将接收到的数据传递给软件显示。

1.3 Transmit

如果评估硬件已连接,在Project Wizard运行一次/或Load Project File之后,点击“Transmit”按钮将打开一个页面,允许AD9361传输I/Q 数据文件。

点击“Program Device”来初始化评估硬件,如果设备尚未被编程或参数发生变化,按钮为黄色,需要对AD9361重新编程。初始化AD9361后,按下“Enable FPGA PG Move to Tx State”将AD9361转移到发射状态,开始将“Tx1”和“Tx2”文件中的I/Q数据发送到AD9361。

1.4 TX/ALERT/RX

如果连接了硬件,窗口右下角的框显示AD9361的状态。当设备已被编程并处于ALERT状态,“ALERT”框将改变颜色。如果AD9361进入 TX或 RX, TX 、RX也会改变颜色。点击其中一个框将迫使AD9361进入这个状态。

1.5 Advanced

高级页面允许访问单个寄存器,并允许独立于或附加于上述“Receive”和“Transmit”功能运行用户创建的脚本。

1.5.1 MANUAL CONTROL

该页允许对AD9361硬件的特定寄存器进行SPI访问。AD9361地址空间为10位宽(D9:D0)。然而,要访问AD9361本身,位D12也必须置1。例如,要写入AD9361地址5,在“SPI Address”框中输入的值应为“1005”

当位D12未设置为高电平时,写操作直接发生在主板上的FPGA中。写入FPGA寄存器F(h)会影响AD9361 ENABLE和TXNRX引脚的逻辑电平,从而影响AD9361状态机的状态。

按下“Register Dump”按钮,在屏幕表格中显示AD9361寄存器值,并允许将它们转储到文件中。

1.5.2 SCRIPTING

可以从该页面清除、加载、保存和运行自定义脚本。任何通过“Create Init Script”创建的脚本都可以加载到此页面中。

二、使用介绍

2.1 点击Run Project Wizard

2.2 RF Wizard

- Device : 设备型号 根据自己设备选型

- Device Rev : 设备版本 默认 R2

- Project Profile : 配置文件 可以自定义或者从常用的模板选取

- Rx Channel : 接收通道 可以选通道1或2或同时选两个接收通道,也可都不选取

- Tx Channel : 发送通道 可以选通道1或2或同时选两个发送通道,也可都不选取

- Rx Input Structure : 接收通道模拟端接口为差分还是单端 详见AD9361 介绍(上) 第三部分接收链中 RxA RxB RxC,为实现最佳噪声系数,建议差分模式

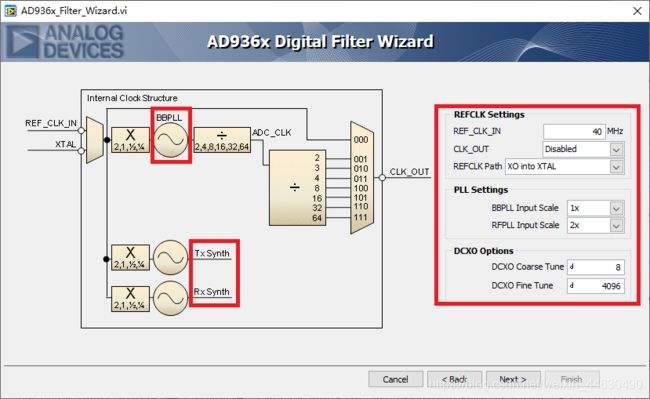

2.3 时钟与PLL

REF_CLK_IN、REFCLK Path、PLL Settings、DCXO讲解详见 AD9361 介绍 (中) 第七部分,我用的是AD-FMCOMMS3,从原理图可知参考频率 REF_CLK与40MHz晶振连接。CLK_OUT详见 AD9361 介绍 (终) 12.2 部分,未用到,Disabled。

由于BBPLL 参考时钟频率最好在35-70MHz中选大的值,RF PLL 参考时钟频率最好在10-80MHz中选大的值,所以BBPLL和RFPLL 分别为1x和2x。

- REF_CLK_IN : 40MHz

- REFCLK Path :XO into XTAL

- BBPLL Input Scale :1x

- RFPLL Input Scale :2x

- CLK_OUT :Disabled

- DCXO Options:如果参考时钟是外部输入时钟,忽略该项。如果参考时钟为DCXO,由于DCXO可以通过coarse word和 fine word,调整产生的DCXO频率,需要根据设备实际情况设置该项,目前先使用默认值。

2.4 采样率与带宽

接收通道和发送通道中滤波器的插值与抽取、Tx/Rx FIR数字滤波器讲解详见 AD9361 介绍 (上) 第五部分,采用Custom自定义时,输入采样率,确定内插和抽取系数后(如果需要的话),会反推出BBPLL频率和BBPLL分频系数(现在不可直接设置)。

- Standard :可以选择Custom自定义设置,也可以选用常用的通信协议模板

- Tx/Rx Sampling Rate : 发射/接收采样频率,当不勾选Rx Rate = 2*Tx Rate时,接收采样速率等于发射采样速率

- Tx/Rx RF Bandwidth :发射/接收射频带宽

- TFIR/RFIR :FIR数字滤波器,勾选Bypass时,可以把FIR数字滤波器旁路掉。我们后续会采用MATLAB设计FIR数字滤波器系数,去除带外干扰,不勾选。

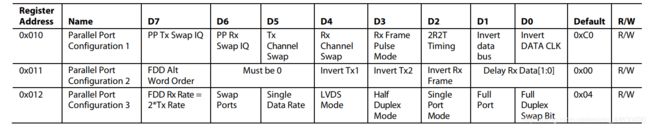

- FDD_Special Rate :由并行端口配置寄存器(地址0x012)可知,D7(FDD Rx Rate = 2*Tx Rate )位清零时,接收采样速率等于发射采样速率。置位时,接收速率是发送速率的两倍。只有当寄存器0x012的位D3清零时(全双工模式),D7位才能置1。我们采用默认状态不勾选。

如下图,勾选最上方后可以设置BBPLL频率、BBPLL和ADC_CLK的分频系数、全部内插和抽取系数,可以推出采样率(采样率灰色,不可设置),推出的采样率需要满足Rx Rate = Tx Rate或Rx Rate = 2*Tx Rate。

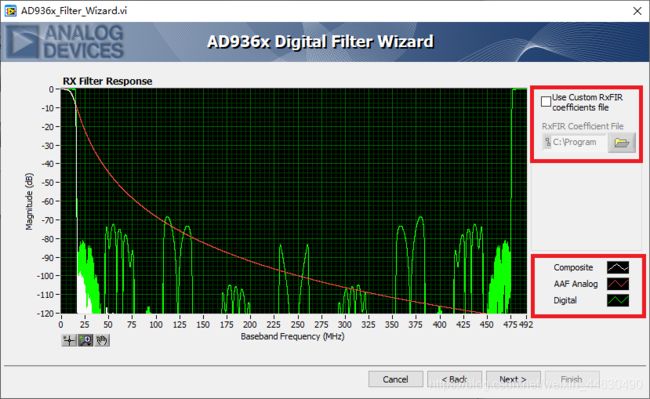

2.5 滤波器

2.5.1 未勾选Use Custom RxFIR coeffcients file

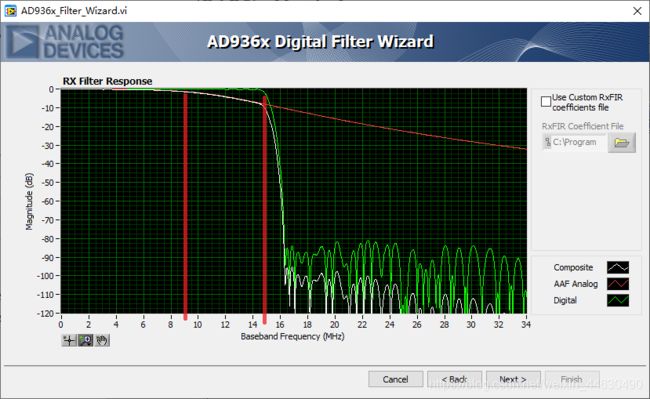

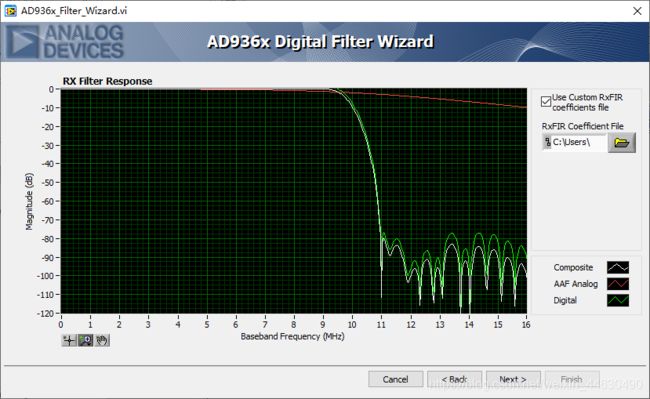

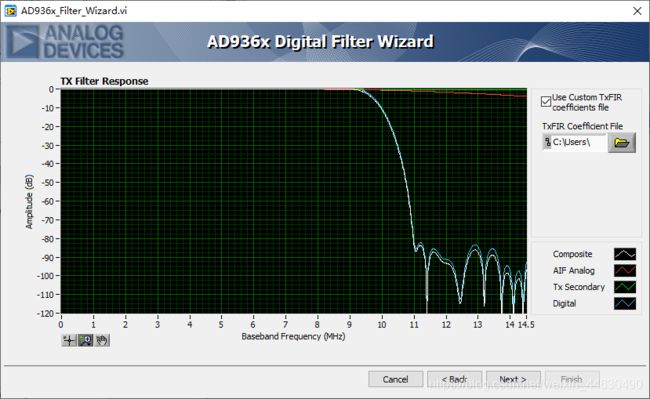

下图中绿线为FIR数字滤波器响应,是软件依据之前设定的采样速率Rx/Tx Sampling Rate自动生成的全通滤波器。红线为模拟防混淆滤波器响应,其3dB角频率和之前设置的带宽RF Bandwidth有关,白线是模拟滤波器和数字滤波器级联后的响应曲线。

下图参数Rx/Tx Sampling Rate:30.72MHz ,RF Bandwidth :18 MHz

局部放大后滤波器响应如下

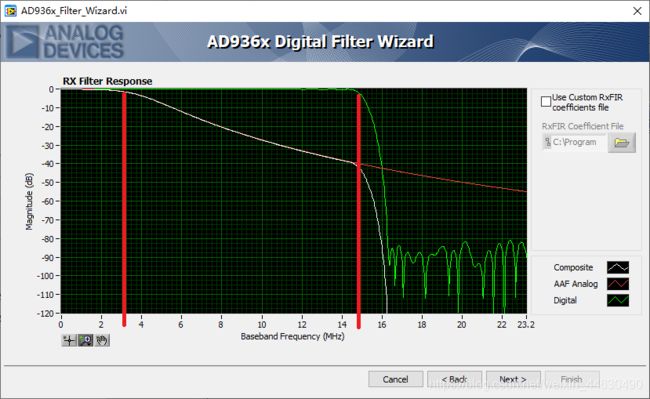

下图参数Rx/Tx Sampling Rate:30.72MHz ,RF Bandwidth :6 MHz

Rx/Tx Sampling Rate:30.72MHz ,RF Bandwidth :6 MHz。局部放大后滤波器响应如下

2.5.2 勾选Use Custom RxFIR coeffcients file

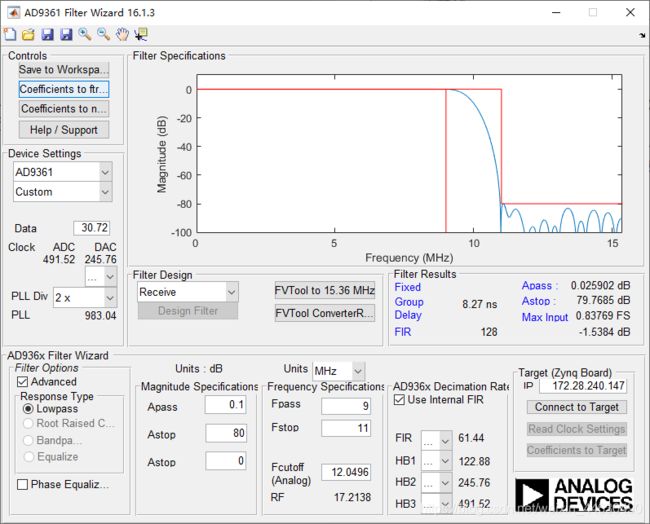

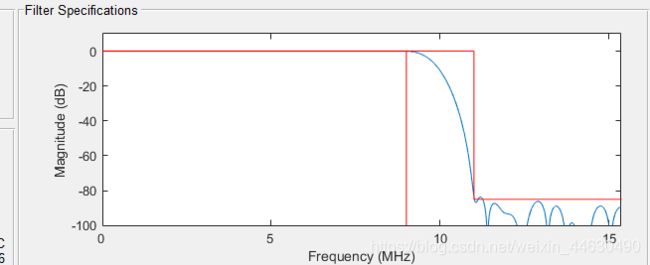

这种情况下,FIR数字滤波器的系数可以根据通信需求利用matlab来得到,详见MATLAB设计AD9361 FIR滤波器。下图分别为MATLAB生成的接收和发送FIR滤波器。

MATLAB生成的发送滤波器频率响应

将生成的fir文件导入,局部放大,可见和MATLAB 窗口预览的滤波器响应形状一致。

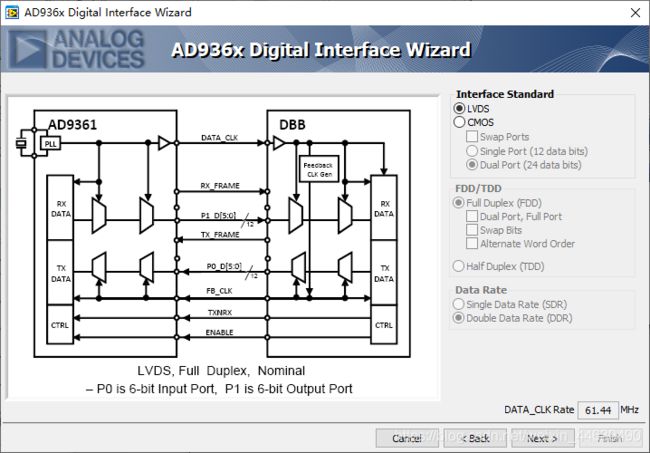

2.6 数据接口

数据接口CMOS模式详见AD9361 介绍 (下) 第十部分,数据接口LVDS模式详见 AD9361介绍 (终) 第十一部分,可根据实际器级选用(推荐LVDS模式),由于后续使用Zynq 系列 中的zc706有LVDS接口,我们采用LVDS模式。

软件后续配置在 AD936x 配置软件介绍 中

有不对的地方,欢迎大家在评论区指正,非常感谢٩(*´◒`*)۶!