硬件开发流程

前言:

研发流程在一个有一定规模的企业中起到了非常重要的作用,也是一个产品或者项目成功量产出货依赖的平台体系,作为工程师如果想要走的更远,就必须了解流程体系,了解如何对产品的开发质量进行更好的管控。

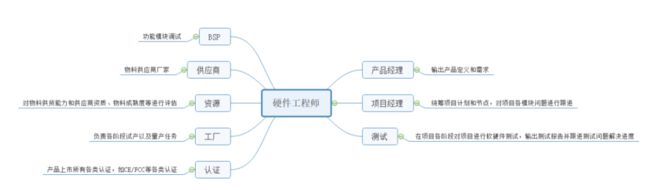

作为一个合格的硬件工程师必须有着一个管理者的素质和担当,与程序员不同,软件工程师通常面对的工作对象是代码,而硬件工程师除了面向电路之外,更多的是接触其他部门的人以及电路之外的事物,甚至很多企业以外的机构,比如工厂、供应商、营销、认证机构,这些对硬件工程师的综合素养有着极高的要求,也是对硬件工程师协调能力的一个考验。

如上图1-1所示,基本涉及到硬件工程师打交道的各个模块,在一款硬件产品的全流程中,硬件工程师始终担当核心角色,将这些不同模块的人员连接起来,同时也是硬件产品开发过程中流程管控的枢纽,对项目的成败起到了决定性的作用。作为核心,工程师就需要详细的了解项目开发的流程,根据流程办事,才能保证项目的状态是可控的。

此外,在硬件产品的实际开发流程中,基本遵循IPD产品开发流程,即集成产品开发,集成产品开发的全流程如图1-2所示,硬件通常会参与从计划到生命周期的整个阶段,我们将会依据这五个阶段去介绍硬件项目的开发流程。

图1-2 IPD产品开发流程

一、硬件SPT阶段

此阶段处于IPD的概念阶段和计划阶段,概念阶段是指基于市场的需求或者公司的产品规划,将接收到的输入需求转化成产品的概念,从产品经理的角度,在这个阶段会形成产品的基本概念,达成想要做成什么样的产品,用什么资源去做,花费多少成本,期望达成什么样的市场效果。在这个阶段硬件团队就需要深度介入,对此阶段产生的需求进行技术可行性进行评估,不合理的需求、不具有可行性的需求需要及时沟通,避免在正式输出产品定义时仍然有争议内容。具有挑战性的需求要及时拉通公司内部涉及模块进行技术攻关、技术预研,并对预期节点是否能够达成目标进行评估。总结汇总如下:

1、不合理需求的技术可行性评估

2、挑战性需求的开发计划

当产品进入计划阶段,项目经理将会介入进行评估产品的详细计划,包括时间计划、成本计划、执行的工作分解的具体计划,对硬件、软件、结构等部分的任务进行分解。此时硬件(某些公司有硬件PM职位)需要根据PM敲定的大的项目主计划制定硬件子计划。

二、需求评估

产品硬件项目的开发,首先要明确硬件总体需求情况,比如CPU的处理能力、存储容量以及速度,IO端口的分配、接口需求、电平需求、特殊电路等。

对于手机领域,对于硬件需求的评估我们可以更具体一些,如下图1-3所示(简单的示意,实际产品定义比较复杂)

图1-3

从硬件维度进行评估,分为如下:

1、平台

使用的平台是否满足算力要求,是否支持产品camera和LCD所需要的分辨率,支持的内存大小,平台需要的主板层阶数,是否支持产品所需要的接口协议(USB3.0、C-PHY、BC1.2)等。大概梳理如下:

(1)算力是否满足项目需求(包括CPU、GPU、ISP、NPU等)

(2)接口是否满足外设需求

比如是否支持USB2.0、Type-C接口、MIPI接口、外设的SPI接口需求等

(3)是否支持产品定义所需求的DDR内存

(4)是否支持LCD、camera的分辨率要求

2、硬件整体系统的基本功能和性能指标

根据产品规划整体系统的基本功能,以及产品的性能指标。典型的,比如产品规划销售区域为亚太区域,那么需要硬件评估需要支持亚太区域的具体频段和射频架构,以及根据产品定位需要做到的具体性能指标。

3、关键器件选型

需要根据产品的需求对关键器件进行选型,从物料的成熟度和成本两个角度去考量,同步拉通采购对关键器件进行评审。

4、成本

评审当前敲定的方案是否满足项目的成本目标,如果没有满足目标,是否需要制定降本方案。

5、关键技术攻关

如果产品涉及到新技术、新物料、新方案,那么需要拉通相关领域的专家,进行评审以及风险评估,如果风险评估比较大的新东西,就需要提前跟项目组或者老板沟通,是否需要做预研等工作,极大风险的甚至需要评估是否砍掉需求,硬着头皮做下去只会将项目做砸。

三、原理图设计

此阶段已经进入产品开发阶段:

在原理图设计阶段,消费电子类产品基本都会参考平台提供的参考原理图设计,但是我们在实际绘制的时候并不是照抄就行了,要基于平台的参考设计对参考设计做必须的裁剪,这样要求硬件工程师对平台的基本特定一定要有相当的了解。

原理图设计阶段注意下面的几个问题:

1、基于平台特性,对参考设计进行裁剪

平台接口配置是否满足当前项目需求——比如MIPI的Lane数配置是否符合选型模组的要求、参考设计sensor的INT信号默认PD是否符合当前选型的设计等

这块的工作将是原理图设计阶段的重点工作之一。

2、基于产品需要,绘制外设部分的原理图

此部分尽量参考成熟电路设计,避免自由发挥,部分模块可能有第一资源和第二资源的需求,需要做好兼容电路的设计。

3、检查电源树的设计是否合理?能否满足效率要求和负载要求?

电源模块是整个硬件系统的核心,验证影响到整机系统的可靠性,需要仔细核查电源树的设计,对于和参考设计差异的部分需要和平台厂商或者供应商的FAE及时拉通确认。

4、GPIO口的配置是否合理?重点检查GPIO口的初始化配置。

5、模块电路的归一化设计

比如sensor、充电等模块电路是否参考历史项目设计,满足CBB要求。

6、新器件的封装设计和检查

在实际项目中,可能会导入新器件的原理图和PCB封装,在新建封装时必须仔细检查封装的准确性,在实际项目中,因为封装出错导致下项目出现重大问题的案例也是很常见的。

7、新方案电路的check

有的时候新方案、新导入的IC并非直接参考SPEC上的典型电路就可以保证没有风险,最好拉通供应商排查芯片、方案的历史问题和友商出现过的问题,做好兼容风险,保证回板后预留的措施可以应对可能出现的风险问题。

8、关键器件评审

在进行原理图绘制的时候,就需要同步开始关键器件的评审,主要从关键物料的性能、成熟度、风险、价格、交付能力这几个维度考量。

在这个阶段硬件工程师需要作为主导的角色参考,及时拉通各模块(SQA、结构等)及时将关键器件确定下来,避免后期频繁进行关键器件变更,导致堆叠、走线也会受到影响。

9、成本

在原理图设计阶段进行的差不多的时候,需要输出一版基本完整的BOM给到采购进行核价,并和历史项目以及友商进行对比,以及是否符合SPT阶段的预估成本,对于成本偏差较大的设计,需要及时找到原因并给出降本方案。

四、堆叠设计阶段

堆叠设计阶段开始的前置条件有2个:

1、原理图方案确定

原理图的变更对堆叠将会有比较大的影响,在原理图方案基本确定的时候,可以同步开始堆叠评估,确定基本的摆件方案。

2、结构输出DXF和EMN文件

结构输出板框文件,PCB尺寸和形状需要评估满足堆叠需求,无大的堆叠和走线瓶颈,否则在此阶段就需要及时拉通结构甚至ID修改结构、ID设计,避免在走线后期才提出变更需求,倒是项目进度严重受到影响。

堆叠阶段在堆叠完成后,各模块需要基于硬件、结构领域的评审要素进行核查,比如:

《堆叠评审要素》

《应力评审要素》

《温升评审要素》

《静电评审要素》

除了对PCB摆件进行检查确认外,对结构设计文件也要进行确认,比如结构干涉、接地设计、温升散热方案进行评估,并及时输出结构修改意见。

堆叠阶段是考验一个硬件工程师实际能力的关键阶段,此阶段需要工程师熟悉多个领域和模块的专业知识:

1、应力是否满足设计规范,关键裸晶器件的摆件?

2、关键热源器件的摆放是否合理?

3、是否满足DXF需求?是否满足工厂生产对堆叠的需求?

4、对射频的链路优化是否合理?

5、充电器件的路径是否满足阻抗需求?

。。。

需要对结构、基带、射频、天线和工厂生产以及PCB工艺都有非常熟悉。

五、EDA阶段

在摆件完成的差不多的时候,就可以开始layout了,对于手机项目来说,平台部分摆件定下来,就可以先安排走平台部分的关键走线以及扇出工作。

在走线阶段硬件工程师需要和PCB工程师紧密的配合,check在走线过程中的问题。最后拉通各模块基于评审要素进行核查,发板前需要完成必要的仿真工作,排除风险,比如SI/PI仿真、QLINK仿真、UFS仿真等工作。

EVB的发板尽量满足仿真要求并进行改善,否则回板阶段如果遇到无法正常开机或者死机等问题,问题的排查工作将会非常痛苦。

六、EVB调试阶段

EVB作为功能调试板(建议不仅仅当作验证板),在EVB回板后,需要配合BSP将各模块功能调通,硬件领域需要关注如下:

1、漏电流、待机电流

2、主板ESD/浪涌测试

3、传导杂散测试

4、EMC认证测试

5、软硬件功能联调

6、天线无源性能测试

7、基带、射频、天线性能调试

8、产线SMT问题跟踪

上面只是列出一部分硬件领域需要关注的问题,EVB板不能仅仅当作一个功能验证板,能够在EVB上暴露的问题就需要想办法尽量暴露出来。

在完成相关的测试和调试工作之后,将需要优化的原理图和PCB修改点梳理汇总,组织相关模块进行评审工作,完成T0的发板动作。

七、T0第一次组装

T0阶段是第一次组装,此阶段需要重点关注产线组装过程中暴露的问题,在此阶段硬件需要重点关注的问题如下:

1、QE测试项目(整机ESD测试、跌落测试等)

2、整机干扰测试

3、QT测试项目

4、EMC测试项目

5、整机音频测试

6、整机温升测试

7、认证相关的工作

8、EVB测试问题回归验证

在对T0阶段的测试问题进行总结,将需要优化的原理图和PCB的修改点梳理汇总,组织相关的模块进行评审工作,完成EVT阶段的发板动作。

八、EVT阶段(Engineering verfication Test)

EVT为工程验证测试阶段,主要是针对EVT阶段的PCBA和整机进行详细的性能和可靠性测试,T0阶段的测试项可能因为项目节点等无法完成完成的测试,而且因为人力等问题可能只有研发进行摸底测试,在EVT阶段则是测试按照用例进行详细的测试,测试部门将会提交测试case给硬件研发。

此阶段必须经历完整一轮测试,并且研发需要经过分析将问题关闭,对于EVT阶段无法关闭需要下阶段验证的风险问题,必须给出详细的解决方案和应对措施,才能进入DVT阶段。

九、DVT阶段(Design Verification Test)

EVT为设计验证阶段,主要是针对EVT阶段测试的问题进行回归验证,以及进行新一轮的测试,测试项基本同EVT阶段。

十、PVT阶段(Pilot-run Verification Test)

DVT阶段的问题必须全部解决完成才能进入到这个阶段,或者DVT阶段一些风险不太高的问题可以在PVT阶段做回归验证

PVT阶段主要关注的是批量量产产品的可交付性,也是为了大批量量产做准备,测试内容基本同EVT和DVT阶段。

十一、售后阶段

在产品开始正式量产后,硬件工程师需要拉通售后,及时同步售后数据确认首销阶段是否有异常数据和异常问题,并及时对售后问题进行处理。

可以加入知识星球,支持原文下载,并将在星球更新更多核心知识哦,并将在星球定期直播硬件开发知识,欢迎您的加入!