【小黑嵌入式系统第七课】PSoC® 5LP 开发套件(CY8CKIT-050B )——PSoC® 5LP主芯片、I/O系统、GPIO控制LED流水灯的实现

上一课:

【小黑嵌入式系统第六课】嵌入式系统软件设计基础——C语言简述、程序涉及规范、多任务程序设计、状态机建模(FSM)、模块化设计、事件触发、时间触发

文章目录

-

- 一、PSoC® 5LP主芯片

- 二、PSoC 5LP I/O系统

-

- (1) I/O系统特性

- (2) I/O系统怎样运作?

-

- 1、I/O驱动模式

- 2、I/O端口配置寄存器

- 三、GPIO控制LED流水灯的实现

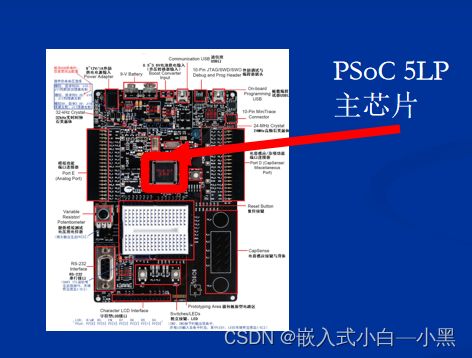

一、PSoC® 5LP主芯片

- PSoC 5LP 是真正的可编程嵌入式片上系统,在同一芯片中集成了自定义的模拟和数字外设功能、存储器以及 ARM Cortex-M3 CPU。

- 带有工作频率高达 80 MHz 的 DMA 控制器、数字滤波处理器以及 32 位 ARM Cortex-M3 内核

- 超低功耗与工业级最宽电压范围

- 带有支持用户自定义的可编程数字和模拟外设

- 任意模拟或数字外设向任意引脚灵活路由的功能

- PSoC 5LP 带有一个丰富的功能集,包括:一个 CPU 和存储器子系统、一个数字子系统、一个模拟子系统以及全部系统资源。

- 性能

- 工作频率介于 DC 至 80 MHz 之间

- 32 位 ARM Cortex-M3 CPU、32 个中断

- 24 通道直接存储器访问(DMA)控制器

- 24 位 64 抽头数字滤波处理器(DFB)

- 存储器

- 程序闪存的最大容量为 256 KB

- 此外,还有多达 32 KB 的闪存空间,用于存储纠错码(ECC)

- SRAM 空间达 64 KB

- EEPROM 容量为 2 KB

- 数字子系统

- 4 个 16 位定时器、计数器和 PWM (TCPWM)模块

- I2C,其总线速度为 1 Mbps

- 获得认证的全速(FS)USB 2.0,其速率为12 Mpbs

- 全速 CAN 2.0b 接口,16 个 Rx 缓冲区,8 个 Tx 缓冲区

- 20 到 24 个 通用数字模块(UDB),通过配置 UDB 模块,可以创建有限数量的如下功能模块:

- 8、16、24 和 32 位定时器、计数器和PWM

- I2C、UART、SPI、I2S 和 LIN 2.0 接口

- 循环冗余校验(CRC)

- 伪随机序列(PRS)发生器

- 正交解码器

- 门限逻辑功能

- 模拟子系统

- 具有 8 至 20 位分辨率的可配置 Delta-Sigma模数转换器

- 最多支持 两 个 12 位 SAR 模 数 转 换 器(ADC)

- 四个 8 位数模转换器(DAC)

- 四个比较器

- 四个运算放大器(opamp)

- 四个可编程模拟模块,用于创建:

- 可编程增益放大器(PGA)

- 互阻放大器(TIA)

- 混频器

- 采样和保持(S/H)电路

- CapSense®支持,多达 62 个传感器

- 1.024 V ± 0.1%内部参考电压

- 多功能 I/O 系统

- 46 至 72 个 I/O 引脚 — 多达 62 个通用 I/O(GPIO)

- 多达 8 个特殊功能 I/O(SIO)引脚

- 25 mA 灌电流

- 可编程的输入/输出电压阈值

- 可作为通用模拟电压比较器使用

- 热交换功能和过压容限

- 可用作 GPIO 的两个 USBIO引脚

- 可从任意一个数字或模拟外设连接到任意的 GPIO

- 任何 GPIO 都具有 LCD 直接驱动器功能,最多可驱动46 × 16 行

- 任何 GPIO 均提供 CapSense 支持

- 1.2 V 至 5.5 V 接口电压,多达 4 个电压域

- 可编程时钟

- 内部振荡器的频率范围为 3 至 74 MHz,在 3 MHz 频率时,精度为 1%

- 外部晶振的频率范围为 4 至 25 MHz

- 内部 PLL 能够生成高达 80 MHz 的时钟

- 频率分别为 1 kHz、33 kHz 和 100 kHz 的低功耗内部振荡器

- 外部时钟晶振的频率为 32.768 kHz

- 可布线到任何外设或 I/O 的 12 个时钟分频器

二、PSoC 5LP I/O系统

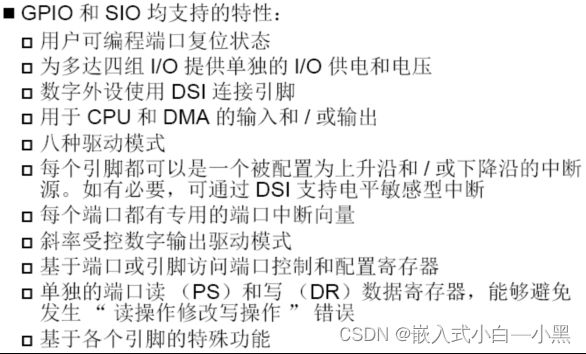

(1) I/O系统特性

-

I/O系统为CPU内核和片内外设提供了连接到外部世界的接口。PSoC的I/O非常灵活,(总体上说)可以连接任意片内信号至任意引脚,从而大大简化了电路设计和电路板布局布线。

-

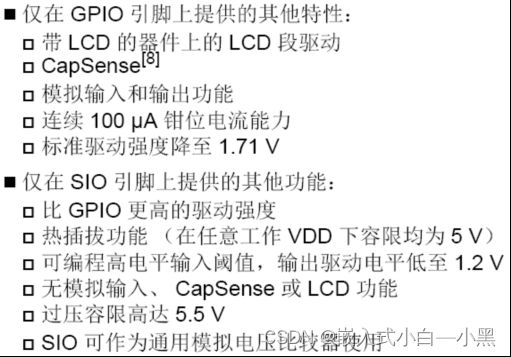

每种PSoC器件均有两种类型的I/O引脚:通用I/O(GPIO)、特殊I/O(SIO)。包含USB功能的器件还提供了第三类的引脚USBIO。

-

GPIO和SIO提供了相似的数字功能,它们的主要区别在于模拟能力和驱动能力。包含USB功能的器件还提供了两个USBIO引脚,支持专门的USB功能和部分GPIO功能。

所有I/O引脚均可供CPU和片内数字外设用作数字输入、数字输出,并且所有I/O引脚都可产生中断。

所有GPIO引脚都可用作模拟输入、CapSense(电容感应)、LCD段驱动。

SIO引脚可被用于超过Vdda电压(器件的最高供电电压)值时的情况,以及用来产生可编程的输出电压,或设置可编程的输入阈值电压。

一个USBIO引脚的结构框图:

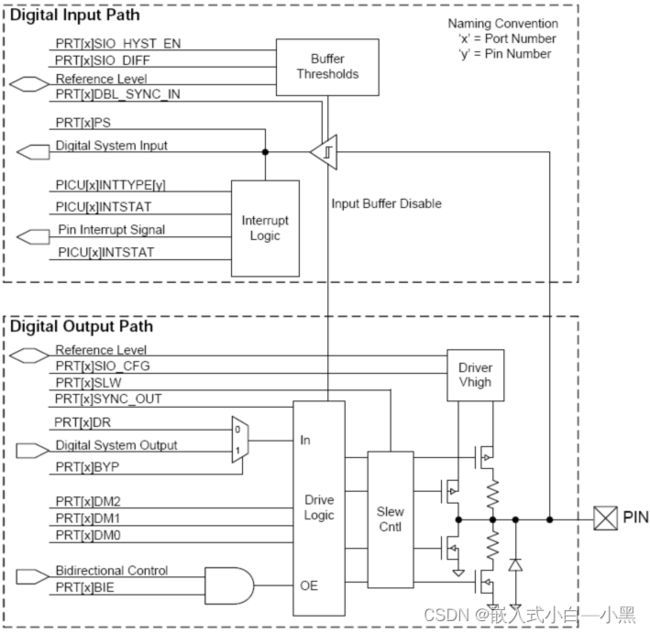

(2) I/O系统怎样运作?

PSoC 的I/O系统提供以下功能:

- 数字输入感测

- 数字输出驱动

- 引脚中断

- 模拟输入、输出的连接

- LCD段驱动、外部存储接口(EMIF)的连接

- 存取片内外设:

(1)用指定port的方式直接连接

(2)通过通用数字块(UDB)经由数字系统互连(DSI)的方式连接

接下来后面主要介绍GPIO的基本运作方式

PSoC 5LP系列器件包含了46~72个I/O引脚,为了方便管理众多的I/O引脚,它们被组织成端口(port)的形式,每个端口最多包含8个引脚(pin)。

一些I/O引脚为多功能复用引脚(除通用功能外,还具有诸如USB、调试口、或石英晶体振荡器等特殊功能),其特殊功能通过相关的控制寄存器来使能,如通过设置石英晶体振荡器控制寄存器,可将该I/O引脚用作石英晶体振荡器功能。

具有多个名称的引脚为多功能复用引脚。

引脚名称中,诸如P1[2]的名称表示该引脚为端口1(port 1)中的2号引脚(pin2)。在PSoC中,一个端口最多包含8个引脚。

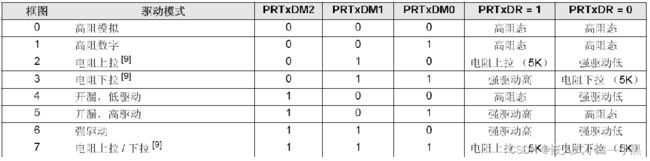

1、I/O驱动模式

I/O驱动模式是引脚的主要属性之一

每个GPIO或SIO引脚都可以被独立配置为8种驱动模式中的一种。

- ‘Out’信号由数据寄存器DR驱动(当引脚的“硬件连接”属性被禁用时),或由其它数字系统电路直接驱动。

- ‘In’信号驱动引脚状态寄存器PS,及其它数字系统电路。

- ‘An’信号连接到模拟系统电路中。

- 高阻模拟

为默认的复位状态,关闭所有的输出驱动器和数字输入缓冲器。这就避免了由于来自浮空的电压引起的流入数字输入缓冲器的电流。这个状态被推荐用于浮空或者支持模拟电压的引脚。

高阻模拟引脚连接到低噪声低干扰的专门布线路径,它不提供数字输入功能。

- 高阻数字

使能输入缓冲器用于数字信号输入。这是一个常用的高阻状态,推荐用于数字输入。

3.电阻上拉或电阻下拉

上拉或下拉各自在一个数据状态下提供串行电阻,并在另一数据状态下提供强驱动。该模式下,引脚能被用于数字输入/输出。这些模式常见于连接机械开关。

4.开漏、高驱动,开漏、低驱动

开漏模式引脚在一种数据状态下为高阻,在另一数据状态下提供强驱动。引脚能被用于数字输入/输出。

一个典型的应用是驱动I2C总线上的信号线。

5.强驱动

在高或低电平输出状态均提供强的CMOS输出驱动。这是引脚常用的输出模式。通常,强驱动模式引脚不得用作输入。这个模式通常用于驱动数字输出信号或者外部的FET。

6.电阻上拉和下拉

与电阻上拉或下拉模式类似,区别是总是存在串行电阻。在高输出状态是上拉,而在低输出状态是下拉。

该模式常用于其它可能引起短路的信号在驱动总线时。

如果I/O引脚选择旁路模式(缺省模式),则实际的I/O引脚上电压由端口数据寄存器(DR)值、引脚驱动模式、引脚所接负载共同决定。引脚电平状态可从端口状态寄存器(PS)中获得。

每个I/O引脚有三个驱动模式配置位(DM[2:0]),这些配置位位于一组PRTx_DM[2:0]寄存器中。 例如寄存器PRTx_DM2、 PRTx_DM1、 PRTx_DM0的各自bit y位,这3位用来设置portx的piny引脚(即Px[y]引脚)的驱动模式。

I/O引脚驱动模式

2、I/O端口配置寄存器

配置I/O引脚驱动模式,以及引脚的其它一些功能设置,可通过两种方式:

- 端口配置寄存器 —— 对某端口的全部引脚进行配置

- 引脚配置寄存器 —— 单独配置某一个端口的某一引脚

CPU可通过写端口数据寄存器(PRTx_DR)来让引脚输出高低电平(或高阻态);CPU通过读引脚状态寄存器(PRTx_PS)来获取引脚实际的电平状态。

端口配置寄存器:配置某端口的所有引脚,每种寄存器配置一个功能,各引脚功能设置可相同也可不相同。

表中所列的各寄存器均为一组寄存器。如PRT[0…11]_DR,表示有12个寄存器,分别为PRT0_DR ~ PRT11_DR,寄存器名中的数字表示端口号(即分别对应port0~port11的数据寄存器)。每个寄存器为8位,寄存器每个bit对应该端口的一个引脚,如PRT0_DR寄存器的bit0对应port0的pin0(即P0[0]引脚)。

PRT[0…11]_PRT配置寄存器(只写):

将某端口的所有引脚配置为相同模式,一次完成全部功能配置。

使用PRTx_PRT寄存器实现对port x的所有引脚的一次性相同配置

端口引脚配置寄存器(PRTx_PC0 ~ PRTx_PC7):用于访问单个I/O端口引脚的配置或状态位。下图给出了访问P3[2]引脚配置寄存器的结构图。

全部的端口引脚配置寄存器简化表示为PRT[0…14]_PC[0…7],最多包含15x8个寄存器。

寄存器名称前面的数字为端口号,后面的数字为引脚号,如寄存器PRT3_PC2为port3的pin2(即P3[2]引脚)引脚配置寄存器。

三、GPIO控制LED流水灯的实现

-

方法1(参见示例项目LED_Marquee):用Creator组件库中的数字输出引脚组件绘制原理图,在项目的设计范围资源文件(.cydwr)中设置其与实际引脚的映射,用该组件的API函数来控制GPIO口的输出。

-

方法2(参见示例项目LED_Marquee2):用Creator组件库中的cy_boot组件(该组件自动被包含进每个项目中,原理图中不显示),无需画原理图及设置引脚映射,直接用该组件的API函数来配置GPIO口及控制GPIO口的输出。

-

方法3(参见示例项目LED_Marquee3):直接通过I/O系统相关的寄存器,来配置GPIO口及控制GPIO口的输出,无需画原理图及设置引脚映射。

建议使用方法1或方法2,尤其方法1。方法3只在要求很快的I/O操作速度时才需要。

补:延时的实现可利用cy_boot组件所提供的延时函数CyDelay()

关于GPIO控制LED流水灯的每个示例项目的阅读及运行:

(1)打开项目目录中的.cywrk文件;(项目路径中不能含有中文)

(2)而后查看项目的原理图TopDesign.cysch、项目的设计范围资源文件.cydwr、main.c、GPIO.h(仅对LED_Marquee3 示例项目);

(3)将程序下载至PSoC 5LP芯片中(USB线连接到板上的J1口),实际观察运行效果。

关于GPIO控制LED流水灯的示例项目的注意事项:

(1)注意示例项目中的注释;

(2)在运行程序前需先将CY8CKIT-050板上的LED1与P0[0]插孔用导线连接、将LED2与P0[1]连接;

(3)Creator自带的组件,均有组件数据手册(中文翻译版需到Cypress官网中搜索下载),里面有该组件的功能、各种配置、API函数等内容的详细说明。

(4)每个项目都会自动隐式地包含cy_boot组件,该组件提供了存取芯片资源的一种方式,提供了大量直接可用的API函数。所有示例项目均使用了cy_boot的一个API函数 —— 延时函数CyDelay(),示例项目2还使用了其引脚相关API函数。

(5)PSoC 5LP器件内的所有寄存器的功能及使用说明,参见“PSoC 5LP寄存器技术参考手册”(PSoC 5LP Registers TRM)。

(6)源程序中有一些Creator自定义的数据类型,如main.c文件中的uint8类型,这些自定义数据类型的含义参见 System Reference Guides 。