实战篇:modelsim独立仿真

在本实战之前,均是用的quartus+modelsim联合仿真,发现在修改代码后,需要重新打开modelsim。如果每次均需要在观察界面下加入模块的信号以及对不同信号进行颜色标注时,联合仿真将表现得不友好,很无奈。因此,习惯使用独立仿真吧,由于Modelsim可以支持命令行的方式,通过创建do文件,可以集成多个可执行的命令。那么对于前期一边编写代码,一边进行功能仿真,使用do文件是可以明显提高工作的效率。

目录

一、使用modelsim界面新建仿真工程

二、使用do文件进行Modelsim仿真

一、使用modelsim界面新建仿真工程

参考:(16条消息) 搭建Modelsim SE仿真环境-使用do文件仿真_七水的博客-CSDN博客,原文链接:https://blog.csdn.net/lg2lh/article/details/51176467

第一步:打开Modelsim SE,点击菜单栏“File—>New—>Project”,准备新建工程。

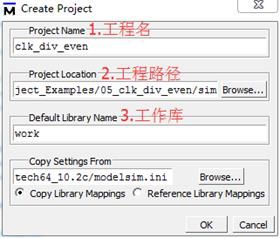

第二步:弹出“Create Project”对话框,按下图填写仿真工程名称,以及工程的存储路径,以及默认库的的名称,这里默认库名为“work”,我们通常叫作工作库。设置好后点击OK。

这里介绍一下库的概念,即library。库是Modelsim仿真的载体,Modelsim会将仿真工程中的设计文件(DUT)和激励文件(Testbench)的编译(Compile)结果存放在work库中,在我们新建工程的时候就会带着生成一个work库,如下图在Modelsim工作区,选择Library选项卡,我们可以看到生成的work库,此时work库是空的,因为我们还没有添加并仿真设计文件和激励文件。

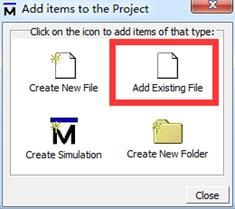

第三步:新建或添加设计文件,这里我们已经写好的testbench和待测模块,所以选择直接添加已存在文件即可。

第四步:依次添加testbench和待测模块文件。

第五步:编译我们的DUT和Testbench文件,如下图在工作区域选择Project选项卡,右键选择Compile—>Compile All,编译所有。

这里,如果有引用.h的头文件,首次modelsim编译可能会失败,显示 Cannot find `include file "xxxxxx" in directories:后面是.v文件中引用的头文件中的变量。

这时,需要设置下无法编译的.v文件,单击鼠标右键-> Properity,在“Verilog&Systemverilog”选项卡中找到“Include Directory”中添加头文件所在的文件夹,确认后编译即可保证工程正常编译进行仿真了。

![]()

如果是VHDL文档由于找不到所引用的文档可以按照同样的方法,鼠标右键单击编译不通过的文件 ->Properity,在VHDL选项卡里面“PSLFile”找到该文件需要引用的文件,重新编译即可。

![]()

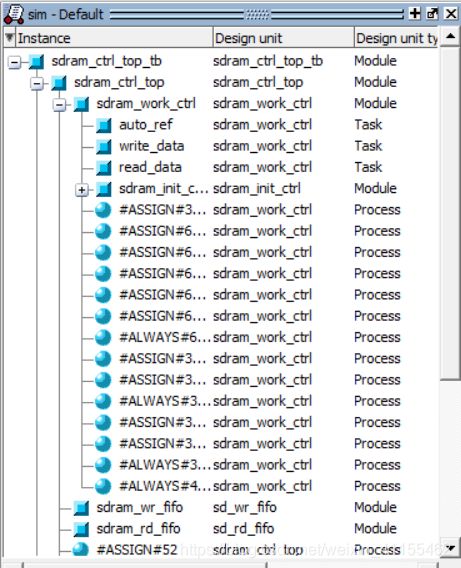

第六步:切回到Library,此时再看work库就不是空的了,work库里的。选中Testbench仿真结果sdram_ctrl_top_tb.v,右键—>Simulate without Optimization,启动无优化仿真。

实践结果:

1.在第5步的时候看work,显示unavailable,并没有+。在工程下将之前建的work修改为work_rtl,重启modelsim后library库里有了work_rtl,但是work还是显示unavailable,无奈,尝试其他操作没有效果后准备重新新建,然后重启,发现发现work下有+,并且有编译成功的文件。迷了~~~~~

2.sdram_ctrl_top_tb.v,右键—>Simulate without Optimization后,显示IP核错误,Instantiation of 'dcfifo' failed. The design unit was not found. 这是因为在添加IP核生成的.v文件时需要将__bb文件一起添加进去。即需要将整个项目生成的.v文件全部进行编译才可以。 终于成功可以走下一步了~~~~

第七步:弹出仿真波形窗口(wave窗口),但是窗口内没有任何信号波形,工作区域多了一个sim选项卡,进入sim选项页,可以看到仿真实例。选择相应的实例,右键—>add wave,添加信号到wave窗口。

第八步:切到wave 窗口,运行仿真。这样我们就可以看到输出的波形信号了,从而验证设计的正确性。

二、使用do文件进行Modelsim仿真

通过do文件快速搭建仿真环境,会比上面的更快捷,只需要双击批处理文件modelsim_run.bat,就可以自动调用Modelsim,并自动完成对Testbench和待验证设计文件的编译和仿真,并且可以自动将要观察的信号添加到wave窗口。

实际操作:只需要以文本的形式创新.bat文件即可。如果文件扩展名被隐藏,可以参考:win10怎么显示文件扩展名-百度经验 (baidu.com),其他操作系统也可自行搜索。

modelsim_run.bat文件:这是一个批处理文件,里面就一行“modelsim -do testbench文件名称.do”,这是一条DOS命令,意思就是调用Modelsim工具,并在Modelsim工具中执行sim.do这个文件。

testbench文件名称.do:do文件是由tcl脚本语言编写的,以下是do文件的内容。

vlib work

vlog ../sim/*.v

vlog ../src/*.v

vsim-t ns -novopt +notimingchecks work.tb_clk_div_even

radix hex

addwave -position insertpoint sim:/tb_clk_div_even/clk_div_even_inst/*

run -all也可参考:http://www.it610.com/article/1577426.htm

或者:Modelsim之提高篇——do脚本、bat命令 (icode9.com)

或者:(17条消息) modelsim脚本仿真(二)带IP核工程仿真_幸运学者的博客-CSDN博客