HDLBits全部解答

文章目录

-

- Getting Started

-

- step_one

- Zero

- Verilog Language

-

- Basics

-

- Wire

- Wire4

- Notgate

- Andgate

- Norgate

- Xnorgate

- Wire decl

- 7458

- Vectors

-

- Vector0

- Vector1

- Vector2

- Vectorgates

- Gates4

- Vector3

- Vectorr

- Vector4

- Vector5

- Modules Hierarchy

-

- Module

- Module pos

- Module name

- Module shift

- Module shift8

- Module add

- Module fadd

- Module cseladd

- Module addsub

- Procedures

-

- Alwaysblock1

- Alwaysblock2

- Always if

- Always if2

- Always case

- Always case2

- Always casez

- Always nolatches

- More Verilog Features

-

- Conditional

- Reduction

- Gates100

- Vector100r

- Popcount255

- Adder100i

- Bcdadd100

- Circuits

-

- Combinational Logic

-

- Basic Gates

-

- m2014 q4h

- m2014 q4i

- m2014 q4e

- m2014 q4f

- m2014 q4g

- Gates

- 7420

- Truthtable1

- Mt2015 eq2

- Mt2015 q4a

- Mt2015 q4b

- Mt2015 q4

- Ringer

- Thermostat

- Popcount3

- Gatesv

- Gatesv100

- Multiplexers

-

- Mux2to1

- Mux2to1v

- Mux9to1v

- Mux256to1

- Mux256to1v

- Arithmetic Circuits

-

- Hadd

- Fadd

- Adder3

- m2014 q4j

- ece241 2014 q1c

- Adder100

- Bcdadd4

- Karnaugh Map to Circuit

-

- Kmap1

- Kmap2

- Kmap3

- Kmap4

- ece241 2013 q2

- m2014 q3

- 2012 q1g

- ece241 2014 q3

- Sequential Logic

-

- Latches and Flip-Flops

-

- Dff

- Dff8

- Dff8r

- Dff8p

- Dff8ar

- Dff16e

- m2014 q4a

- m2014 q4b

- m2014 q4c

- m2014 q4d

- Mt2015 muxdff

- 2014 q4a

- ece241 2014 q4

- ece241 2013 q7

- Edgedetect

- Edgedetect2

- Edgecapture

- Dualedge

- Counters

-

- Count15

- Count10

- Count1to10

- Countslow

- ece241 2014 q7a

- ece241 2014 q7b

- Countbcd

- Count clock

- Shift Registers

-

- Shift4

- Rotate100

- Shift18

- Lfsr5

- Mt2015 lfsr

- Lfsr32

- m2014 q4k

- 2014 q4b

- ece241 2013 q12

- More Circuits

-

- Rule90

- Rule110

- Conwaylife

- Finite State Machines

-

- Fsm1

- Fsm1s

- Fsm2

- Fsm2s

- Fsm3comb

- Fsm3onehot

- Fsm3

- Fsm3s

- ece241 2013 q4

- Lemmings1

- Lemmings2

- Lemmings3

- Lemmings4

- Fsm onehot

- Fsm ps2

- Fsm ps2data

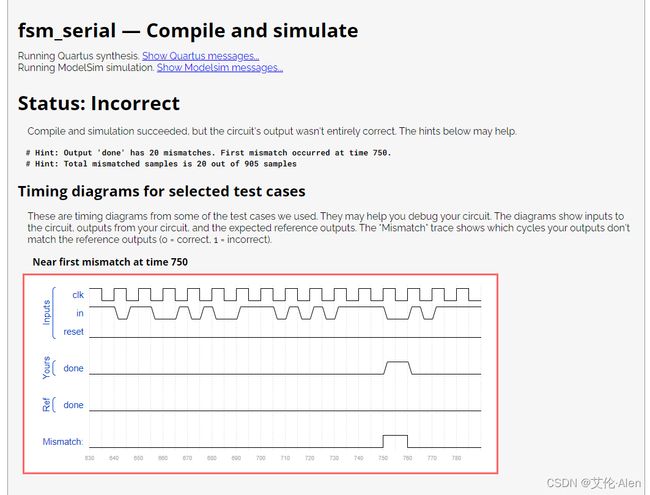

- Fsm serial

- Fsm serialdata

- Fsm serialdp

- Fsm hdlc

- ece241 2013 q8

- ece241 2014 q5a

- ece241 2014 q5b

- 2014 q3fsm

- 2014 q3bfsm

- 2014 q3c

- m2014 q6b

- m2014 q6c

- m2014 q6

- 2012 q2fsm

- 2012 q2b

- 2013 q2afsm

- 2013 q2bfsm

- Building Larger Circuits

-

- review2015 count1k

- review2015 shiftcount

- review2015 fsmseq

- review2015 fsmshift

- review2015 fsm

- review2015 fancytimer

- review2015 fsmonehot

- Verification: Reading Simulations

-

- Finding bugs in code

-

- Bugs mux2

- Bugs nand3

- Bugs mux4

- Bugs addsubz

- Bugs case

- Building a circuit from a simulation waveform

-

- circuit1

- circuit2

- circuit3

- circuit4

- circuit5

- circuit6

- circuit7

- circuit8

- circuit9

- circuit10

- Verfication: Writing Testbenches

-

- clock

- tb1

- and

- tb2

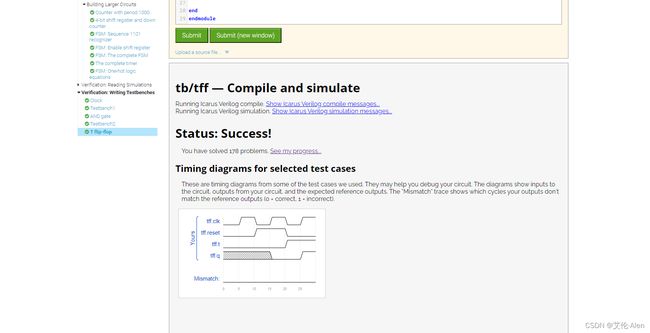

- tff

- 最后

Getting Started

step_one

module top_module( output one );

// Insert your code here

assign one = 1'b1;

endmodule

Zero

module top_module(

output zero

);// Module body starts after semicolon

assign zero = 1'b0;

endmodule

Verilog Language

Basics

Wire

module top_module( input in, output out );

assign out = in;

endmodule

Wire4

module top_module(

input a,b,c,

output w,x,y,z );

assign w = a;

assign x = b;

assign y = b;

assign z = c;

endmodule

Notgate

module top_module( input in, output out );

assign out = ~in;

endmodule

Andgate

module top_module(

input a,

input b,

output out );

assign out = a && b;

endmodule

Norgate

或非门(英语:NOR gate)是数字逻辑电路中的基本元件,实现逻辑或非功能。有多个输入端,1个输出端,多输入或非门可由2输入或非门和反相器构成。

只有当两个输入A和B为低电平(逻辑0)时输出为高电平(逻辑1)。也可以理解为任意输入为高电平(逻辑1),输出为低电平(逻辑0)。

module top_module(

input a,

input b,

output out );

//或非门(英语:NOR gate)是数字逻辑电路中的基本元件,实现逻辑或非功能。

//有多个输入端,1个输出端,多输入或非门可由2输入或非门和反相器构成。

//只有当两个输入A和B为低电平(逻辑0)时输出为高电平(逻辑1)。也可以理解为任意输入为高电平(逻辑1),输出为低电平(逻辑0)。

assign out = ((a == 1'b0) && (b == 1'b0) ) ? 1'b1 : 1'b0;

endmodule

Xnorgate

module top_module(

input a,

input b,

output out );

//同或门(英语:XNOR gate或equivalence gate)也称为异或非门,

//在异或门的输出端再加上一个非门就构成了异或非门,是数字逻辑电路的基本单元,有2个输入端、1个输出端。

//当2个输入端中有且只有一个是低电平(逻辑0)时,输出为低电平。亦即当输入电平相同时,输出为高电平(逻辑1)。

assign out = (a == b) ? 1'b1 :1'b0;

endmodule

同或门(英语:XNOR gate或equivalence gate)也称为异或非门,

在异或门的输出端再加上一个非门就构成了异或非门,是数字逻辑电路的基本单元,有2个输入端、1个输出端。

当2个输入端中有且只有一个是低电平(逻辑0)时,输出为低电平。亦即当输入电平相同时,输出为高电平(逻辑1)。

Wire decl

//`default_nettype none

module top_module(

input a,

input b,

input c,

input d,

output out,

output out_n );

wire first;

wire second;

assign first = a && b;

assign second = c && d;

assign out = first || second;

assign out_n = ~out;

endmodule

7458

module top_module (

input p1a, p1b, p1c, p1d, p1e, p1f,

output p1y,

input p2a, p2b, p2c, p2d,

output p2y );

wire wire1;

wire wire2;

wire wire3;

wire wire4;

assign wire1 = p2a && p2b;

assign wire2 = p2c && p2d;

assign p2y = wire1 || wire2;

assign wire3 = p1a && p1b && p1c;

assign wire4 = p1f && p1e && p1d;

assign p1y = wire3 || wire4;

endmodule

Vectors

Vector0

module top_module (

input wire [2:0] vec,

output wire [2:0] outv,

output wire o2,

output wire o1,

output wire o0 ); // Module body starts after module declaration

assign outv = vec;

assign o0 = vec[0];

assign o1 = vec[1];

assign o2 = vec[2];

endmodule

Vector1

`default_nettype none // Disable implicit nets. Reduces some types of bugs.

module top_module(

input wire [15:0] in,

output wire [7:0] out_hi,

output wire [7:0] out_lo );

assign out_hi = in[15:8];

assign out_lo = in[7:0];

endmodule

Vector2

module top_module(

input [31:0] in,

output [31:0] out );//

// assign out[31:24] = ...;

assign out[31:24] = in[7:0];

assign out[23:16] = in[15:8];

assign out[15:8] = in[23:16];

assign out[7:0] = in[31:24];

endmodule

Vectorgates

module top_module(

input [2:0] a,

input [2:0] b,

output [2:0] out_or_bitwise,

output out_or_logical,

output [5:0] out_not

);

assign out_or_bitwise = a | b;

assign out_or_logical = a || b;

assign out_not[5:3] = ~b;

assign out_not[2:0] = ~a;

endmodule

Gates4

module top_module(

input [3:0] in,

output out_and,

output out_or,

output out_xor

);

assign out_and = in[3] & in[2] & in[1] & in[0] ;

assign out_or = in[3] | in[2] | in[1] | in[0] ;

assign out_xor = (in[3] == in[2] == in[1] == in[0]) ? 1'b0 : 1'b1;

endmodule

Vector3

module top_module (

input [4:0] a, b, c, d, e, f,

output [7:0] w, x, y, z );//

// assign { ... } = { ... };

assign w = {a,b[4:2]};

assign x = {b[1:0],c,d[4]};

assign y = {d[3:0],e[4:1]};

assign z = {e[0],f,2'b11};

endmodule

Vectorr

module top_module(

input [7:0] in,

output [7:0] out

);

assign out = {in[0],in[1],in[2],in[3],in[4],in[5],in[6],in[7]};

endmodule

// I know you're dying to know how to use a loop to do this:

//Create a combinational always block. This creates combinational logic that computes the same result

//as sequential code. for-loops describe circuit *behaviour*, not *structure*, so they can only be used

//inside procedural blocks (e.g., always block).

//The circuit created (wires and gates) does NOT do any iteration: It only produces the same result

//AS IF the iteration occurred. In reality, a logic synthesizer will do the iteration at compile time to

//figure out what circuit to produce. (In contrast, a Verilog simulator will execute the loop sequentially

//during simulation.)

//always @(*) begin

// for (int i=0; i<8; i++) // int is a SystemVerilog type. Use integer for pure Verilog.

// out[i] = in[8-i-1];

//end

//It is also possible to do this with a generate-for loop. Generate loops look like procedural for loops,

//but are quite different in concept, and not easy to understand. Generate loops are used to make instantiations

//of "things" (Unlike procedural loops, it doesn't describe actions). These "things" are assign statements,

//module instantiations, net/variable declarations, and procedural blocks (things you can create when NOT inside

//a procedure). Generate loops (and genvars) are evaluated entirely at compile time. You can think of generate

//blocks as a form of preprocessing to generate more code, which is then run though the logic synthesizer.

//In the example below, the generate-for loop first creates 8 assign statements at compile time, which is then

//synthesized.

//Note that because of its intended usage (generating code at compile time), there are some restrictions

//on how you use them. Examples: 1. Quartus requires a generate-for loop to have a named begin-end block

//attached (in this example, named "my_block_name"). 2. Inside the loop body, genvars are read only.

//generate

// genvar i;

// for (i=0; i<8; i = i+1) begin: my_block_name

// assign out[i] = in[8-i-1];

// end

//endgenerate

Vector4

module top_module (

input [7:0] in,

output [31:0] out );//

// assign out = { replicate-sign-bit , the-input };

assign out ={{24{in[7]}},in};

endmodule

Vector5

module top_module (

input a, b, c, d, e,

output [24:0] out );//

// The output is XNOR of two vectors created by

// concatenating and replicating the five inputs.

// assign out = ~{ ... } ^ { ... };

assign out = ~{{5{a}},{5{b}},{5{c}},{5{d}},{5{e}}} ^ {{5{a,b,c,d,e}}};

endmodule

Modules Hierarchy

Module

module top_module ( input a, input b, output out );

mod_a instance2 (

.out(out),

.in1(a),

.in2(b)

);

endmodule

Module pos

module top_module (

input a,

input b,

input c,

input d,

output out1,

output out2

);

mod_a u_mod_a(

out1,

out2,

a,

b,

c,

d

);

endmodule

Module name

module top_module (

input a,

input b,

input c,

input d,

output out1,

output out2

);

mod_a u_mod_a(

.out1(out1),

.out2(out2),

.in1(a),

.in2(b),

.in3(c),

.in4(d)

);

endmodule

Module shift

module top_module ( input clk, input d, output q );

wire wire1;

wire wire2;

my_dff my_dff_1(

.clk(clk),

.d(d),

.q(wire1)

);

my_dff my_dff_2(

.clk(clk),

.d(wire1),

.q(wire2)

);

my_dff my_dff_3(

.clk(clk),

.d(wire2),

.q(q)

);

endmodule

Module shift8

module top_module (

input clk,

input [7:0] d,

input [1:0] sel,

output [7:0] q

);

wire [7:0] wire1;

wire [7:0] wire2;

wire [7:0] wire3;

my_dff8 my_dff8_u1(

.clk(clk),

.d(d),

.q(wire1)

);

my_dff8 my_dff8_u2(

.clk(clk),

.d(wire1),

.q(wire2)

);

my_dff8 my_dff8_u3(

.clk(clk),

.d(wire2),

.q(wire3)

);

always @( *) begin

case (sel)

2'd0:q <= d;

2'd1:q <= wire1;

2'd2:q <= wire2;

2'd3:q <= wire3;

endcase

end

endmodule

Module add

module top_module(

input [31:0] a,

input [31:0] b,

output [31:0] sum

);

wire [15:0] low;

wire [15:0] heigh;

wire wire1;

add16 add16_low(

.a(a[15:0]),

.b(b[15:0]),

.cin(1'b0),

.sum(low),

.cout(wire1)

);

add16 add16_heigh(

.a(a[31:16]),

.b(b[31:16]),

.cin(wire1),

.sum(heigh),

.cout()

);

assign sum = {heigh,low};

endmodule

Module fadd

module top_module (

input [31:0] a,

input [31:0] b,

output [31:0] sum

);//

wire [15:0] low;

wire [15:0] heigh;

wire wire1;

add16 add16_low(

.a(a[15:0]),

.b(b[15:0]),

.cin(1'b0),

.sum(low),

.cout(wire1)

);

add16 add16_heigh(

.a(a[31:16]),

.b(b[31:16]),

.cin(wire1),

.sum(heigh),

.cout()

);

assign sum = {heigh,low};

endmodule

module add1 ( input a, input b, input cin, output sum, output cout );

// Full adder module here

/*

reg sum1;

reg cout1;

always @( *) begin

case (a + b + cin)

1'b0:begin

cout1 <= 1'b0;

sum1 <= 1'b0;

end

1'b1:

begin

cout1 <= 1'b0;

sum1 <= 1'b1;

end

2'b10:

begin

cout1 <= 1'b1;

sum1 <= 1'b0;

end

2'b11:

begin

cout1 <= 1'b1;

sum1 <= 1'b1;

end

endcase

end

assign sum = sum1;

assign cout = cout1;*/

//Full adder equations:

assign sum = a ^ b ^ cin;//位异或,加法器可以用异或来实现

assign cout = a&b | a&cin | b&cin;

//太复杂了,直接位运算就好了

endmodule

Module cseladd

module top_module(

input [31:0] a,

input [31:0] b,

output [31:0] sum

);

wire [15:0] low;

wire [15:0] heigh1;

wire [15:0] heigh2;

wire wire1;

add16 add16_low(

.a(a[15:0]),

.b(b[15:0]),

.cin(1'b0),

.sum(low),

.cout(wire1)

);

add16 add16_heigh0(

.a(a[31:16]),

.b(b[31:16]),

.cin(1'b0),

.sum(heigh1),

.cout()

);

add16 add16_heigh1(

.a(a[31:16]),

.b(b[31:16]),

.cin(1'b1),

.sum(heigh2),

.cout()

);

assign sum = (wire1) ? {heigh2,low} : {heigh1,low};

endmodule

Module addsub

module top_module(

input [31:0] a,

input [31:0] b,

input sub,

output [31:0] sum

);

wire [31:0] new_b;

wire [15:0] low;

wire [15:0] heigh;

wire wire1;

assign new_b = (sub == 1'b1) ? ((~b) + 1'b1) : (b);//补码

add16 add16_low(

.a(a[15:0]),

.b(new_b[15:0]),

.cin(1'b0),

.sum(low),

.cout(wire1)

);

add16 add16_heigh(

.a(a[31:16]),

.b(new_b[31:16]),

.cin(wire1),

.sum(heigh),

.cout()

);

assign sum = {heigh,low};

endmodule

Procedures

Alwaysblock1

// synthesis verilog_input_version verilog_2001

module top_module(

input a,

input b,

output wire out_assign,

output reg out_alwaysblock

);

assign out_assign = a & b;

always @( *) begin

out_alwaysblock <= a & b;

end

endmodule

Alwaysblock2

// synthesis verilog_input_version verilog_2001

module top_module(

input clk,

input a,

input b,

output wire out_assign,

output reg out_always_comb,

output reg out_always_ff );

assign out_assign = a ^ b;

always @( *) begin

out_always_comb <= a ^ b;

end

always @(posedge clk) begin

out_always_ff <= a ^b;

end

endmodule

Always if

// synthesis verilog_input_version verilog_2001

module top_module(

input a,

input b,

input sel_b1,

input sel_b2,

output wire out_assign,

output reg out_always );

assign out_assign = ((sel_b1 == 1'b1) && (sel_b2 == 1'b1)) ? b : a;

always @( *) begin

if ((sel_b1 == 1'b1) && (sel_b2 == 1'b1)) begin

out_always <= b;

end

else

out_always <= a;

end

endmodule

Always if2

// synthesis verilog_input_version verilog_2001

module top_module (

input cpu_overheated,

output reg shut_off_computer,

input arrived,

input gas_tank_empty,

output reg keep_driving ); //

always @(*) begin

if (cpu_overheated)

shut_off_computer = 1;

else

shut_off_computer = 0;

end

always @(*) begin

if (~arrived)

keep_driving = ~gas_tank_empty;

else

keep_driving = 0;

end

endmodule

Always case

// synthesis verilog_input_version verilog_2001

module top_module (

input [2:0] sel,

input [3:0] data0,

input [3:0] data1,

input [3:0] data2,

input [3:0] data3,

input [3:0] data4,

input [3:0] data5,

output reg [3:0] out );//

always@(*) begin // This is a combinational circuit

case(sel)

3'd0:

out <= data0;

3'd1:

out <= data1;

3'd2:

out <= data2;

3'd3:

out <= data3;

3'd4:

out <= data4;

3'd5:

out <= data5;

default :

out <= 4'b0;

endcase

end

endmodule

Always case2

// synthesis verilog_input_version verilog_2001

module top_module (

input [3:0] in,

output reg [1:0] pos );

always @( *) begin

casez (in[3:0])

4'b0000:

pos = 2'd0;

4'bzzz1:

pos = 2'd0;

4'bzz1z:

pos = 2'd1;

4'bz1zz:

pos = 2'd2;

4'b1zzz:

pos = 2'd3;

default :

pos <= 2'd0;

endcase

end

endmodule

Always casez

// synthesis verilog_input_version verilog_2001

module top_module (

input [7:0] in,

output reg [2:0] pos );

always @( *) begin

casez (in)

8'bzzzzzzz1:pos = 3'd0;

8'bzzzzzz1z:pos = 3'd1;

8'bzzzzz1zz:pos = 3'd2;

8'bzzzz1zzz:pos = 3'd3;

8'bzzz1zzzz:pos = 3'd4;

8'bzz1zzzzz:pos = 3'd5;

8'bz1zzzzzz:pos = 3'd6;

8'b1zzzzzzz:pos = 3'd7;

default :pos = 3'd0;

endcase

end

endmodule

Always nolatches

// synthesis verilog_input_version verilog_2001

module top_module (

input [15:0] scancode,

output reg left,

output reg down,

output reg right,

output reg up );

always @( *) begin

left = 1'b0;

down = 1'b0;

right = 1'b0;

up = 1'b0;

case (scancode)

16'he06b:left = 1'b1;

16'he072:down = 1'b1;

16'he074:right = 1'b1;

16'he075:up = 1'b1;

endcase

end

endmodule

More Verilog Features

Conditional

module top_module (

input [7:0] a, b, c, d,

output [7:0] min);//

// assign intermediate_result1 = compare? true: false;

wire [7:0] ab;

wire [7:0] cd;

assign ab = (a < b) ? a : b;

assign cd = (c < d) ? c : d;

assign min = (ab < cd) ? ab : cd;

endmodule

Reduction

module top_module (

input [7:0] in,

output parity);

assign parity = ^ in[7:0];

endmodule

Gates100

module top_module(

input [99:0] in,

output out_and,

output out_or,

output out_xor

);

assign out_and = & in[99:0];

assign out_or = | in[99:0];

assign out_xor = ^ in[99:0];

endmodule

Vector100r

module top_module(

input [99:0] in,

output [99:0] out

);

reg [99:0] out1;

always @( *) begin

for (integer i = 0;i<=99 ;i=i+1 ) begin

out1[99-i] <= in[i];

end

end

assign out = out1;

endmodule

/*

integer类型也是一种寄存器数据类型,integer类型的变量为有符号数,而reg类型的变量则为无符号数,用integer的变量都可以用reg定

义,只是用于计数更方便而已。

module top_module (

input [99:0] in,

output reg [99:0] out

);

always @(*) begin

for (int i=0;i<$bits(out);i++) // $bits() is a system function that returns the width of a signal.

out[i] = in[$bits(out)-i-1]; // $bits(out) is 100 because out is 100 bits wide.

end

endmodule

*/

Popcount255

module top_module(

input [254:0] in,

output [7:0] out );

reg [7:0] out1;

always @( *) begin

out1 = 8'b0;//赋值语句一定要放在always块里

for (integer i =0 ;i<=254 ;i=i+1 ) begin

if (in[i] == 1'b1) begin

out1 <= out1 +1'b1;

end

else

out1 <= out1;

end

end

assign out = out1;

endmodule

Adder100i

module top_module(

input [99:0] a, b,

input cin,

output [99:0] cout,

output [99:0] sum );

assign sum[0] = a[0] ^ b[0]^ cin;

assign cout[0] = a[0]&b[0] | a[0]&cin | b[0]&cin;

//这两句就可以实现一个一位全加器

genvar i;

generate

for( i=1; i<=99; i=i+1) begin:add1

assign sum[i] = a[i] ^ b[i]^ cout[i-1];

assign cout[i] = a[i]&b[i] | a[i]&cout[i-1] | b[i]&cout[i-1];

end

endgenerate

endmodule

Bcdadd100

module top_module(

input [399:0] a, b,

input cin,

output cout,

output [399:0] sum );

reg [99:0] cout_reg;

bcd_fadd (

.a(a[3:0]),

.b(b[3:0]),

.cin(cin),

.cout(cout_reg[0]),

.sum(sum[3:0])

);

genvar i;

generate

for (i = 1;i<=99 ; i=i+1) begin:fadd

bcd_fadd fadd(

.a(a[4*(i+1)-1:4*(i+1)-4]),

.b(b[4*(i+1)-1:4*(i+1)-4]),

.cin(cout_reg[i-1]),

.cout(cout_reg[i]),

.sum(sum[4*(i+1)-1:4*(i+1)-4])

);

end

endgenerate

assign cout = cout_reg[99];

endmodule

Circuits

Combinational Logic

Basic Gates

m2014 q4h

module top_module (

input in,

output out);

assign out = in ;

endmodule

m2014 q4i

module top_module (

output out);

assign out = 1'b0;

endmodule

m2014 q4e

module top_module (

input in1,

input in2,

output out);

assign out = ~(in1 | in2);

endmodule

m2014 q4f

module top_module (

input in1,

input in2,

output out);

assign out = in1 & ~in2;

endmodule

m2014 q4g

module top_module (

input in1,

input in2,

input in3,

output out);

assign out = in3 ^ ~(in1 ^ in2);

endmodule

Gates

module top_module(

input a, b,

output out_and,

output out_or,

output out_xor,

output out_nand,

output out_nor,

output out_xnor,

output out_anotb

);

assign out_and = a & b;

assign out_or = a | b;

assign out_xor = a ^ b;

assign out_nand = ~(a & b);

assign out_nor = ~(a | b);

assign out_xnor = ~(a ^ b);

assign out_anotb = a & ~b;

endmodule

7420

module top_module (

input p1a, p1b, p1c, p1d,

output p1y,

input p2a, p2b, p2c, p2d,

output p2y );

assign p1y = ~(p1a & p1b & p1c & p1d);

assign p2y = ~(p2a & p2b & p2c & p2d);

endmodule

Truthtable1

module top_module(

input x3,

input x2,

input x1, // three inputs

output f // one output

);//可以用卡诺图化简

assign f =(x3 & x1) | (~x3 & x2);

endmodule

Mt2015 eq2

module top_module ( input [1:0] A, input [1:0] B, output z );

assign z = (A == B) ? 1'b1 : 1'b0;

endmodule

Mt2015 q4a

module top_module (input x, input y, output z);

assign z = (x^y) & x;

endmodule

Mt2015 q4b

module top_module ( input x, input y, output z );

assign z = ~(x ^ y);

endmodule

Mt2015 q4

module top_module (input x, input y, output z);

wire wire1,wire2;

assign wire1 = ((x^y) & x) | (~(x ^ y));

assign wire2 = ((x^y) & x) & (~(x ^ y));

assign z = wire1 ^ wire2;

endmodule

Ringer

module top_module (

input ring,

input vibrate_mode,

output ringer, // Make sound

output motor // Vibrate

);

assign ringer = ring & ~vibrate_mode;

assign motor = ring & vibrate_mode;

endmodule

Thermostat

module top_module (

input too_cold,

input too_hot,

input mode,

input fan_on,

output heater,

output aircon,

output fan

);

assign heater = too_cold & mode;

assign aircon = too_hot & ~mode;

assign fan = fan_on | (too_cold & mode) | (too_hot & ~mode);

endmodule

Popcount3

module top_module(

input [2:0] in,

output [1:0] out );

assign out = in[0] + in[1] + in[2];

endmodule

/*

module top_module (

input [2:0] in,

output [1:0] out

);

// This is a function of 3 inputs. One method is to use a 8-entry truth table:

// in[2:0] out[1:0]

// 000 00

// 001 01

// 010 01

// 011 10

// 100 01

// 101 10

// 110 10

// 111 11

assign out[0] = (~in[2] & ~in[1] & in[0]) | (~in[2] & in[1] & ~in[0]) | (in[2] & ~in[1] & ~in[0]) | (in[2] & in[1] & in[0]);

assign out[1] = (in[1] & in[0]) | (in[2] & in[0]) | (in[2] & in[1]);

// Using the addition operator works too:

// assign out = in[0]+in[1]+in[2];

// Yet another method uses behavioural code inside a procedure (combinational always block)

// to directly implement the truth table:

always @(*) begin

case (in)

3'd0: out = 2'd0;

3'd1: out = 2'd1;

3'd2: out = 2'd1;

3'd3: out = 2'd2;

3'd4: out = 2'd1;

3'd5: out = 2'd2;

3'd6: out = 2'd2;

3'd7: out = 2'd3;

endcase

end

endmodule

*/

Gatesv

module top_module(

input [3:0] in,

output [2:0] out_both,

output [3:1] out_any,

output [3:0] out_different );

assign out_both = in[2:0] & in[3:1];

assign out_any = in[3:1] | in[2:0];

assign out_different = in[3:0] ^ {in[0],in[3:1]};

endmodule

Gatesv100

module top_module(

input [99:0] in,

output [98:0] out_both,

output [99:1] out_any,

output [99:0] out_different );

assign out_both = in[98:0] & in[99:1];

assign out_any = in[99:1] | in[98:0];

assign out_different = in[99:0] ^ {in[0],in[99:1]};

endmodule

Multiplexers

Mux2to1

module top_module(

input a, b, sel,

output out );

assign out = (sel) ? b : a;

endmodule

Mux2to1v

module top_module(

input [99:0] a, b,

input sel,

output [99:0] out );

assign out = (sel) ? b : a;

endmodule

Mux9to1v

module top_module(

input [15:0] a, b, c, d, e, f, g, h, i,

input [3:0] sel,

output reg [15:0] out );

always @( *) begin

case (sel)

4'd0:out = a;

4'd1:out = b;

4'd2:out = c;

4'd3:out = d;

4'd4:out = e;

4'd5:out = f;

4'd6:out = g;

4'd7:out = h;

4'd8:out = i;

default :

out = 16'b1111_1111_1111_1111;

endcase

end

endmodule

Mux256to1

module top_module(

input [255:0] in,

input [7:0] sel,

output reg out );

integer i;

always @( *) begin

i = sel;

out = in[i];

end

endmodule

/*

module top_module (

input [255:0] in,

input [7:0] sel,

output out

);

// Select one bit from vector in[]. The bit being selected can be variable.

assign out = in[sel];

endmodule

*/

Mux256to1v

module top_module(

input [1023:0] in,

input [7:0] sel,

output [3:0] out );

assign out = in[(4*sel)+:4];

/*

integer i;

always @( *) begin

i = sel;

out = in[(4*i)+:4];

end

big_vect[0 +:8]和big_vect [7:0]是等价的

big_vect[15 -:8]和big_vect[15:8]是等价的。

同时这里的0和15可以为变量,如果不采用这种写法,常用的[a:b]这种形式,a,b必须为常数,不能是一个变量

*/

endmodule

Arithmetic Circuits

Hadd

module top_module(

input a, b,

output cout, sum );

assign sum = a ^b;

assign cout = a & b;

endmodule

Fadd

module top_module(

input a, b, cin,

output cout, sum );

assign sum = a ^ b ^ cin;

assign cout = (a & b) | (a & cin) | (cin & b);

endmodule

Adder3

module top_module(

input [2:0] a, b,

input cin,

output [2:0] cout,

output [2:0] sum );

genvar i;

generate

for( i=0; i<=2; i=i+1) begin:add

if (i == 0) begin

assign sum[i] = a[i] ^ b[i] ^ cin;

assign cout[i] = a[i]&b[i] | a[i]&cin | b[i]&cin;

end

else

begin

assign sum[i] = a[i] ^ b[i]^ cout[i-1];

assign cout[i] = a[i]&b[i] | a[i]&cout[i-1] | b[i]&cout[i-1];

end

end

endgenerate

endmodule

m2014 q4j

module top_module (

input [3:0] x,

input [3:0] y,

output [4:0] sum);

wire [3:0] cout;

genvar i;

generate

for( i=0; i<=3; i=i+1) begin:add

if (i == 0) begin

assign sum[i] = x[i] ^ y[i];

assign cout[i] = x[i]&y[i] ;

end

else

begin

assign sum[i] = x[i] ^ y[i]^ cout[i-1];

assign cout[i] = x[i]&y[i] | x[i]&cout[i-1] | y[i]&cout[i-1];

end

end

endgenerate

assign sum[4] = cout[3];

endmodule

ece241 2014 q1c

module top_module (

input [7:0] a,

input [7:0] b,

output [7:0] s,

output overflow

); //

// assign s = ...

// assign overflow = ...

wire [7:0] cout;

genvar i;

generate

for( i=0; i<=7; i=i+1) begin:add

if (i == 0) begin

assign s[i] = a[i] ^ b[i];

assign cout[i] = a[i]&b[i] ;

end

else

begin

assign s[i] = a[i] ^ b[i]^ cout[i-1];

assign cout[i] = a[i]&b[i] | a[i]&cout[i-1] | b[i]&cout[i-1];

end

end

endgenerate

assign overflow = (cout[6] ^ cout[7]) ? 1'b1 : 1'b0;

endmodule

/*

补码加减法运算,如何判断溢出?

溢出用OF(overflow)表示:当OF=1时溢出;OF=0时,未溢出

m表示符号位是否进位(进位为1,否则为0)

n表示最高数值位是否进位(进位为1,否则为0)

*/

Adder100

module top_module(

input [99:0] a, b,

input cin,

output cout,

output [99:0] sum );

wire [99:0] cout1;

genvar i;

generate

for( i=0; i<=99; i=i+1) begin:add

if (i == 0) begin

assign sum[i] = a[i] ^ b[i] ^ cin;

assign cout1[i] = a[i]&b[i] | a[i]&cin | cin&b[i];

end

else

begin

assign sum[i] = a[i] ^ b[i]^ cout1[i-1];

assign cout1[i] = a[i]&b[i] | a[i]&cout1[i-1] | b[i]&cout1[i-1];

end

end

endgenerate

assign cout = cout1[99];

endmodule

/*看到这个我人麻了,这就是思维固化吗?

module top_module (

input [99:0] a,

input [99:0] b,

input cin,

output cout,

output [99:0] sum

);

// The concatenation {cout, sum} is a 101-bit vector.

assign {cout, sum} = a+b+cin;

endmodule

*/

Bcdadd4

module top_module(

input [15:0] a, b,

input cin,

output cout,

output [15:0] sum );

//题目说可以例化一个BCD加法器

wire [3:0] cout1;

bcd_fadd u_bcd_fadd(

.a(a[3:0]),

.b(b[3:0]),

.cin(cin),

.cout(cout1[0]),

.sum(sum[3:0])

);

genvar i;

generate

for (i = 1;i<=3 ; i=i+1) begin:bcdadd

bcd_fadd u_bcd_fadd(

.a(a[(4*i)+:4]),

.b(b[(4*i)+:4]),

.cin(cout1[i-1]),

.cout(cout1[i]),

.sum(sum[(4*i)+:4])

);

end

endgenerate

assign cout = cout1[3];

/*

//尝试自己写一个BCD加法器

wire [3:0] cout1;

assign sum[3:0] = ((a[3:0] + a[3:0] + cin) >= 10) ? (a[3:0] + b[3:0] + cin - 4'd10) : (a[3:0] + b[3:0] + cin);

assign cout1[0] = ((a[3:0] + b[3:0] + cin) >= 10) ? 1'b1 : 1'b0;

genvar i;

generate

for (i = 1;i<=3 ; i=i+1) begin:bcdadd

assign sum[(4*i)+:4] = ((a[(4*i)+:4] + b[(4*i)+:4] + cout1[i-1]) >= 10) ? (a[(4*i)+:4] + b[(4*i)+:4] + cout1[i-1] - 4'd10) : (a[(4*i)+:4] + b[(4*i)+:4] + cout1[i-1]);

assign cout1[i] = ((a[(4*i)+:4] + b[(4*i)+:4] + cout1[i-1]) >= 10) ? 1'b1 : 1'b0;

end

endgenerate

assign cout = cout1[3];

*/

endmodule

Karnaugh Map to Circuit

Kmap1

module top_module(

input a,

input b,

input c,

output out );

assign out = a&~b | ~b&c | b;

endmodule

Kmap2

module top_module(

input a,

input b,

input c,

input d,

output out );

assign out = ~a&~d | a&~b&~c | ~b&~c&d | a&c&d | ~a&b&c;

endmodule

Kmap3

module top_module(

input a,

input b,

input c,

input d,

output out );

assign out = a | ~a&~b&c;

endmodule

Kmap4

module top_module(

input a,

input b,

input c,

input d,

output out );

assign out = ~a&b&~c&~d | a&~b&~c&~d | ~a&~b&~c&d | a&b&~c&d | ~a&b&c&d | a&~b&c&d | ~a&~b&c&~d | a&b&c&~d ;

endmodule

ece241 2013 q2

module top_module (

input a,

input b,

input c,

input d,

output out_sop,

output out_pos

);

//最小项的反是最大项,最大项的反是最小项。最常用的是最小项。

assign out_sop = c&d | ~a&~b&c;

assign out_pos = ~((~c|~d) & (a|b|~c));

endmodule

m2014 q3

module top_module (

input [4:1] x,

output f );

assign f = ~x[1]&x[3] | x[1]&x[2]&x[4];

endmodule

2012 q1g

module top_module (

input [4:1] x,

output f

);

assign f = ~x[2]&~x[3]&~x[4] | ~x[1]&x[3] | x[1]&x[2]&x[3]&x[4] | x[1]&~x[2]&x[3]&~x[4];

endmodule

ece241 2014 q3

module top_module (

input c,

input d,

output [3:0] mux_in

);

assign mux_in[0] = ~c&d | c&d | c&~d;

assign mux_in[1] = 1'b0;

assign mux_in[3] = c&d;

assign mux_in[2] = ~c&~d | c&~d;

endmodule

Sequential Logic

Latches and Flip-Flops

Dff

module top_module (

input clk, // Clocks are used in sequential circuits

input d,

output reg q );//

// Use a clocked always block

// copy d to q at every positive edge of clk

// Clocked always blocks should use non-blocking assignments

always @(posedge clk) begin

q <= d;

end

endmodule

Dff8

module top_module (

input clk,

input [7:0] d,

output reg [7:0] q

);

always @(posedge clk) begin

q <= d;

end

endmodule

Dff8r

module top_module (

input clk,

input reset, // Synchronous reset

input [7:0] d,

output reg [7:0] q

);

always @(posedge clk ) begin

if (reset) begin

q <= 8'b0;

end

else

q <= d;

end

endmodule

Dff8p

module top_module (

input clk,

input reset,

input [7:0] d,

output reg [7:0] q

);

always @(negedge clk) begin

if (reset) begin

q <= 8'h34;

end

else

q <= d;

end

endmodule

Dff8ar

module top_module (

input clk,

input areset, // active high asynchronous reset

input [7:0] d,

output reg [7:0] q

);

always @(posedge clk or posedge areset) begin

if (areset) begin

q <= 8'b0;

end

else

q <= d;

end

endmodule

Dff16e

module top_module (

input clk,

input resetn,

input [1:0] byteena,

input [15:0] d,

output reg [15:0] q

);

always @(posedge clk) begin

if (!resetn) begin

q <= 16'b0;

end

else

begin

case (byteena)

2'b00:

q <= q;

2'b01:

q <= {q[15:8],d[7:0]};

2'b10:

q <= {d[15:8],q[7:0]};

2'b11:

q <= d;

endcase

end

end

endmodule

m2014 q4a

module top_module (

input d,

input ena,

output reg q);

always @( *) begin

if (ena) begin

q <= d;

end

else

q <= q;

end

endmodule

m2014 q4b

module top_module (

input clk,

input d,

input ar, // asynchronous reset

output reg q);

always @(posedge clk or posedge ar) begin

if (ar) begin

q <= 1'b0;

end

else

q <= d;

end

endmodule

m2014 q4c

module top_module (

input clk,

input d,

input r, // synchronous reset

output reg q);

always @(posedge clk) begin

if (r) begin

q <= 1'b0;

end

else

q <= d;

end

endmodule

m2014 q4d

module top_module (

input clk,

input in,

output reg out);

wire d;

assign d = in ^ out;

always @(posedge clk) begin

out <= d;

end

endmodule

Mt2015 muxdff

module top_module (

input clk,

input L,

input r_in,

input q_in,

output reg Q);

always @(posedge clk) begin

if (L) begin

Q <= r_in;

end

else

Q <= q_in;

end

endmodule

2014 q4a

module top_module (

input clk,

input w, R, E, L,

output reg Q

);

always @(posedge clk) begin

if (L) begin

Q <= R;

end

else

begin

if (E) begin

Q <= w;

end

else

Q <= Q;

end

end

endmodule

ece241 2014 q4

module top_module (

input clk,

input x,

output z

);

reg [2:0] Q;

always @(posedge clk) begin

Q[0] <= x ^ Q[0];

Q[1] <= x & ~Q[1];

Q[2] <= x | ~Q[2];

end

assign z = ~| Q;

endmodule

ece241 2013 q7

module top_module (

input clk,

input j,

input k,

output reg Q);

always @(posedge clk) begin

if (j) begin

if (k) begin

Q <= ~Q;

end

else

Q <= 1'b1;

end

else

begin

if (k) begin

Q <= 1'b0;

end

else

Q <= Q;

end

end

endmodule

Edgedetect

module top_module (

input clk,

input [7:0] in,

output reg [7:0] pedge

);

reg [7:0] in1;

always @(posedge clk) begin

in1 <= in;

end

always @(posedge clk) begin

for (integer i = 0;i<=7 ;i = i+1 ) begin

if ((in[i] == 1'b1) && (in1[i] == 1'b0)) begin

pedge[i] <= 1'b1;

end

else

pedge[i] <= 1'b0;

end

end

endmodule

/*

module top_module(

input clk,

input [7:0] in,

output reg [7:0] pedge);

reg [7:0] d_last;

always @(posedge clk) begin

d_last <= in; // Remember the state of the previous cycle

pedge <= in & ~d_last; // A positive edge occurred if input was 0 and is now 1.

end

endmodule

*/

Edgedetect2

module top_module (

input clk,

input [7:0] in,

output reg [7:0] anyedge

);

reg [7:0] last_in;

always @(posedge clk) begin

last_in <= in;

end

always @(posedge clk) begin

anyedge <= in ^ last_in;

end

endmodule

Edgecapture

module top_module (

input clk,

input reset,

input [31:0] in,

output reg [31:0] out

);

reg [31:0] in1;

always @(posedge clk) begin

in1 <= in;

end

always @(posedge clk) begin

if (reset) begin

out <= 32'b0;

end

else

out <= ~in & in1 | out;//可以利用或运算来保持out输出1之后一直保持不变,同样的道理如果想保持输出的0不变可以使用and

end

endmodule

/*

reg [31:0] in1;

wire [31:0] out1;

always @(posedge clk) begin

in1 <= in;

end

assign out1 = ~in & in1;

always @(posedge clk) begin

if (reset) begin

out <= 32'b0;

end

else

begin

for ( integer i=0 ;i<=31 ;i=i+1 ) begin

if (out1[i]) begin

out[i] <= 1'b1;

end

end

end

end

*/

Dualedge

module top_module (

input clk,

input d,

output q

);

reg q_d1;

reg q_d2;

always@(posedge clk)begin

q_d1 <= d ^ q_d2;

end

always@(negedge clk)begin

q_d2 <= d ^ q_d1;

end

assign q = q_d1 ^ q_d2;

//上升沿和下降沿交替触发,使两个寄存器交替变化,最后用异或来输出q,这个题目感觉有难度。

//原文链接:https://blog.csdn.net/wangkai_2019/article/details/106238994

endmodule

Counters

Count15

module top_module (

input clk,

input reset, // Synchronous active-high reset

output reg [3:0] q);

always @(posedge clk) begin

if (reset) begin

q <= 4'b0;

end

else if (q == 4'd15) begin

q <= 4'b0;

end

else

q <= q + 1'b1;

end

endmodule

/*

module top_module(

input clk,

input reset,

output reg [3:0] q);

always @(posedge clk)

if (reset)

q <= 0;

else

q <= q+1; // Because q is 4 bits, it rolls over from 15 -> 0.

// If you want a counter that counts a range different from 0 to (2^n)-1,

// then you need to add another rule to reset q to 0 when roll-over should occur.

endmodule

*/

Count10

module top_module (

input clk,

input reset, // Synchronous active-high reset

output reg [3:0] q);

always @(posedge clk) begin

if (reset) begin

q <= 4'b0;

end

else if(q == 4'd9) begin

q <= 4'b0;

end

else

q <= q +1'b1;

end

endmodule

Count1to10

module top_module (

input clk,

input reset,

output reg [3:0] q);

always @(posedge clk) begin

if (reset) begin

q <= 4'b1;

end

else if(q == 4'd10) begin

q <= 4'b1;

end

else

q <= q + 1'b1;

end

endmodule

Countslow

module top_module (

input clk,

input slowena,

input reset,

output reg [3:0] q);

always @(posedge clk) begin

if (reset) begin

q <= 4'b0;

end

else if(slowena) begin

q <= q + 1'b1;

if(q == 4'd9) begin

q <= 4'b0;

end

end

else

q <= q;

end

endmodule

ece241 2014 q7a

module top_module (

input clk,

input reset,

input enable,

output [3:0] Q,

output c_enable,

output c_load,

output [3:0] c_d

); //

wire load1;

assign load1 = (((Q == 4'd12)&enable) || (reset) ) ? 1'b1 : 1'b0;

//一定要注意,是在计数到12,并且使能状态之下才可以重装载

count4 the_counter (

.clk(clk),

.enable(enable),

.load(load1),

.d(4'b1),

.Q(Q)

);

assign c_enable = enable;

assign c_load = load1;

assign c_d = 4'b1;

endmodule

ece241 2014 q7b

module top_module (

input clk,

input reset,

output reg OneHertz,

output reg [2:0] c_enable

); //

reg [3:0] q0,q1,q2;

always @( *) begin

c_enable[0] <= 1'b1;

end

always @(posedge clk) begin

if (q0 == 4'd8) begin

c_enable[1] <= 1'b1;

end

else

c_enable[1] <= 1'b0;

end

always @(posedge clk) begin

if ((q1 == 4'd9) && (q0 == 4'd8)) begin

c_enable[2] <= 1'b1;

end

else

c_enable[2] <= 1'b0;

end

bcdcount count1(

.clk(clk),

.reset(reset),

.enable(c_enable[0]),

.Q(q0)

);

bcdcount count2(

.clk(clk),

.reset(reset),

.enable(c_enable[1]),

.Q(q1)

);

bcdcount count3(

.clk(clk),

.reset(reset),

.enable(c_enable[2]),

.Q(q2)

);

always @(posedge clk) begin

if ((q2 == 4'd9) && (q1 == 4'd9) && (q0 == 4'd8)) begin

OneHertz <= 1'b1;

end

else

OneHertz <= 1'b0;

end

//用always就会延迟一个时钟,所以要到998,如果用assign的话就不会延时,所以可以写到999

//因为要求每个计数器的时钟都是同一时钟,所以使能位就担任起不同时钟的作用了

endmodule

Countbcd

module top_module (

input clk,

input reset, // Synchronous active-high reset

output [3:1] ena,

output reg [15:0] q);

wire [3:0] ena1;

assign ena1[0] = 1'b1;

always @(posedge clk) begin

if (reset) begin

q[3:0] <= 4'b0;

end

else if (ena1[0]) begin

if(q[3:0] == 4'd9) begin

q[3:0] <= 4'b0;

end

else

q[3:0] <= q[3:0] +1'b1;

end

end

assign ena1[1] = (q[3:0] == 4'd9) ? 1'b1 : 1'b0;

always @(posedge clk) begin

if (reset) begin

q[7:4] <= 4'b0;

end

else if (ena1[1]) begin

if(q[7:4] == 4'd9) begin

q[7:4] <= 4'b0;

end

else

q[7:4] <= q[7:4] +1'b1;

end

end

assign ena1[2] = ((q[3:0] == 4'd9) && (q[7:4] == 4'd9)) ? 1'b1 : 1'b0;

always @(posedge clk) begin

if (reset) begin

q[11:8] <= 4'b0;

end

else if (ena1[2]) begin

if(q[11:8] == 4'd9) begin

q[11:8] <= 4'b0;

end

else

q[11:8] <= q[11:8] +1'b1;

end

end

assign ena1[3] = ((q[3:0] == 4'd9) && (q[7:4] == 4'd9) && (q[11:8] == 4'd9)) ? 1'b1 : 1'b0;

always @(posedge clk) begin

if (reset) begin

q[15:12] <= 4'b0;

end

else if (ena1[3]) begin

if(q[15:12] == 4'd9) begin

q[15:12] <= 4'b0;

end

else

q[15:12] <= q[15:12] +1'b1;

end

end

assign ena = ena1[3:1];

//

endmodule

Count clock

module top_module(

input clk,

input reset,

input ena,

output reg pm,

output [7:0] hh,

output [7:0] mm,

output [7:0] ss);

wire ss_en,ss_60_en; //秒个位进十位的进位脉冲,秒记满59的时候产生进位分钟的脉冲

reg [3:0] ss_one,ss_ten; //秒的个位和十位 ,以下类推

wire mm_en,mm_60_en;

reg [3:0] mm_one,mm_ten;

wire hh_en,pm_en; //产生AM PM交换时产生的脉冲,到11点59分59秒的时候产生一个脉冲,使pm取反

reg [3:0] hh_one,hh_ten;

assign ss = {ss_ten,ss_one};

assign mm = {mm_ten,mm_one};

assign hh = {hh_ten,hh_one};

always @(posedge clk) begin

if (reset) begin

ss_one <= 4'b0;

end

else if(ena) begin

if (ss_one == 4'd9) begin

ss_one <= 4'b0;

end

else

ss_one <= ss_one + 1'b1;

end

end

assign ss_en = ((ss_one == 4'd9) && ena) ? 1'b1 : 1'b0;

always @(posedge clk) begin

if (reset) begin

ss_ten <= 4'b0;

end

else if(ss_en) begin

if ((ss_one == 4'd9) && (ss_ten == 4'd5) && ena) begin

ss_ten <= 4'b0;

end

else

ss_ten <= ss_ten + 1'b1;

end

end

assign ss_60_en = ((ss_one == 4'd9) && (ss_ten == 4'd5) && ena) ? 1'b1 : 1'b0;

always @(posedge clk) begin

if (reset) begin

mm_one <= 4'b0;

end

else if(ss_60_en) begin

if (mm_one == 4'd9) begin

mm_one <= 4'b0;

end

else

mm_one <= mm_one + 1'b1;

end

end

assign mm_en = ((mm_one == 4'd9) && (ss_one == 4'd9) && (ss_ten == 4'd5) && ena) ? 1'b1 : 1'b0;

always @(posedge clk) begin

if (reset) begin

mm_ten <= 4'b0;

end

else if(mm_en) begin

if ((mm_one == 4'd9) && (mm_ten == 4'd5) && ena && (ss_one == 4'd9) && (ss_ten == 4'd5)) begin

mm_ten <= 4'b0;

end

else

mm_ten <= mm_ten + 1'b1;

end

end

assign mm_60_en = ((mm_one == 4'd9) && (mm_ten == 4'd5) && ena && (ss_one == 4'd9) && (ss_ten == 4'd5)) ? 1'b1 : 1'b0;

always @(posedge clk) begin

if (reset) begin

hh_one <= 4'd2;

end

else if(mm_60_en) begin

if ((hh_one == 4'd2) && (hh_ten == 4'd1) && (mm_one == 4'd9) && (mm_ten == 4'd5) && ena && (ss_one == 4'd9) && (ss_ten == 4'd5)) begin

hh_one <= 4'd1;

end

else if ((hh_one == 4'd9) && (hh_ten == 4'd0) && (mm_one == 4'd9) && (mm_ten == 4'd5) && ena && (ss_one == 4'd9) && (ss_ten == 4'd5)) begin

hh_one <= 4'd0;

end

else

hh_one <= hh_one + 1'b1;

end

end

assign hh_en = ((hh_one == 4'd9) && (hh_ten == 4'd0) && (mm_one == 4'd9) && (mm_ten == 4'd5) && ena && (ss_one == 4'd9) && (ss_ten == 4'd5)) ? 1'b1 : 1'b0;

always @(posedge clk) begin

if (reset) begin

hh_ten <= 4'b1;

end

else if ((hh_one == 4'd2) && (hh_ten == 4'd1) && (mm_one == 4'd9) && (mm_ten == 4'd5) && ena && (ss_one == 4'd9) && (ss_ten == 4'd5)) begin

hh_ten <= 4'd0;

end

else if(hh_en) begin

hh_ten <= 4'd1;

end

end

assign pm_en = ((hh_one == 4'd1) && (hh_ten == 4'd1) && (mm_one == 4'd9) && (mm_ten == 4'd5)&& (ss_one == 4'd9) && (ss_ten == 4'd5) && ena) ? 1'b1 : 1'b0;

always @(posedge clk) begin

if (reset) begin

pm <= 1'b0;

end

else if (pm_en) begin

pm <= ~pm;

end

end

//注意在产生进位脉冲的时候,要考虑到最小单位的进位,比如在判断分钟的进位时,要等到秒计数到59的时候才产生进位脉冲

endmodule

Shift Registers

Shift4

module top_module(

input clk,

input areset, // async active-high reset to zero

input load,

input ena,

input [3:0] data,

output reg [3:0] q);

always @(posedge clk or posedge areset) begin

if (areset) begin

q <= 4'b0;

end

else if (load) begin

q <= data;

end

else if (ena) begin

q <= {1'b0,q[3:1]};

end

end

endmodule

Rotate100

module top_module(

input clk,

input load,

input [1:0] ena,

input [99:0] data,

output reg [99:0] q);

always @(posedge clk) begin

if (load) begin

q <= data;

end

else

begin

case (ena)

2'b01:q <= {q[0],q[99:1]};

2'b10:q <= {q[98:0],q[99]};

default :

q <= q;

endcase

end

end

endmodule

Shift18

module top_module(

input clk,

input load,

input ena,

input [1:0] amount,

input [63:0] data,

output reg [63:0] q);

always @(posedge clk) begin

if (load) begin

q <= data;

end

else if(ena) begin

case (amount)

2'b00:q <= {q[62:0],1'b0};

2'b01:q <= {q[55:0],8'b0};

2'b10:q <= {q[63],q[63:1]};

2'b11:q <= {{8{q[63]}},q[63:8]};

endcase

end

else

q <= q;

end

endmodule

Lfsr5

module top_module(

input clk,

input reset, // Active-high synchronous reset to 5'h1

output reg [4:0] q

);

always @(posedge clk) begin

if (reset) begin

q <= 5'h1;

end

else

begin

q[4] <= 0 ^ q[0];

q[3] <= q[4];

q[2] <= q[3] ^ q[0];

q[1] <= q[2];

q[0] <= q[1];

end

end

endmodule

/*

线性反馈移位寄存器(英语:Linear feedback shift register,LFSR)

module top_module(

input clk,

input reset,

output reg [4:0] q);

reg [4:0] q_next; // q_next is not a register

Convenience: Create a combinational block of logic that computes

what the next value should be. For shorter code, I first shift

all of the values and then override the two bit positions that have taps.

A logic synthesizer creates a circuit that behaves as if the code were

executed sequentially, so later assignments override earlier ones.

Combinational always block: Use blocking assignments.

逻辑合成器创建的电路就像代码一样顺序执行,所以后面的赋值会覆盖前面的赋值。

always @(*) begin

q_next = q[4:1]; // Shift all the bits. This is incorrect for q_next[4] and q_next[2],左边5位,右边4位,则会赋值给4个低位,高位为0

q_next[4] = q[0]; // Give q_next[4] and q_next[2] their correct assignments

q_next[2] = q[3] ^ q[0];

end

在 assign 赋值操作中,如果等号左右两侧信号的位宽不同,那么就会进行截断或者补零操作。

左侧信号位宽大于右侧信号位宽,右值的低位赋予左值对应的低位,左值高位的部分赋零。

左侧信号位宽小于右侧信号位宽,右值的低位赋予左值对应的低位,右值高位的部分直接被截断。即保留右值的低位。

This is just a set of DFFs. I chose to compute the connections between the

DFFs above in its own combinational always block, but you can combine them if you wish.

You'll get the same circuit either way.

Edge-triggered always block: Use non-blocking assignments.

always @(posedge clk) begin

if (reset)

q <= 5'h1;

else

q <= q_next;

end

endmodule

*/

Mt2015 lfsr

module top_module (

input [2:0] SW, // R

input [1:0] KEY, // L and clk

output [2:0] LEDR); // Q

reg [2:0] Q;

wire [2:0] R;

assign LEDR = Q;

assign R = SW;

always @(posedge KEY[0]) begin

if (KEY[1]) begin

Q[0] <= R[0];

Q[1] <= R[1];

Q[2] <= R[2];

end

else

begin

Q[0] <= Q[2];

Q[1] <= Q[0];

Q[2] <= Q[2] ^ Q[1];

end

end

endmodule

Lfsr32

module top_module(

input clk,

input reset, // Active-high synchronous reset to 32'h1

output reg [31:0] q

);

reg [31:0] q_next;

always @(*) begin

q_next = q[31:1];

q_next[31] = q[0];//这是32抽头,和0异或

q_next[0] = q[0] ^ q[1];

q_next[1] = q[0] ^ q[2];

q_next[21] = q[0] ^ q[22];

end

always @(posedge clk) begin

if (reset) begin

q <= 32'h1;

end

else

q <= q_next;

end

endmodule

m2014 q4k

module top_module (

input clk,

input resetn, // synchronous reset

input in,

output out);

reg [3:0] Q;

always @(posedge clk) begin

if (!resetn) begin

Q <= 4'b0;

end

else

begin

Q[0] <= in;

Q[1] <= Q[0];

Q[2] <= Q[1];

Q[3] <= Q[2];

end

end

assign out = Q[3];

endmodule

/*

module top_module (

input clk,

input resetn,

input in,

output out

);

reg [3:0] sr;

// Create a shift register named sr. It shifts in "in".

always @(posedge clk) begin

if (~resetn) // Synchronous active-low reset

sr <= 0;

else

sr <= {sr[2:0], in};

end

assign out = sr[3]; // Output the final bit (sr[3])

endmodule

*/

2014 q4b

module top_module (

input [3:0] SW,

input [3:0] KEY,

output [3:0] LEDR

); //

wire [3:0] R;

wire clk,E,L,W;

reg [3:0] Q;

assign R = SW;

assign clk = KEY[0];

assign E = KEY[1];

assign L = KEY[2];

assign W = KEY[3];

assign LEDR = Q;

MUXDFF MUXDFF_1(

.clk(clk),

.w(W),

.R(R[3]),

.E(E),

.L(L),

.Q(Q[3])

);

MUXDFF MUXDFF_2(

.clk(clk),

.w(Q[3]),

.R(R[2]),

.E(E),

.L(L),

.Q(Q[2])

);

MUXDFF MUXDFF_3(

.clk(clk),

.w(Q[2]),

.R(R[1]),

.E(E),

.L(L),

.Q(Q[1])

);

MUXDFF MUXDFF_4(

.clk(clk),

.w(Q[1]),

.R(R[0]),

.E(E),

.L(L),

.Q(Q[0])

);

endmodule

module MUXDFF (

input clk,

input w, R, E, L,

output reg Q

);

always @(posedge clk) begin

if (L) begin

Q <= R;

end

else

begin

if (E) begin

Q <= w;

end

else

Q <= Q;

end

end

endmodule

ece241 2013 q12

module top_module (

input clk,

input enable,

input S,

input A, B, C,

output reg Z );

reg [7:0] Q;

wire[2:0] chose;

assign chose = {A,B,C};

always @(posedge clk) begin

if (enable) begin

Q <= {Q[6:0],S};

end

end

always @(*) begin

case (chose)

3'd0: Z = Q[0];

3'd1: Z = Q[1];

3'd2: Z = Q[2];

3'd3: Z = Q[3];

3'd4: Z = Q[4];

3'd5: Z = Q[5];

3'd6: Z = Q[6];

3'd7: Z = Q[7];

default :

Z = 1'b0;

endcase

end

endmodule

/*

module top_module (

input clk,

input enable,

input S,

input A, B, C,

output reg Z

);

reg [7:0] q;

// The final circuit is a shift register attached to a 8-to-1 mux.

// Create a 8-to-1 mux that chooses one of the bits of q based on the three-bit number {A,B,C}:

// There are many other ways you could write a 8-to-1 mux

// (e.g., combinational always block -> case statement with 8 cases).

assign Z = q[ {A, B, C} ];//妙哉

// Edge-triggered always block: This is a standard shift register (named q) with enable.

// When enabled, shift to the left by 1 (discarding q[7] and and shifting in S).

always @(posedge clk) begin

if (enable)

q <= {q[6:0], S};

end

endmodule

*/

More Circuits

Rule90

module top_module(

input clk,

input load,

input [511:0] data,

output reg [511:0] q );

wire [511:0] q_l,q_r,q_next;

assign q_l = {q[510:0],1'b0};

assign q_r = {1'b0,q[511:1]};

assign q_next = q_l ^ q_r;

always @(posedge clk) begin

if (load) begin

q <= data;

end

else

q <= q_next;

end

endmodule

Rule110

module top_module(

input clk,

input load,

input [511:0] data,

output reg [511:0] q

);

wire [511:0] q_l,q_r,q_next;

assign q_r = {q[510:0],1'b0};

assign q_l = {1'b0,q[511:1]};

assign q_next = ~q_l & q | ~q_l & ~q & q_r | q_l & q & ~q_r | q_l & ~q & q_r;

always @(posedge clk) begin

if (load) begin

q <= data;

end

else

q <= q_next;

end

endmodule

Conwaylife

John Conway, mathematician and creator of the Game of Life cellular automaton, passed away from COVID-19 on April 11, 2020.

module top_module(

input clk,

input load,

input [255:0] data,

output reg [255:0] q );

//做之前应该画画图,看着图做。

reg [2:0] sum;

reg [255:0] q_next;

always @( *) begin

for (integer i= 0;i<=255 ; i = i+1) begin

if (i == 0) begin

sum = q[1]+q[16]+q[15]+q[240]+q[241]+q[31]+q[17]+q[255];

end

else if (i == 15) begin

sum = q[14]+q[255]+q[0]+q[31]+q[254]+q[240]+q[16]+q[30];

end

else if (i == 240) begin

sum = q[224]+q[241]+q[0]+q[255]+q[225]+q[239]+q[1]+q[15];

end

else if (i == 255) begin

sum = q[254]+q[239]+q[240]+q[15]+q[238]+q[224]+q[14]+q[0];

end

else if (i%16 == 0) begin

sum = q[i+1]+q[i+15]+q[i+16]+q[i+17]+q[i+31]+q[i-16]+q[i-15]+q[i-1];

end

else if (i%16 == 15) begin

sum = q[i-1]+q[i-15]+q[i+16]+q[i+15]+q[i+1]+q[i-16]+q[i-17]+q[i-31];

end

else if ((i>=241) && (i<=254)) begin

sum = q[i-1]+q[i+1]+q[i-16]+q[i-17]+q[i-15]+q[i-240]+q[i-241]+q[i-239];

end

else if ((i>=1) && (i<=14)) begin

sum = q[i-1]+q[i+1]+q[i+16]+q[i+15]+q[i+17]+q[i+240]+q[i+241]+q[i+239];

end

else

sum = q[i-1]+q[i+1]+q[i-16]+q[i-15]+q[i-17]+q[i+16]+q[i+15]+q[i+17];

case (sum)

3'd0:q_next[i] = 1'b0;

3'd1:q_next[i] = 1'b0;

3'd2:q_next[i] = q[i];

3'd3:q_next[i] = 1'b1;

default:

q_next[i] = 1'b0;

endcase

end

end

always @(posedge clk) begin

if (load) begin

q <= data;

end

else

q <= q_next;

end

endmodule

Finite State Machines

Fsm1

module top_module(

input clk,

input areset, // Asynchronous reset to state B

input in,

output out);//

parameter A=0, B=1;

reg state, next_state;

always @(*) begin // This is a combinational always block

// State transition logic

case (state)

A:

begin

if (in == 1'b0) begin

next_state = B;

end

else

next_state = A;

end

B:

begin

if (in == 1'b0) begin

next_state = A;

end

else

next_state = B;

end

endcase

end

always @(posedge clk, posedge areset) begin // This is a sequential always block

// State flip-flops with asynchronous reset

if (areset) begin

state <= B;

end

else

state <= next_state;

end

// Output logic

// assign out = (state == ...);

assign out = (state == B) ? 1'b1 : 1'b0;

endmodule

/*

module top_module (

input clk,

input in,

input areset,

output out

);

// Give state names and assignments. I'm lazy, so I like to use decimal numbers.

// It doesn't really matter what assignment is used, as long as they're unique.

parameter A=0, B=1;

reg state; // Ensure state and next are big enough to hold the state encoding.

reg next;

// A finite state machine is usually coded in three parts:

// State transition logic

// State flip-flops

// Output logic

// It is sometimes possible to combine one or more of these blobs of code

// together, but be careful: Some blobs are combinational circuits, while some

// are clocked (DFFs).

// Combinational always block for state transition logic. Given the current state and inputs,

// what should be next state be?

// Combinational always block: Use blocking assignments.

always@(*) begin

case (state)

A: next = in ? A : B;

B: next = in ? B : A;

endcase

end

// Edge-triggered always block (DFFs) for state flip-flops. Asynchronous reset.

always @(posedge clk, posedge areset) begin

if (areset) state <= B; // Reset to state B

else state <= next; // Otherwise, cause the state to transition

end

// Combinational output logic. In this problem, an assign statement is the simplest.

// In more complex circuits, a combinational always block may be more suitable.

assign out = (state==B);

endmodule

*/

Fsm1s

// Note the Verilog-1995 module declaration syntax here:

module top_module(clk, reset, in, out);

input clk;

input reset; // Synchronous reset to state B

input in;

output out;

parameter A=0, B=1;

reg state, next_state;

always @(*) begin // This is a combinational always block

// State transition logic

case (state)

A:

begin

if (in == 1'b0) begin

next_state = B;

end

else

next_state = A;

end

B:

begin

if (in == 1'b0) begin

next_state = A;

end

else

next_state = B;

end

endcase

end

always @(posedge clk) begin // This is a sequential always block

// State flip-flops with asynchronous reset

if (reset) begin

state <= B;

end

else

state <= next_state;

end

// Output logic

// assign out = (state == ...);

assign out = (state == B) ? 1'b1 : 1'b0;

endmodule

/*

// Note the Verilog-1995 module declaration syntax here:

module top_module(clk, reset, in, out);

input clk;

input reset; // Synchronous reset to state B

input in;

output out;//

reg out;

// Fill in state name declarations

reg present_state, next_state;

always @(posedge clk) begin

if (reset) begin

// Fill in reset logic

end else begin

case (present_state)

// Fill in state transition logic

endcase

// State flip-flops

present_state = next_state;

case (present_state)

// Fill in output logic

endcase

end

end

endmodule

*/

Fsm2

module top_module(

input clk,

input areset, // Asynchronous reset to OFF

input j,

input k,

output out); //

parameter OFF=0, ON=1;

reg state, next_state;

always @(*) begin

// State transition logic

case (state)

OFF:

begin

if (j == 1'b1) begin

next_state = ON;

end

else

next_state = state;

end

ON:

begin

if (k == 1'b1) begin

next_state = OFF;

end

else

next_state = state;

end

endcase

end

always @(posedge clk, posedge areset) begin

// State flip-flops with asynchronous reset

if (areset) begin

state <= OFF;

end

else

state <= next_state;

end

// Output logic

// assign out = (state == ...);

assign out = (state == ON);

endmodule

Fsm2s

module top_module(

input clk,

input reset, // Asynchronous reset to OFF

input j,

input k,

output out); //

parameter OFF=0, ON=1;

reg state, next_state;

always @(*) begin

// State transition logic

case (state)

OFF:

begin

if (j == 1'b1) begin

next_state = ON;

end

else

next_state = state;

end

ON:

begin

if (k == 1'b1) begin

next_state = OFF;

end

else

next_state = state;

end

endcase

end

always @(posedge clk) begin

// State flip-flops with asynchronous reset

if (reset) begin

state <= OFF;

end

else

state <= next_state;

end

// Output logic

// assign out = (state == ...);

assign out = (state == ON);

endmodule

Fsm3comb

module top_module(

input in,

input [1:0] state,

output reg [1:0] next_state,

output out); //

parameter A=0, B=1, C=2, D=3;

// State transition logic: next_state = f(state, in)

always @( *) begin

case (state)

A:

begin

case (in)

1'b0:next_state = A;

1'b1:next_state = B;

endcase

end

B:

begin

case (in)

1'b0:next_state = C;

1'b1:next_state = B;

endcase

end

C:

begin

case (in)

1'b0:next_state = A;

1'b1:next_state = D;

endcase

end

D:

begin

case (in)

1'b0:next_state = C;

1'b1:next_state = B;

endcase

end

endcase

end

assign out = (state == D);

// Output logic: out = f(state) for a Moore state machine

endmodule

Fsm3onehot

module top_module(

input in,

input [3:0] state,

output [3:0] next_state,

output out); //

parameter A=0, B=1, C=2, D=3;

// State transition logic: Derive an equation for each state flip-flop.

assign next_state[A] = ~in & (state[A] | state[C]);

assign next_state[B] = in & (state[A] | state[B]| state[D]);

assign next_state[C] = ~in & (state[B] | state[D]);

assign next_state[D] = in & state[C];

// Output logic:

assign out = state[D];

/*本题的关键是理解题目的意思,题目的输入和输出的状态信息都是独热码,需要用逻辑电路的方式来判断下一个状态

独热码可以理解为已经将二进制编码进行译码之后的结果,就像是经过了3-8译码器一样,因此使用独热码可以节约逻辑资源,

但是,独热码会浪费更多的寄存器,因此状态比较少的时候可以使用独热码来节约逻辑资源,提升运行速度*/

endmodule

Fsm3

module top_module(

input clk,

input in,

input areset,

output out); //

reg [4:0] state,next_state;

parameter A=4'b0001,B=4'b0010,C=4'b0100,D=4'b1000;

// State transition logic

always @( *) begin

case (state)

A:next_state = in ? B : A;

B:next_state = in ? B : C;

C:next_state = in ? D : A;

D:next_state = in ? B : C;

/*我的太不简洁了

A:

begin

if (in) begin

next_state = B;

end

else

next_state = A;

end

B:

begin

if (in) begin

next_state = B;

end

else

next_state = C;

end

C:

begin

if (in) begin

next_state = D;

end

else

next_state = A;

end

D:

begin

if (in) begin

next_state = B;

end

else

next_state = C;

end

*/

default : next_state = A;

endcase

end

// State flip-flops with asynchronous reset

always @(posedge clk or posedge areset) begin

if (areset) begin

state <= A;

end

else

state <= next_state;

end

// Output logic

assign out = (state == D) ;

endmodule

/*

module top_module (

input clk,

input in,

input areset,

output out

);

// Give state names and assignments. I'm lazy, so I like to use decimal numbers.

// It doesn't really matter what assignment is used, as long as they're unique.

parameter A=0, B=1, C=2, D=3;

reg [1:0] state; // Make sure state and next are big enough to hold the state encodings.

reg [1:0] next;

// Combinational always block for state transition logic. Given the current state and inputs,

// what should be next state be?

// Combinational always block: Use blocking assignments.

always@(*) begin

case (state)

A: next = in ? B : A;

B: next = in ? B : C;

C: next = in ? D : A;

D: next = in ? B : C;

endcase

end

// Edge-triggered always block (DFFs) for state flip-flops. Asynchronous reset.

always @(posedge clk, posedge areset) begin

if (areset) state <= A;

else state <= next;

end

// Combinational output logic. In this problem, an assign statement is the simplest.

assign out = (state==D);

endmodule

*/

Fsm3s

module top_module(

input clk,

input in,

input reset,

output out); //

reg [4:0] state,next_state;

parameter A=4'b0001,B=4'b0010,C=4'b0100,D=4'b1000;

// State transition logic

always @( *) begin

case (state)

A:next_state = in ? B : A;

B:next_state = in ? B : C;

C:next_state = in ? D : A;

D:next_state = in ? B : C;

default : next_state = A;

endcase

end

// State flip-flops with asynchronous reset

always @(posedge clk) begin

if (reset) begin

state <= A;

end

else

state <= next_state;

end

// Output logic

assign out = (state == D) ;

endmodule

ece241 2013 q4

module top_module (

input clk,

input reset,

input [3:1] s,

output fr3,

output fr2,

output fr1,

output dfr

);

reg [3:0] out;

assign {fr3,fr2,fr1,dfr} = out;

reg [2:0] state,next_state,last_state;

parameter A=3'd1,B=3'd2,C=3'd3,D=3'd4;

always @( *) begin

case (state)

A:

begin

next_state = (s == 3'b011) ? B : A;

if (s == 3'b011) begin

end

end

B:

begin

if (s == 3'b001) begin

next_state = C;

end

else if (s == 3'b111) begin

next_state = A;

end

else

next_state = B;

end

C:

begin

if (s == 3'b000) begin

next_state = D;

end

else if (s == 3'b011) begin

next_state = B;

end

else

next_state = C;

end

D:

begin

next_state = (s == 3'b001) ? C : D;

if (s == 3'b001) begin

end

end

endcase

end

always @(posedge clk) begin

if (reset) begin

state <= D;

end

else

state <= next_state;

end

always @(*) begin

case (state)

A:

begin

out[3:1] = 3'b000;

end

B:

begin

out[3:1] = 3'b001;

end

C:

begin

out[3:1] = 3'b011;

end

D: out[3:1] = 3'b111;

endcase

end

always @(posedge clk) begin

last_state <= state;

end

always @(*) begin

if (((last_state==A) && (state==B)) || ((last_state==B) && (state==C))) begin

out[0] = 1'b1;

end

else if (((last_state==D) && (state==C)) || ((last_state==C) && (state==B))) begin

out[0] = 1'b0;

end

else if (state == D) begin

out[0] = 1'b1;

end

else if (state == A) begin

out[0] = 1'b0;

end

end

endmodule

//本题的关键是dfr的输出,我的想法是通过检测水位到底是由高水位降到低水位还是相反的过程,类似于边沿检测的想法

//题目的答案的想法就非常简洁,直接把高水位和低水位变化过来的当成两个状态,这样就可以直接输出结果,不需要再去判断边沿了,完美

/*

module top_module (

input clk,

input reset,

input [3:1] s,

output reg fr3,

output reg fr2,

output reg fr1,

output reg dfr

);

// Give state names and assignments. I'm lazy, so I like to use decimal numbers.

// It doesn't really matter what assignment is used, as long as they're unique.

// We have 6 states here.

parameter A2=0, B1=1, B2=2, C1=3, C2=4, D1=5;

reg [2:0] state, next; // Make sure these are big enough to hold the state encodings.

// Edge-triggered always block (DFFs) for state flip-flops. Synchronous reset.

always @(posedge clk) begin

if (reset) state <= A2;

else state <= next;

end

// Combinational always block for state transition logic. Given the current state and inputs,

// what should be next state be?

// Combinational always block: Use blocking assignments.

always@(*) begin

case (state)

A2: next = s[1] ? B1 : A2;

B1: next = s[2] ? C1 : (s[1] ? B1 : A2);

B2: next = s[2] ? C1 : (s[1] ? B2 : A2);

C1: next = s[3] ? D1 : (s[2] ? C1 : B2);

C2: next = s[3] ? D1 : (s[2] ? C2 : B2);

D1: next = s[3] ? D1 : C2;

default: next = 'x;

endcase

end

// Combinational output logic. In this problem, a procedural block (combinational always block)

// is more convenient. Be careful not to create a latch.

always@(*) begin

case (state)

A2: {fr3, fr2, fr1, dfr} = 4'b1111;

B1: {fr3, fr2, fr1, dfr} = 4'b0110;

B2: {fr3, fr2, fr1, dfr} = 4'b0111;

C1: {fr3, fr2, fr1, dfr} = 4'b0010;

C2: {fr3, fr2, fr1, dfr} = 4'b0011;

D1: {fr3, fr2, fr1, dfr} = 4'b0000;

default: {fr3, fr2, fr1, dfr} = 'x;

endcase

end

endmodule

*/

Lemmings1

module top_module(

input clk,

input areset, // Freshly brainwashed Lemmings walk left.

input bump_left,

input bump_right,

output walk_left,

output walk_right); //

parameter LEFT=1'b0, RIGHT=1'b1;

reg state, next_state;

always @(*) begin

// State transition logic

case (state)

LEFT:next_state = (bump_left) ? RIGHT : LEFT;

RIGHT:next_state = (bump_right) ? LEFT : RIGHT;

endcase

end

always @(posedge clk, posedge areset) begin

// State flip-flops with asynchronous reset

if (areset) begin

state <= LEFT;

end

else

state <= next_state;

end

// Output logic

assign walk_left = (state == LEFT);

assign walk_right = (state == RIGHT);

endmodule

/*

module top_module (

input clk,

input areset,

input bump_left,

input bump_right,

output walk_left,

output walk_right

);

// Give state names and assignments. I'm lazy, so I like to use decimal numbers.

// It doesn't really matter what assignment is used, as long as they're unique.

parameter WL=0, WR=1;

reg state;

reg next;

// Combinational always block for state transition logic. Given the current state and inputs,

// what should be next state be?

// Combinational always block: Use blocking assignments.

always@(*) begin

case (state)

WL: next = bump_left ? WR : WL;

WR: next = bump_right ? WL : WR;

endcase

end

// Combinational always block for state transition logic. Given the current state and inputs,

// what should be next state be?

// Combinational always block: Use blocking assignments.

always @(posedge clk, posedge areset) begin

if (areset) state <= WL;

else state <= next;

end

// Combinational output logic. In this problem, an assign statement are the simplest.

// In more complex circuits, a combinational always block may be more suitable.

assign walk_left = (state==WL);

assign walk_right = (state==WR);

endmodule

*/

Lemmings2

module top_module(

input clk,

input areset, // Freshly brainwashed Lemmings walk left.

input bump_left,

input bump_right,

input ground,

output walk_left,

output walk_right,

output aaah );

parameter LEFT=2'd0,RIGHT=2'd1,LEFT_FALL=2'd2,RIGHT_FALL=2'd3;

reg [1:0] state,next_state;

always @( *) begin

case (state)

LEFT:

begin

if (!ground) begin

next_state = LEFT_FALL;

end

else if (bump_left) begin

next_state = RIGHT;

end

else