EDA(Quartus II)——正弦信号发生器的设计

目录

实验目的:

实验预习:

实验原理:

定制LPM_ROM模块流程:

1、定制初始化数据文件,建立.mif格式文件

2、定制LPM_ROM元件

3、对生成的文件建工程,编译、仿真,生成rom_1元件。

选学一:仿真ROM元件

实验任务一

实验任务二

选学二:顶层设计的仿真

第一种方法(使用SignalTap II Logic Analyzer)

第二种方法:(用Modelsim仿真)

实验任务三

作业1:

作业2:

实验目的:

进一步熟悉QuartusⅡ及其LPM_ROM与FPGA硬件资源的使用方法。

实验预习:

定制LPM_ROM模块流程。

实验原理:

EDA是电子设计自动化,对象是数字电路设计,而正弦信号发生器的设计却是一个模拟电路设计,因此需要用到D/A转换器。

根据正弦信号发生器的波形,得知该实验的输入为时间,而输出为振幅。如果将正弦波的振幅放在存储单元为64的ROM中,根据ROM的功能得知,ROM中的数据与地址是一一对应关系,因此设计由时间和振幅的对应关系转换为时间和地址的对应关系。据此,要得到正弦信号,需要设计一个6位二进制计数器。下图为总体设计框图:

图1 正弦信号发生器总体设计框图

图1 正弦信号发生器总体设计框图

在许多实用情况下,必须使用宏功能模块才能使用一些Altera特定器件的硬件功能,例如各类片上存储器、DSP模块等等。这些可以以图形或硬件描述语言模块形式方便调用的宏功能块,使得基于EDA技术的电子设计的效率和可靠性有了很大的提高。

LPM是参数可设置模块库(Library of Parameterized Modules)的英语缩写。根据实际电路的设计需要,选择LPM库中的适当模块,并为其设定适当的参数,就能满足自己的设计需要,从而在自己的项目中十分方便的调用优秀的电子工程技术人员的硬件设计成果。

LPM功能模块内容丰富,每一模块的功能、参数含义、使用方法、硬件描述语言模块参数设置及调用方法都可以在QuartusⅡ中的help中查阅到,方法是选择helpàMegafunction/LPM命令。

定制LPM_ROM模块流程:

1、定制初始化数据文件,建立.mif格式文件

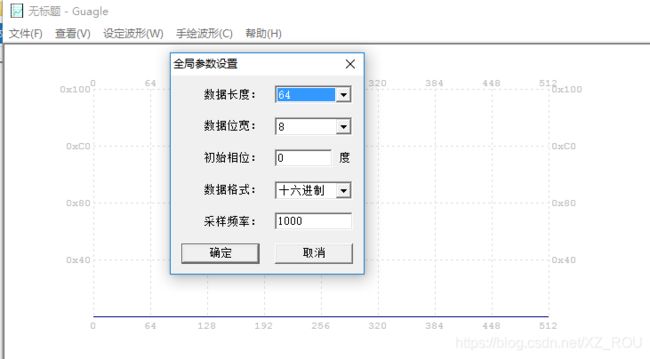

(1)打开Mif任意波编辑器Mif_Maker2010【软件已上传资源库】,选择“设定波形”-“全局参数”,修改数据长度为64,数据宽度为8,如图1所示。

设定数据长度、位宽及数据格式

设定数据长度、位宽及数据格式

(2)选择“设定波形”-“正弦波”,如图2所示。

设定波形

设定波形

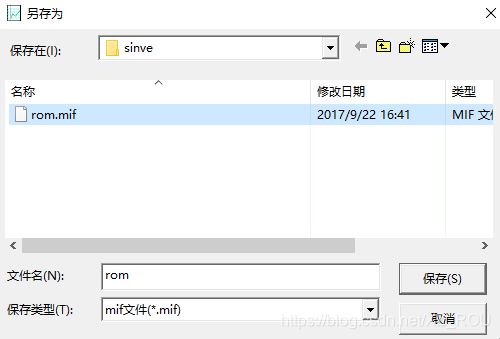

(3)在文件中选择保存,保存在D:/myfile/sinve文件夹【建议保存在即将使用的工程文件目录下】,注意sinve是工作库目录,如图3所示。

保存定制的rom.mif文件

保存定制的rom.mif文件

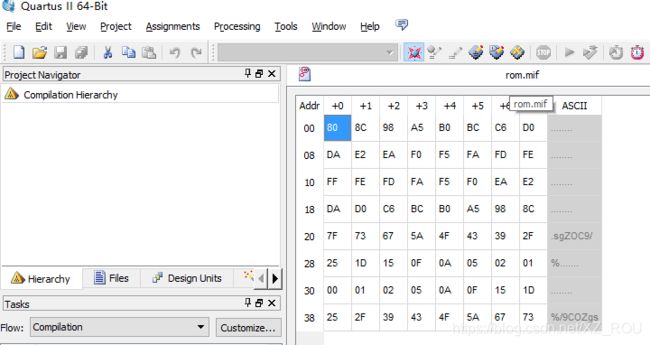

(4)在QuartusII软件中打开rom.mif文件,如图4所示。

在QuartusII中打开rom.mif文件

在QuartusII中打开rom.mif文件

2、定制LPM_ROM元件

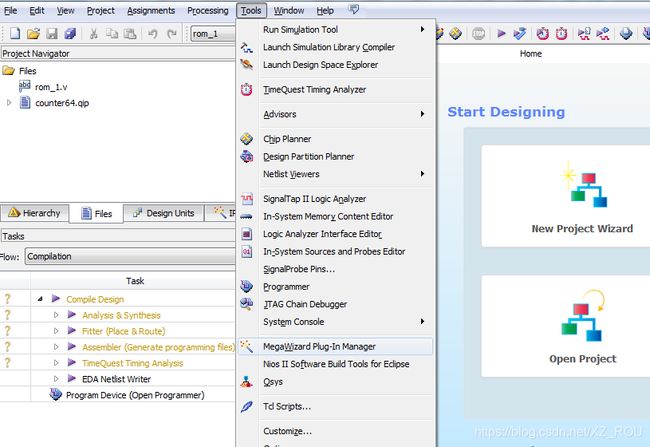

(1)打开Tools菜单,选择“MegaWizard Plug-In Manager”,如下图5所示。

找到MegaWizard Plug-In Manager菜单

找到MegaWizard Plug-In Manager菜单

(2)点击打开MegaWizard Plug-In Manager初始对话框,选择创建新的宏功能模块,如图6所示。

MegaWizard Plug-In Manager初始对话框

MegaWizard Plug-In Manager初始对话框

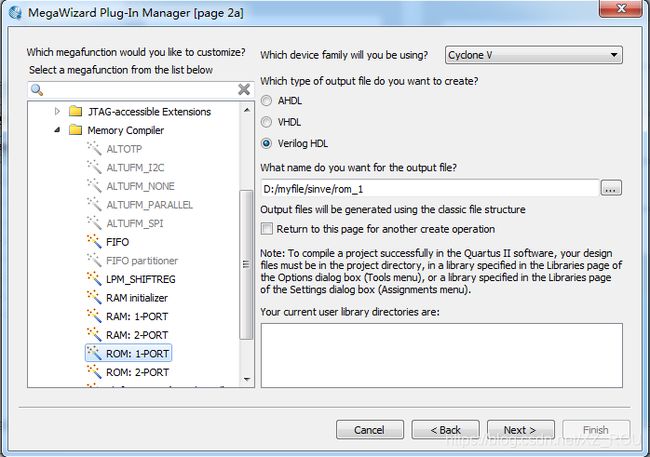

(3)点击“Next”,选择选择宏功能块(ROM:1-PORT)、使用器件(ACEX1K)、输出文件信息(文件类型:VerilogHDL;文件地址:D:\\myfile\sinve\;文件名称:rom_1),如图7所示。

选择宏功能块、使用器件、输出文件信息

选择宏功能块、使用器件、输出文件信息

(4)点击“Next”,选择ROM模块存储数据位数和地址线宽(即存储容量),如图8所示。

选择ROM模块数据线和地址线宽

选择ROM模块数据线和地址线宽

(5)点击“Next”,选择地址锁存信号inclock,如图9所示。

选择地址锁存信号inclock

选择地址锁存信号inclock

(6)点击“Next”,导入定制的.mif文件,【最重要的一步】

导入定制的.mif文件

导入定制的.mif文件

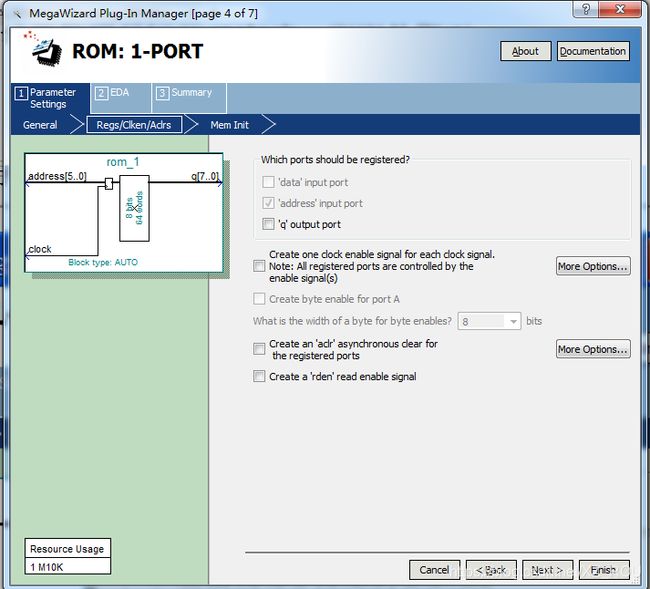

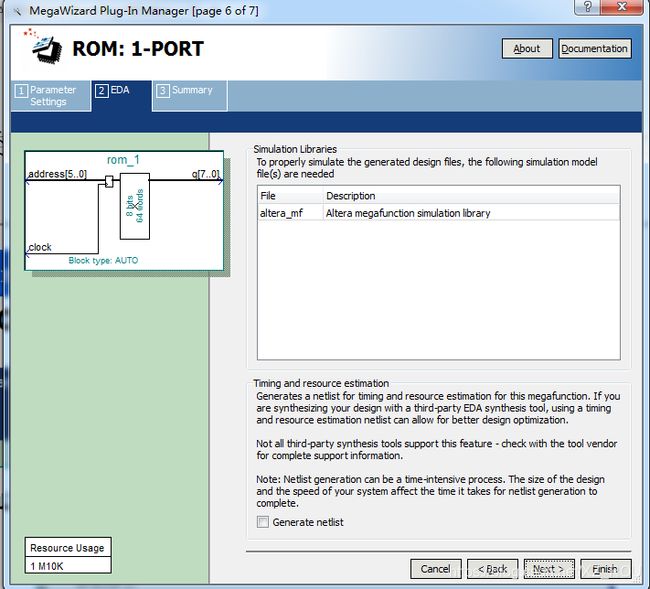

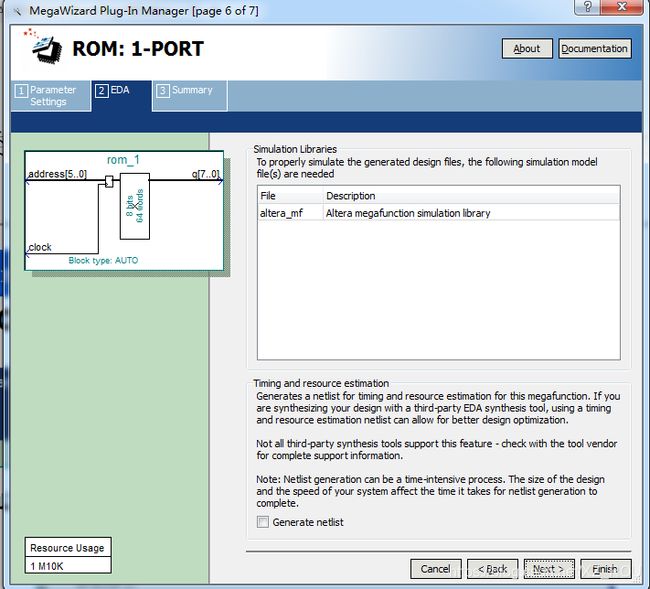

(7)默认仿真库,如图11所示,不做任何选择。

默认仿真库

默认仿真库

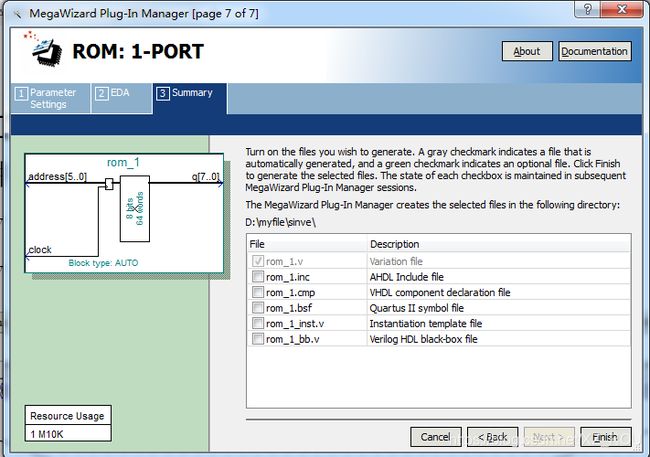

(8)选择产生文件类型,默认产生rom_1.v,可以自由选择让系统产生更多的文件。【建议把后三个方框都勾上】

选择产生文件类型

选择产生文件类型

3、对生成的文件建工程,编译、仿真,生成rom_1元件。

(1)首先在文件夹D:\\myfile\sinve\中找到生成的文件rom_1.v;

(2)将rom_1.v设为当前工程,并对其编译;

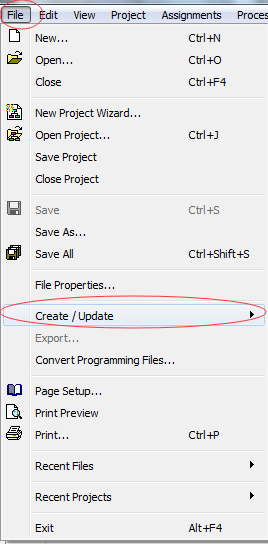

(3)点选File-Create/Update-Create Symbol Files for Current File,生成rom_1元件,如图13所示。

生成rom_1元件

生成rom_1元件

(4)点选File-New-BlcokDiagram/Schematic File,在新出现的界面,左键双击,出现如下图界面,双击rom_1,界面就会出现rom_1元件。

找到 rom_1元件

找到 rom_1元件

选学一:仿真ROM元件

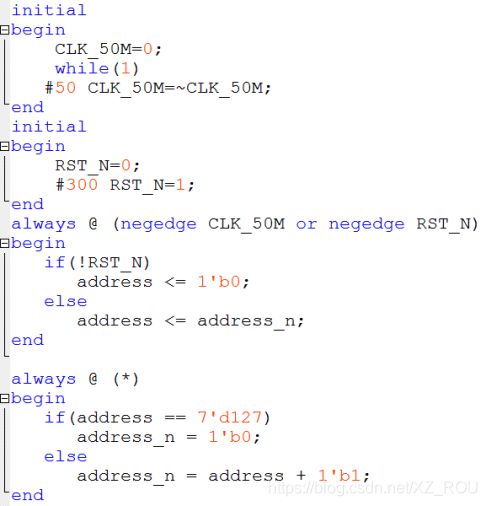

(1)重新建立一个工程,其文件源代码如下图所示:

(2)对该工程编译,产生其仿真的test bench模板,产生方法为点选Processing-Start-Start Test Bench Template Write,如下图15所示。

产生仿真的test bench模板

产生仿真的test bench模板

(3)打开sinve-simulation-modelsim文件夹,找到Verilog_Ip_ROM.vt文件,打开,如图16所示。

找到Verilog_Ip_ROM.vt文件

找到Verilog_Ip_ROM.vt文件

(4)修改test bench的初始化内容,如下所示。

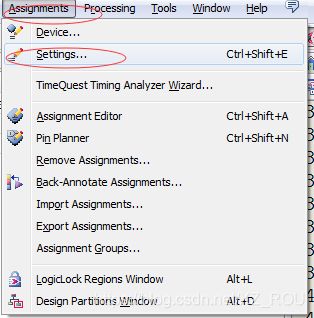

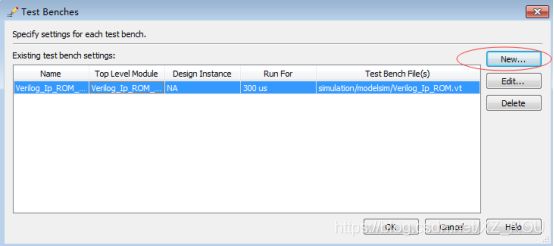

(5)设置test bench,点选Assignments-Settings-Simulation,如图17所示选择,其中test bench name就是Verilog_Ip_ROM.vt文件的模块名。

设置test bench

设置test bench

(6)点选Tools-Run Simulation Tool-RTL Simulation,如下图所示,用Modelsim仿真。

选择仿真工具

选择仿真工具

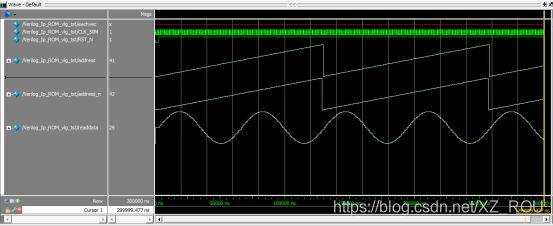

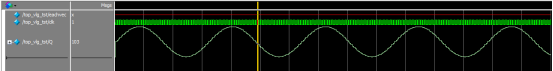

(7)仿真结果如图19所示,注意右键点选信号,选择显示方式为

modelsim仿真结果

modelsim仿真结果

根据上面讲述的定制LPM_ROM模块流程,完成以下实验任务。

实验任务一

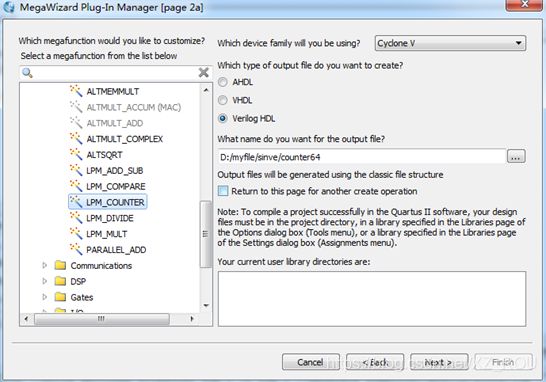

根据上述QuartusⅡ宏功能模块的使用方法,在“Arithmetic”中选择“LPM-COUNTER”设计6位计数器,对生成的counter1.v文件建工程、编译、仿真,并生成counter64元件。

注意:计数器宏功能块的选择:

选择计数器宏功能块

选择计数器宏功能块

实验任务二

完成正弦信号发生器的完整设计,并给出其时序波形及其分析。

正弦信号发生器的完整设计

正弦信号发生器的完整设计

选学二:顶层设计的仿真

第一种方法(使用SignalTap II Logic Analyzer)

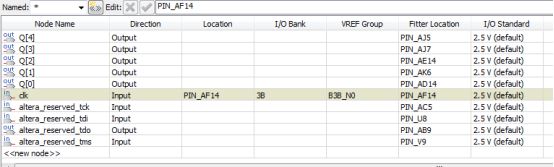

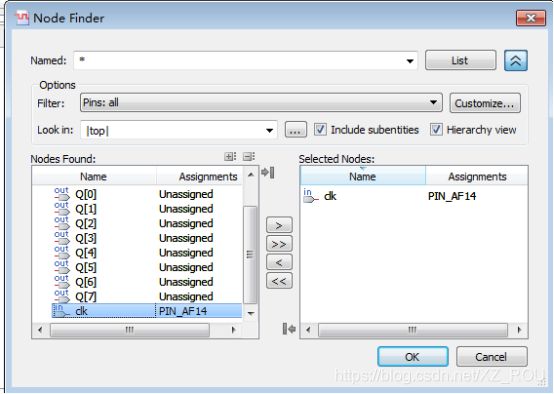

(1)将clk的引脚锁在系统时钟上,时钟引脚要去看友晶的用户手册,这里直接给出,是AF14。然后全程编译。

时钟的引脚锁定

时钟的引脚锁定

(2)点选File-New-signalTap II Logic Analyzer File,如图23所示。

选择signalTap II Logic Analyzer File

选择signalTap II Logic Analyzer File

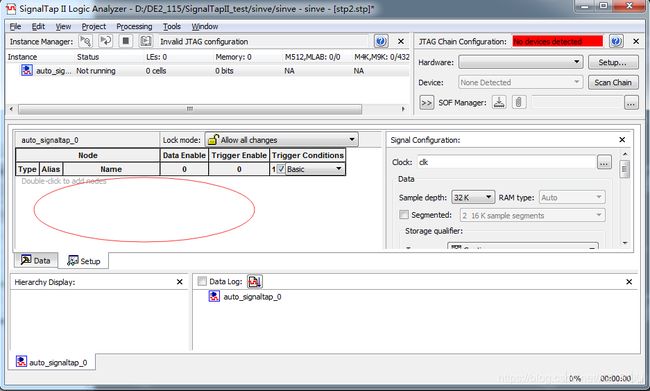

(3)在弹出的界面选择setup,添加采样时钟clock,如下图24所示。

添加采样时钟

添加采样时钟

(4)在如图所示地方双击添加输出信号q[7:0]。

添加其他信号

添加其他信号

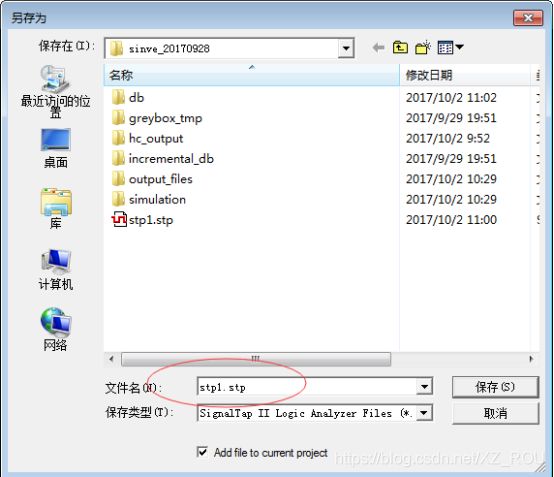

(5)选择File-Save As,输入此SignalTap II文件名为stp1.stp(默认文件名和后缀),单击“保存”按钮后,将会出现一个提示:“Do you want to enable SignalTap II...”,应该单击“是”按钮,表示同意再次编译时将此SignalTap II文件与工程捆绑在一起综合/适配,以便一同被下载进FPGA芯片中去完成实时测试任务。

保存为.stp的文件

保存为.stp的文件

(6)点选Processing-Start Compilation命令,启动全程编译。

(7)重新打开,点选Tools-SignalTap II Logic Analyzer,如图27所示。

打开signalTap II Logic Analyzer

打开signalTap II Logic Analyzer

(8)单击右侧的Setup按钮,确定编程器模式,如USB-Blaster。然后单击下方的Device表框边的Scan Chain按钮,对开发板进行扫描。如果在板上出现FPGA的型号名,表示系统JTAG通信情况正常,可以进行下载。按"..."按钮,选择SOF文件,再单击左侧的下载标号,观察左下角的下载信息。

下载设定

下载设定

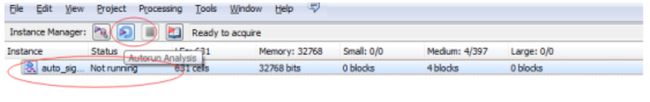

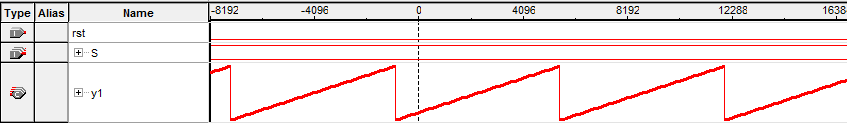

(9)启动SignalTap II进行采样与分析,单击Instance名auto_sin,再单击Processing菜单的Autorun Analysis按钮,启动SignalTap II连续采样。采样波形如下图所示。

启动SignalTap II进行采样与分析

启动SignalTap II进行采样与分析

第二种方法:(用Modelsim仿真)

流程同rom_1仿真,不同点列写如下:

(1)将顶层的.bdf文件转成.V的文件,方法如下图30所示,点选File-Create/Update-Create HDL Design File from Current File。

顶层的.bdf文件转成.V的文件

顶层的.bdf文件转成.V的文件

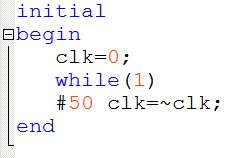

(2)生成test bench 模板后,修改test bench的初始内容如下代码所示。

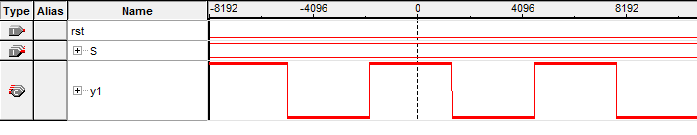

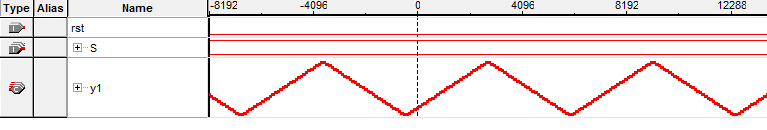

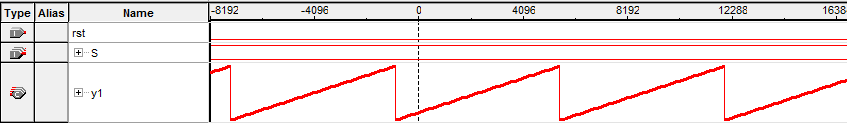

(3)顶层设计的modelsim仿真波形如图31所示。

顶层设计的modelsim仿真波形

顶层设计的modelsim仿真波形

实验任务三

硬件验证设计正弦信号发生器的功能。

1 该实验电路模式可以任选

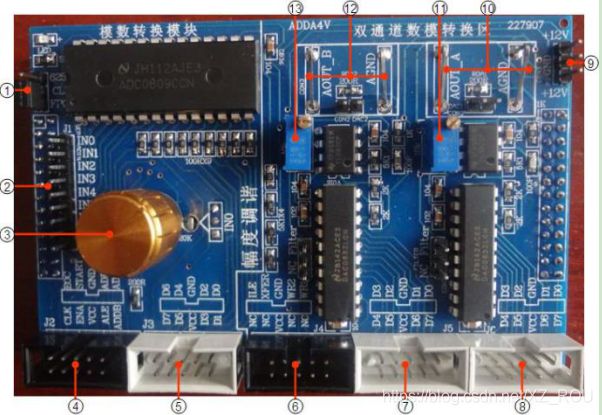

2 该实验需要使用DAC0832扩展模块,如图32所示。需注意:该扩展模块如果插在主系统上使用,要选择主系统的带+-12V的的插座,比如我们实验箱的实验模块3。

双通道DAC和ADC标准模块

双通道DAC和ADC标准模块

其中:标注“6“是DA0832的控制端,用户可根据0832的使用手册进行控制。标注”7”是0832的B通道的数据输入端。标注“8“是0832的A通道的数据输入端。标注“10、12“分别是A/B通道的输出接示波器端口。标注“11、13“是调节A/B通道的幅度的点位器。另外0832左边上是分别有个跳线帽,是滤波选择,如跳下是无滤波,跳上是有滤波。

3 DAC0832的8位数据口D[7..0]可以和FPGA的80芯端口的任意8个扩展口相连,比如和DB15~DB10及DBT1、DBT0相连;时钟信号接系统的clockB0。

作业1:

设计三角波、方波、锯齿波中的任何一种。

提示:修改ROM中存储的数据即可。

作业2:

设计信号发生器,该信号发生器能够产生三角波、方波、正弦波和锯齿波。

提示:使用多路选择器。

多路信号发生器不同输入时SignalTap 逻辑分析仪的波形

多路信号发生器不同输入时SignalTap 逻辑分析仪的波形

实验总结与分析