MBIST --- PATR2.Memorybist 测试流程

mem bist作为现在design设计中不可或缺的DFT设计内容,越发重要。本章节主要介绍mem bist的flow,如何在tessent中实现mbist以及tessent中的一些命令和mode。

overview

-

Contexts and Modes

整个实现过程在flow里里面按照system mode,可以分为三种:setup、analysis、insertion,按照context分类分为DFT和pattern

从DFT来看,在run dft过程中分为

setup:包括环境的setup和一些设定,为insert dft logic

analysis:进行design rule check,insert scan和test point并做对应的analysis

insertion:RTL or gate-level editing,也就是dft insertion

从Contexts角度来看:

setup:环境setup和一些设定,为gen pattern做准备

analysis:进行drc check并生成patterns

关于命令设置:SETUP> set_contest dft -rtl

1. Load design and specify requirements

1.1 Load design

Load design:

1) SETUP> read_verilog xxx.v

2) SETUP> read_verilog -f xxx.list

SETUP> set_current_design top.v

3) SETUP> set_design_source -format verilog -y -extensisons

SETUP> read_verilog top.v

Read library:

Use tessent library,mentor atpg library

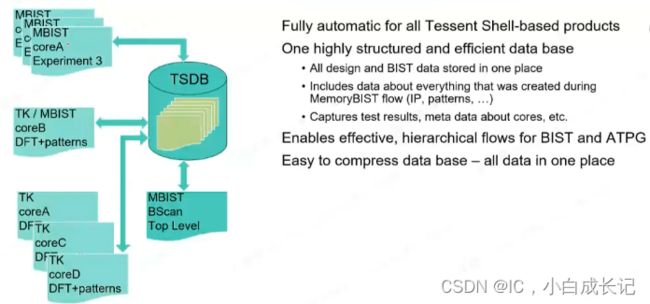

tessent membist models read in and processed as Tessent Core Descriptions(TCD),同时会存入到tsdb的database中

关于读library,如果之前没有读入过,直接read_cell_library读入即可,如果之前存入过tcd,可以直接

SETUP> set_design_sources -format tcd_memory

Elaborate design:

如果前面设置了set_current_design,会自动触发elab操作,如果前面只是读入了verilog,那么需要设置root design。所以set_current_design是在读完design和lib之后才设置的。

在elab过程中,可以允许有些design缺失,不过对于这些不包含mem或者或者与mem有关elements的module需要设置add_black_box

Optional Data:

一个controller(TMB)只能包含一个power domain中的mem,而一个power domain中的不同mem可以连接在不同的controller

use upf信息对controller进行声明,通过read_upf xxx.upf读入相应的upf

如果mem已经摆好了floor plan,可以通过读入def的方式对controller进行声明。通过read_def xxx.def方式读入。

Report command:

report_design_sources 可以把design和读入的library信息报告出来

report_memory_instances可以把相应的mem的信息报告出来

同样支持tcl base脚本

SETUP> join [lsort [get_name_list [get_mem_inst]]] \n

1.2 specify requirements

Design Level

声明design所在的level,不同level的design需要进行不同的设置

*Chip: 声明为top层,表明所有的ports都需要有pad buffer,需要一个TAP controller,BISR controller也会需要,如果pad需要做boundary scan测试,也需要插入相应逻辑。

*Sub_sys: 可能不需要做TAP和BISR controller,只需要把相关的小的逻辑做进去,做综合和timing就可以了。

Memory BIST Options

set_dft_specification_requirement -memory_test on|off

在上述命令设置之后,还会有 -mem_bist on|off -mem_bisr_chain on|off -mem_bisr_controller on | off 的设置按照design需求进行设置。

Memory Instance Options

set_memory_instance_options [***]

通过对check过drc的mem进行相关的properity设定,并create dft specification

add inputs constraints

对于一些特殊的primary inputs,比如和scan 相关的scan信号,需要设置为固定值

add_input_constraints scan_en -C0

add_input_constraints scan_mode -C0

add_input_constraints pll_bypass -C0

set_attribute_value

比如定义一些top上的信号,如下所示在TOP定义TAP

set_attribute_value tck_p -name function -value tck

set_attribute_value tdi_p -name function -value tdi

set clock

tessent工具会从mem的ck pin对clock进行trace,trace到clock source处。必须用add_clock对clock进行define

SETUP> add_clock CLK -period 10ns -label RAM_CLK_100M

同样也可以对clock进行分频倍频的定义

SETUP> add_clock CLK_DIV -label RAM_CLK_mul_500M -reference PLL/OUT -freq_multiplier 5

DRCs

当上面的所有的constrants都设置完成,通过check_design_rules进行check。如果DRCs没有error,则sys mode会设置到analysis mode,否则回停在setup mode。

如果有DRCs问题,可以通过analyze_drc_violation方式进行debug

至此,关于Load design and specify requirements的内容介绍完毕。

2. Create and Process DFT Specification

这一步通过第一步的design和constraint,会create出来dft specification。然后有针对性的进行修改。然后会生成相应的bist电路和ijtag电路

2.1 Create DFTspecification

通过design level,specification requirements,mem_instance_options, defaultspecification, design等等会产生一个dft specification。可以通过report_config_data方式对打印出来的文本或者display_specification方式利用gui界面对现存的dft specification进行review。更加详细内容后面章节介绍。

2.2 Process DFT specification

process_dft_spec 用来把前面的dft specification用起来,进行rtl的bist 逻辑的生成和插入

-no_insertion: 只generate出来bist rtl逻辑,而不插入到rtl中。

tessent工具对于process的内容会默认存储在./tsdb_outdir中,所有修改的design都会存入相应的目录。

IJTAG ICL和PDL文件也会相应存储。如下图所示,tsdb_outdir目录基本存储了我们dft相关的所有内容。

3. Extract ICL

上面内容插入的bist logic本身是用IEEE标准engining进行的插如,ICL这一步把相关的内容抽取出来,作为备份。ICL :instrument connectivity language。通过process_dft_spec这一步骤,把ICL抽取出来。

ICL描述测试模块/hardware的 ports和基本的组成。extract_icl会验证ICL module的连接性并生成相应design level的ICL文件

要保证ICL抽取过程中pass,否则会影响test patterns的generation.当ICL pass之后,当前design的ICL的描述文件产生,用来gen patterns,如果有错可以通过DFTvisualizer进行ICL extraction errors的debug。

一般出错的情况可能是针对一些IP,用的是自己写的dft specification,而不是工具自动生成的dft specification。

4. Patterns Specification

工具生成test patterns给到bist signoff仿真(仿真的testbench),以后后续芯片回片的ATE测试。(仿真testbench和机台使用文件)

create_patterns_specification signoff | manufacturing -replace 生成相应的pattern的预览文件,并未真正生成出来,类似于create dft specification

process_patterns_specification 吃入pattern预览文件,进行真正的pattern产生,类似于process dft specificaition

5. Simulation Validation

这是design flow中的 最后一步骤,对testbench进行仿真测测试。

run_testbench_simulations,基于test case,对生成的pattern进行仿真

check_testbench_simulations 简要总结。