【原创】The solutional manual of the Verilog HDL: A Guide to Digital Design and Synthesis (2nd)—ch07-I

Chapter 7. Behavioral Modeling

7.11 Exercises

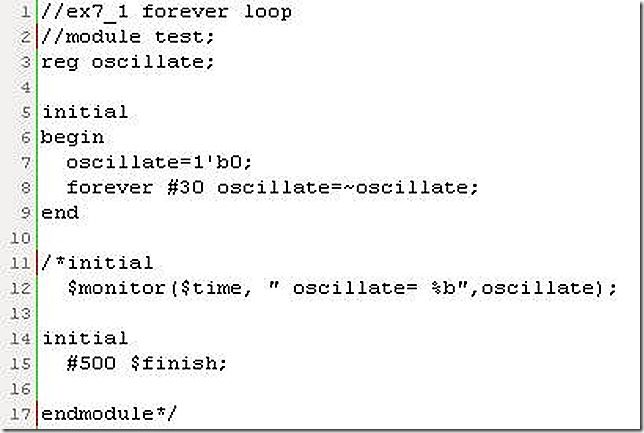

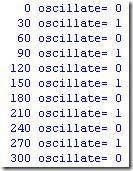

1. Declare a register called oscillate. Initialize it to 0 and make it toggle every 30 time units. Do not use always statement ( Hint: Use the forever loop).

my answer:

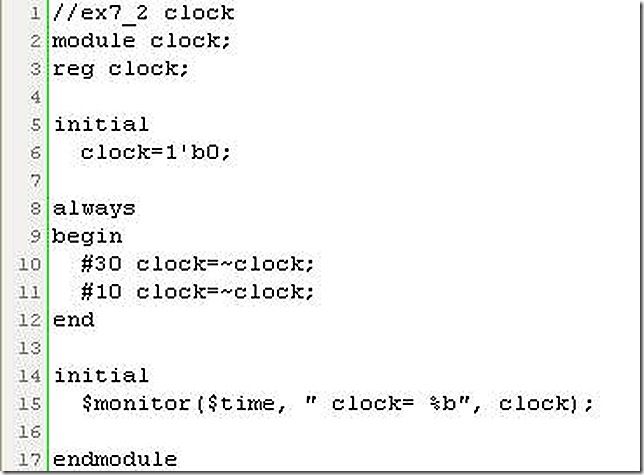

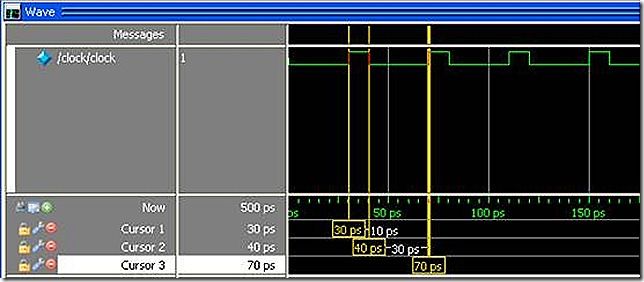

2. Design a clock with time period = 40 and a duty cycle of 25% by using the always and initial statements. The value of clock at time = 0 should be initialized to 0.

my answer:

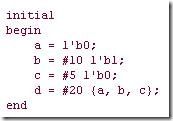

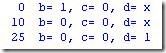

3. Given below is an initial block with blocking procedural assignments. At what simulation time is each statement executed? What are the intermediate and final values of a, b, c, d?

my answer:

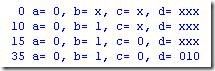

4. Repeat exercise 3 if nonblocking procedural assignments were used.

my answer:

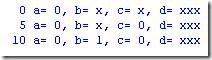

5. What is the order of execution of statements in the following Verilog code? Is there any ambiguity in the order of execution? What are the final values of a,b,c,d?

my answer:

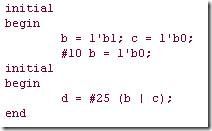

6. What is the final value of d in the following example? (Hint: See intra-assignment delays.)

my answer: