POE受电设备(PD)电路工作原理

硬件设计:POE--POE受电设备(PD)电路工作原理

参考资料:解决POE PD设计挑战的有效的解决方案

POE电源模块的介绍特性和芯片的详细资料概述

如何应对PoE受电设备设计挑战

以太网供电中受电设备的芯片设计与研究

以太网供电检测和分级接口电路设计

PD(Power Device,受电端设备)是POE系统中的客户端设备,如IP电话、网络安全摄像机、AP及掌上电脑等许多其他以太网设备。根据POE供电工作流程(参考:POE基础),PD端应该存在一个用于被检测的签名电路和PD功耗分类电路(可选),通过PSE供电设备的检测,得到稳定的48V供电电压,但是在一般电路中48V电压过高,需要一个电源转换器将48V电压转换至合适的电压;所以PD设备端的电路将由签名电路、功耗分级电路和电源转换电路组成。

一、签名检测电路

根据IEEE 802.3af标准要求,PD检测状态应该满足输入阻抗在23.75~26.25KΩ之间(一般取值24.9KΩ),输入电容在0.02~0.12uF之间,所以签名电路可设计如图1所示。

图1 PD签名电路

二、功耗分级电路

当进行功耗分级时,PSE会施加一个15.5~20.5V的探测电压(电流限制在100mA以下),PD设备通过从线路中吸收一个恒定的电流来向PSE表明自己所需的最大功率。

图2 PD分级接口电路

图2显示了两种分级接口电路;

图2(a)实现了一个0级PD;当PSE施加15.5~20.5V的探测电压后,稳压管VR1无法导通,所以PSE将检测到0mA的电流,即PD设备判定为0级;

图2(b)则实现了一个完整的分级电路,通过更改电阻R16的阻值,可以将PD分级;其中R14、Q12、Q13、R15构成一个350µA的偏置电流源,R14、Q12、R15是一个普通的三极管放大电路,而Q13构成一个负反馈电路,保证了流过R15的电流恒定,即形成一个简易电流源;同样,Q14、U11、R16和电流源又构成一个偏置电流源,U11是一个低电压可调节精密并联稳压器,可以保证R16两端电压稳定在1.24V,即保证了集电极电流的恒定,例如:R16=69.8Ω,则集电极电流I=17.77mA,则PD设备将被判定为等级2;而VR11保证了在PSE签名检测阶段,分级电路不工作;R12、VR12、R13、VR13、Q1构成欠压锁定(UVLO)电路,只要当输入电压达到42V以上时,MOS管Q1才导通,此时通过R17和Q15的控制,分级电路将失效;

三、电源转换器

电源转换器有两种选择,一种是DC/DC,另一种是LDO,考虑功耗损耗问题,一般采用DC/DC;另外产品的工作电压一般低于48V,所以选择降压型电路,所以PD设备中常见的电源转换器主要是BUCK型和FlyBack型,采用FlyBack电源转换器的整体电路设计如图3所示。

扩展资料:PD集成芯片设计方案

PD集成芯片设计方案一般采用下列两种方法:

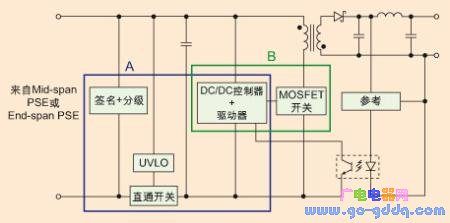

A、将前端接口电路和一个用于DC/DC转换器(驱动一个分立功率MOSFET)的PWM控制器集成在一片IC上,如图4中的A部分;

B、将一个功率MOSFET、PWM控制器和用于DC/DC转换器的所有支持电路集成在一片IC上,如图4中的B部分;

图4 PD电路框图

第一种方法貌似要将大部分电路集成到芯片中,然而,它并不是理想的最佳解决方案。因为接口电路仅仅具有一种可变功能:识别PD的级别;在IC内集成如此简单的电路并未实现最有成本效益地利用晶圆面积,特别是仅使用几个标准的独立元件就能以低廉的成本实现的电路,这些独立元件还可能在另个电路设计中重复使用,而DC/DC转换器比接口电路要复杂得多。因此,第二种方法如果把支持DC/DC转换需要的所有功能(包括过热保护、启动、软启动、UVLO、过压关断、过流保护等)都集成在IC内部的话,可以极大地简化设计;这种方法的设计也就相当于一款DC/DC电源芯片的设计,可参考资料也相对较多。