CPU系统级验证——验证环境——OpenHW core-v验证环境及文件分析

本文记录的相关源工程和文件为:

core-v RISCV核功能验证工程:https://github.com/openhwgroup/core-v-verif

core-v 验证策略:https://core-v-docs-verif-strat.readthedocs.io/en/latest/#

core-v系列核cva6工程:https://github.com/openhwgroup/cva6

core-v系列核cv32e40p工程:https://github.com/openhwgroup/cv32e40p

LowRISCV Ibex核工程:https://github.com/lowRISC/ibex

core-v RISCV核相关说明文档:https://github.com/openhwgroup/core-v-docs

RISCV ISA指令流(instruction stream)生成器:https://github.com/openhwgroup/force-riscv

core-v系列指令流(instruction stream)生成器:https://github.com/openhwgroup/core-v-isg

sail语言介绍:https://www.cl.cam.ac.uk/~pes20/sail/

REMS的sail RISCV开源项目:https://github.com/rems-project/sail-riscv

openHW全称为open-source hardware,是一个支持开源软件和硬件的非盈利组织。该组织开源的内容包括开源CPU核、相关IP、工具和软件等。下文中部分图片取自OPENHW。

1. cv32e40p

CV32E40P(原先PULP开发的RI5CY)是一个32bit的4级流水线核,支持整数运算指令、乘法除法指令、单浮点运算指令、压缩指令以及DSP扩展指令(包括硬件循环、SIMD扩展、位操作和增量指令)

该核的验证环境有两套,一套是原来基础上改进的的testbench;一套是UVM环境搭建的testbench,该环境下testcase的产生是可以基于UVM环境的(这种方式类似于Ibex核验证环境)。两套环境均由systemverilog编写。均包含了指令集验证、中断验证、CSR寄存器验证、异常验证、debug验证等。

1 目录概况

cv32e40p的验证环境在cv32文件夹中,该文件夹下又分为bsp,env,regress,sim,tb,tests六个文件夹。

- bsp

板级支持包,包含crt,syscall等初始化文件、链接脚本、一些简单的定向test

- env

包含uvm验证环境所需的一些环境文件,比如定义了一些类的文件,包含了一些宏的文件,以及一些参数的定义

- regress

包含了用yaml编写的配置文件,包含了工程makefile中用到的命令,以及每个testcase的配置信息

- sim

包含了两个验证环境的makefile脚本文件,分别为core文件夹和uvmt_cv32文件夹,同时还包含tools(仿真工具文件夹)、mcy和common.mk文件

- common.mk

该文件包含了两个验证环境的通用变量,通用操作(比如git clone、riscv-toolchain对执行对象的编译和反汇编等) - uvmt_cv32/Makefile

该文件是所有makefile的根文件,一切命令都需要在该文件的绝对下执行 - uvmt_cv32/xrun.mk

C家的xcelium运行脚本文件

- tb

包含了两个验证环境的testbench文件

- tests

包含了testcase源文件

- 自定义的测试程序

命令:make test TEST=... - corev-dv指令压力测试

类似于google的riscv-dv

命令:make corev-dv

make gen_corev-dv test TEST=... - 指令兼容性测试

包括riscv-tests、riscv-compilance和cv32扩展指令的定向测试文件

make compliance RISCV_ISA=COMPLIANCE_PROG=...

2 验证环境

(一) core testbench

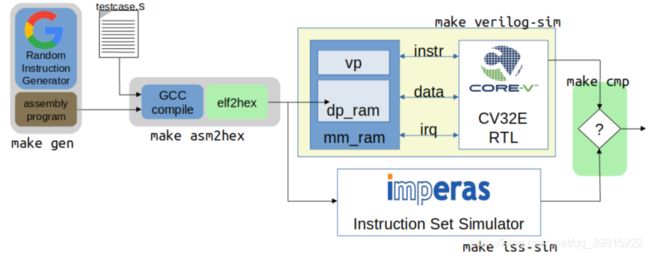

该工程是PULP遗留下的产物,OpenHW做了一定修改并持续维护。验证环境中已集成了指令集模拟器。

该工程的测试集激励包含指令兼容性测试(偏定向测试,如riscv-tests和riscv-compilance-tests)和随机约束(google riscv-dv),和其他的一些fireware测试用例。

测试环境结构如下:

该testbench简单,运行较快,通过verilator运行,但是有额外的开销且不能获取覆盖率。

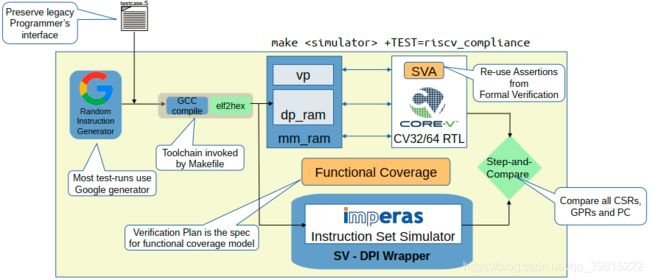

(二) UVM 验证环境(uvmt_cv32)

cv32核的UVM验证环境已搭建完成,在DSIM(Metrics)运行也很稳定。验证环境中可以集成了指令集模拟器参考模型,整个环境功能齐全且可复用性较高,可以经过简单修改应用到其他CPU上

uvm验证环境的testcase均是由uvm相关类生成,同时该环境还集成了riscv-dv,但具体的激励生成还需要再分析。

- 脚本中相关变量

(1)进行仿真命令的变量

即 make test 等

-

GUI

GUI=1允许打开图形界面进行调试 -

ADV_DEBUG

ADV_DEBUG=YES允许EDA公司先进的调试工具运行,例如cadence,即运行indago而非simvision -

USER_RUN_FLAGS

与UVM_MAX_QUIT_COUNT搭配,表示中止test允许的error数量 -

WAVES

WAVES=YES即sim的同时就产生波形 -

COV

COV=1,即进行覆盖率分析

(2)仿真后的命令

- make cov TEST=...

进行某项测试的覆盖率分析并打印报告。 - 变量MERGE

将所有测试的覆盖率分析融合到一个report中

- 验证环境架构

(1)验证环境概况

该testbench有两种工作模式,一种是只有DUT的情况,测试激励为自检测测试,测试是否成功会设置一个寄存器中的某位,testbench会在测试结束后读取该位的值,从而确定测试是或否成功;第二种是step compare,比较DUT和ISS的输出trace。

对于第二种工作模式,ISS是可以通过设置脚本命令变量(ISS)选择是否参与仿真。如果命令中设置了ISS=1,则会通过uvmt_cv32_step_compare模块进行trace的比较

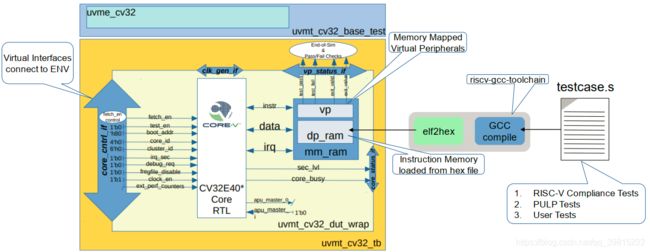

验证环境的顶层文件是uvmt_cv32_tb.sv,DUT的顶层文件是uvmt_cv32_dut_wrap.sv,参考模型的顶层文件是uvmt_cv32_iss_wrap.sv。

- DUT

DUT的顶层文件中又包含cv32e40p_wrapper和指令/数据存储器,其中cv32e40p_wrapper包含core的顶层文件和其他一些可选APU、exception的tracer模块。

tracer模块保存已执行指令的CPU的寄存器值,保存对应状态位,同时该模块会提供pc值和GPR值给step_compare模块

- reference module

参考模型也是有systemverilog编写,而不是现成的可执行文件。其顶层文件中包含core的参考模型CPU.sv、RAM(模拟指令/数据存储器)和自定义的总线BUS。

- step_compare

单步比较模块存在的前提是参考模型加入(即ISS=1),用于验证DUT和参考模型的运行结果

当指令执行完成会和DUT和参考模型的Tracer模块进行握手 - assertion

TB中的assertion包括interrupt相关、debug相关、指令数据OBI接口相关 - coverage组件

包括core、interrupt、debug等的coverage module和covergroup。coverage module在对应agent种,covergroup在env中

uvme_rv32isa_covg模块用于统计ISA的功能覆盖率,从而确保每条指令运行都能覆盖到所有的源寄存器和目的寄存器,计算指令的混合度

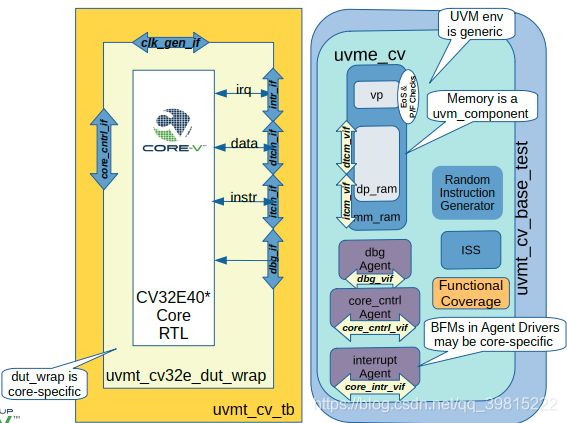

(2)UVM内部组件关系

上图为UVM testbench中的DUT部分,即uvmt_cv32_dut_wrap模块,DUT有包含CV32的RTL代码和mm_ram。

mm_ram包含了virtual peripheral(VP)和双端口的RAM(dp_ram,包含指令/数据存储器)。dp_ram模型有两个OBI接口,不同功能的虚拟外设用做CPU的定向测试的外设,包括中断产生,随机数,定时器等

debug、interrupt、OBI、时钟/reset均通过UVM_agent组件产生,且通过uvm_sequence组件输入激励。

同时每种agent都包含对应的functional coverage module组件,方便了收集覆盖率

下图为UVM验证环境运行的流程

(3)uvmt_cv32中的测试激励

该环境包含自定义测试激励和随机测试激励。

自定义测试激励一般为定向测试的C代码和汇编代码。C代码可以通过man函数返回值确定该case的pass/fail

随机测试激励通过corev-dv自动生成汇编代码。

2. CVA6

CVA6(ariane)是一个6级流水线、单发射、顺序执行的RV32GC或RV64GC核,支持M/U/S三种模式,支持linux操作系统。

该核现存的验证环境尚未成熟,但同样可以构建UVM的验证环境。

该工程的指令集测试激励包括riscv官方测试套件(即riscv-tests)。