Ultrascale/Ultrascale+ FPGA GTH IP及结构详解(二)

目录

一、Physical Resource界面对应GTH结构说明

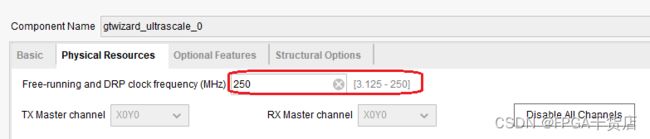

1.free-running and DRP时钟频率

1.1DRP接口

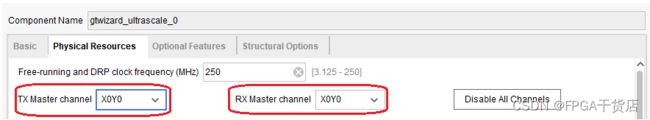

2.TX/RX Master CHannel

3.Channel table

3.1参考时钟的选择和分布

二、Optional Features界面

2.1Receiver comma detection and alignment

1.Valid comma values for 8B/10B encoding

2.comma detection

3.comma alignment

一、Physical Resource界面对应GTH结构说明

1.free-running and DRP时钟频率

该IP选项是设置用于提供GTH Transceiver core和example中给helper block模块使用 时钟,同时用于提供给DRP接口的时钟,在gth ip的文档中对该时钟需设置的频率给出了说明:

1)当RXUSRCLK2频率小于等于TXUSRCLK2,则选择Fupper最小频率或是RXUSRCLK2频率;

2)当RXUSRCLK2频率大于TXUSRCLK2,则选择Fupper最小频率或是TXUSRCLK2频率;

那么下面简单介绍DRP的接口描述及时序;

1.1DRP接口

动态重配置端口DRP允许动态改变GTHE3/4_CHANNEL和GTHE3/4_COMMON源语的参数。DRP接口是一个处理器友好的同步接口,具有地址总线(DRPADDR),读(DRPDO)和写(DRPDI)数据独立分开;一个使能信号(DRPEN),读写控制信号(DRPWE),和一个ready/vaild(DRPRDY)作为控制信号来实现读写的操作、表明操作完成或是表明数据有效。

(1)DRP写接口时序: 当DRPRDY有效时,新的DRP操纵执行。

(2)DRP读接口时序: 当DRPRDY有效时,新的DRP操纵执行。

(3) 端口描述:

对于GTHE3/4_CHANNEL源语的DRP接口:

| 端口 |

方向 |

时钟域 |

描述 |

| DRPADDR[8:0] |

In |

DRPCLK |

只用于UltraScale FPGAs |

| DRPADDR[9:0] |

In |

DRPCLK |

只用于UltraScale+ FPGAs |

| DRPCLK |

In |

N/A |

DRP接口时钟 |

| DRPEN |

In |

DRPCLK |

DRP使能信号 1:读写使能操作 对于写操作,DRPEN和DRPWE同时在一个DRPCLK时钟周期拉高有效 |

| DRPDI[15:0] |

In |

DRPCLK |

写配置数据总线 |

| DRPRDY |

Out |

DRPCLK |

表明写操作完成标志和读操作数据有效;

|

| DRPDO[15:0] |

Out |

DRPCLK |

从配置端口中读取数据总线 |

| DRPWE |

In |

DRPCLK |

DRP写使能 0:当DRPEN为1时读操作; 1:当DRPEN为0时写操作; |

| PCSRSVDIN[2] |

In |

Aysnc |

只用于UltraScale FPGAs复位 |

| DRPRST |

In |

DRPCLK |

只用于UltraScale+ FPGAs复位 |

对于GTHE3/4_COMMON源语的DRP接口:

| 端口 |

方向 |

时钟域 |

描述 |

| DRPADDR[8:0] |

In |

DRPCLK |

只用于UltraScale FPGAs |

| DRPADDR[15:0] |

In |

DRPCLK |

只用于UltraScale+ FPGAs |

| DRPCLK |

In |

N/A |

DRP接口时钟 |

| DRPEN |

In |

DRPCLK |

DRP使能信号 1:读写使能操作 对于写操作,DRPEN和DRPWE同时在一个DRPCLK时钟周期拉高有效 |

| DRPDI[15:0] |

In |

DRPCLK |

写配置数据总线 |

| DRPRDY |

Out |

DRPCLK |

表明写操作完成标志和读操作数据有效;

|

| DRPDO[15:0] |

Out |

DRPCLK |

从配置端口中读取数据总线 |

| DRPWE |

In |

DRPCLK |

DRP写使能 0:当DRPEN为1时读操作; 1:当DRPEN为0时写操作; |

可以通过IP界限将需要的信号勾选,如下图所示:

2.TX/RX Master CHannel

当有多个Channel通道使能时,需要选择TX和RX的主通道,主要是为了驱动example中的user clocking network helper block的时钟源;

当下面的channel只选择一个时,该IP选项会变成灰色不用选择;

3.Channel table

该选项用于选择使用channel的位置、外部参考时钟;该表格中的channel数量及位置与FPGA device的型号有关。

当选择完成后,左边会将选择的结果显示出来;

(1)选择参考时钟源;

(2)选择GHT channel;

3.1参考时钟的选择和分布

在架构上一个Quad(或Q)的概念是包含:

- 一组4个GTHE3/4_CHANNEL源语(也就是4个GTH transceivers);

- 一个GTHE3/4_COMMON源语;

- 两个专用的外部参考时钟对;

- 专用南北参考时钟布线;

对于一个Quad的参考时钟可以来自它下边的两个Quad (Q(n–1) 或 Q(n-2))的GTNORTHREFCLK,也可以来自它上边的两个Quad (Q(n+1) or Q(n+2))的GTSOUTHREFCLK;也就是说每个GTH transceivers通道有6个参考时钟可以使用。

- QPLL和CPLL多个参考时钟选择

当有多个参考时钟输入时,QPLL会通过端口QPLL0/1REFCLKSEL,CPLL通过端口CPLLREFCLKSEL选择所需要的时钟,如下图所示;例如,当输入的参考时钟是GTREFCLK00/01时,QPLL0/1REFCLKSEL则为3’b001,这个连接是由Xlinx工具完成的,但是也是通过界面去设置

- 单参考时钟用户使用

每个Quad都有两对差分参考时钟,无论使用其中一个时,都需要例化IBUFDS_GTE3/4源语,输出的O给GTHE3/4_COMMON和GTHE3/4_CHANNEL源语的GTREFCLK0端口,如下图所示;

同时,上一小节也讲到Quad的时钟你可以给它上下两个的Quad使用,如下图所示;

2.多个参考时钟用户使用

当一个Quad使用多个参考时钟时,每个输入的参考时钟都必须例化自己的IBUDFS_GTE3源语使用,如下图所示;但QPLL或CPLL使用哪个参考时钟就需要用户自己去选择设置。在这种模式下,Xilinx工具不会主动给完成,而是由用户去完成;

同时,上一小节也讲到Quad的时钟你可以给它上下两个的Quad使用,如下图所示;

注意:

- 外部多个参考时钟使用,他们都是要来自同一个晶振输出;

- 多速率的设计可能需要动态改变使用参考时钟源,当动态改变后需要复位CPLL或是QPLL的复位端口;

- 从Transceiver输出的TXOUTCLK和RXOUTCLK必须使用BUFG_GT buffer;

二、Optional Features界面

2.1Receiver comma detection and alignment

1.Valid comma values for 8B/10B encoding

该设置选项用于选择是所有的8B/10B comma作为comma字符,还是将IEEE Std 802.3指定的comma作为comma字符;

(1)8B/10B编码

8b10b编码一句话概括起来就是把8bit的数据变成10bit的数据,其中所有1或0的个数不会超过6个,并且连续的1或0的个数不会超过4个。这样原本1024的汉明空间编码后就大大减小了。其中有256个data码和12K码控制码。这样数据和控制码不会重合。

GTH transceiver建立8B/10B TX路径是为了编码TX data无需消耗device资源。dan使能8B/10B编码会增加TX的路径延时。![]()

其中K28.1,K28.5,K28.7可以作为分隔码,也叫comma码,用于接收端在串行的数据流中找到字节边界。常用的K28.5即0xBC。

(2)那什么是为comma码,K码?

在serdes上面的高速串行流在接收端需要重新串并转化成多字并行,怎么找到字的边界进行对齐呢? 这就需要一个特殊的序列,这就是comma码。 传输过程中需要的一些控制,最好不要和数据冲突了,这就是K码。

在8B/10B的编码中可以看到特殊的码(K码),他主要用于控制功能。其中TXCTRL2端口被用于表示在TXDATA上的数据是否是K码或是常规数据。当TXCTRL2拉高后,8B/10B编码器会检查接收的TXDATA字节是否和任意K码匹配。

K28.5字符用于识别一帧数据的开始,数据发送时以字为单位传输,在接口处数据是32位,用于字节对齐与数据同步。检测到帧同步信号(K28.5)时,根据所处的位置将同步字符提取出来删掉,剩余部分为有效数据。

2.comma detection

该选项用于选择comma的类型(默认选择K28.5,代码发送及检测8'hBC),以及comma检测方式(单独选择plus或minus,还是两者组合);

3.comma alignment

该选项用于选择comma检测对齐是任意字节、双字节还是4字节的方式。