错题集:HDLBits Exams/m2014 q6c

摘要:这道题的独热码编码状态机,在仿真时,出现了让我疑惑的问题,在上一篇文章中,我发现两种写法(case语句/assign语句)都可以通过,但这道题,只有用assign语句以及选通状态某一位来编写状态逻辑式的写法可以通过。

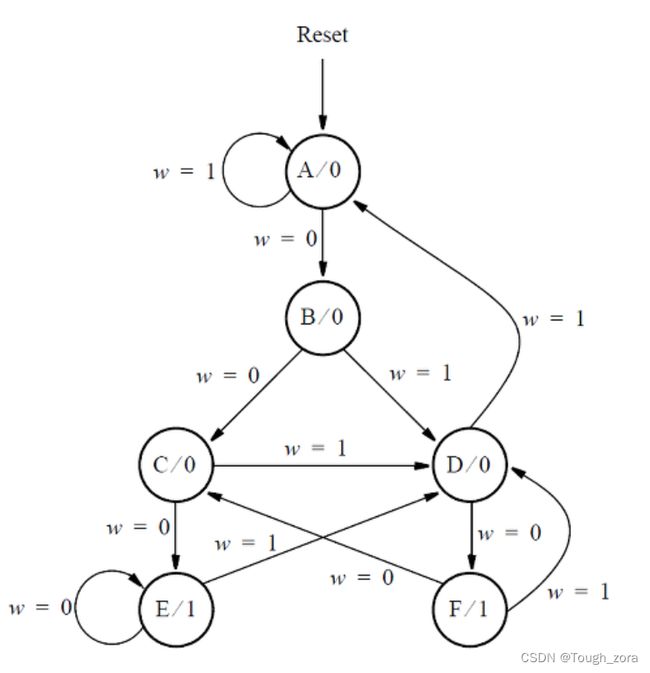

对于这部分,假设一个独热代码与状态赋值 'y[6:1]= 000001、000010、000100、001000、010000、100000、100000 分别用于状态 A、B,..., F。

为下一个状态信号 Y2 和 Y4 编写逻辑表达式。 (通过检查推导出逻辑方程,假设是独热编码。测试平台将使用非一个热输入进行测试,以确保您不会尝试做更复杂的事情)。

- 方法一:出错了,代码和仿真情况如下:

module top_module (

input [6:1] y,

input w,

output Y2,

output Y4);

parameter A=6'b000001,B=6'b000010,C=6'b000100,D=6'b001000,E=6'b010000,F=6'b100000;

reg [6:1] next_state;

always@(*)begin

case(y)

A:next_state = w?A:B;

B:next_state = w?D:C;

C:next_state = w?D:E;

D:next_state = w?A:F;

E:next_state = w?D:E;

F:next_state = w?D:C;

default:next_state = A;

endcase

end

assign Y2 = next_state[2];

assign Y4 = next_state[4];

endmodule 在网上看到别人的解题方法,也有一模一样的报错,也贴到下面:

module top_module (

input [6:1] y,

input w,

output Y2,

output Y4);

parameter A=6'b000001,B=6'b000010,C=6'b000100,

D=6'b001000,E=6'b010000,F=6'b100000;

assign Y2=(~w&y[6:1]==A);

assign Y4=(w&y[6:1]==B)|(w&y[6:1]==C)|(w&y[6:1]==E)|(w&y[6:1]==F);

endmodule

- 方法二:网上看到的方法,能解题,但不具有实际意义,参数设了也没用不上,和题目的要求关系不大。

module top_module (

input [6:1] y,

input w,

output Y2,

output Y4);

parameter A=6'b000001,B=6'b000010,C=6'b000100,

D=6'b001000,E=6'b010000,F=6'b100000;

assign Y2=~w&y[1];

assign Y4=w&(y[2]|y[3]|y[5]|y[6]);

endmodule

- 方法三:我认为的正确解题方法,用上了状态转换思路

/*正确的结题方法:独热码的转换和我想象的不一样,我还没有完全弄懂,

目前明确的就是,输入的肯定不止是A~F这几个状态,并且在非A~F状态也能正常输出*/

module top_module (

input [6:1] y,

input w,

output Y2,

output Y4);

reg [6:1] next_state;

assign next_state[1] = (y[1]|y[4])&w;

assign next_state[2] = (y[1]&~w);

assign next_state[3] = (y[2]|y[6])&~w;

assign next_state[4] = (y[2]|y[3]|y[5]|y[6])&w;

assign next_state[5] = (y[3]|y[5])&~w;

assign next_state[6] = (y[4]&~w);

assign Y2 = next_state[2];

assign Y4 = next_state[4];

endmodule经过整理分析和重新读题,我找到了这道题困扰我的原因:

其实第一种方法和第三种方法都应该是可以的,但是因为这道题的题目希望我用assign语句以及简单的逻辑表达式来产生下一个状态,而不是用case语句来产生,所以题目给的输入是非独热的,也就是除了A~F还给了其他状态。而这种tb的输入就只有方法三能顺利通过。

一开始我认为题目的输入有问题,因为以输入y=24,w=1为例,就相当于y[5]和y[4]同时选通,在w=1的情况下,下个状态既可能是A也可能是D,因为不同assign语句是并行的,所以就有可能出现竞争冒险,也会出现一会儿次态为A,一会儿次态为D的情况,所以我认为题目有问题,所以我又读了一遍题,终于明白了,题目所说的意思。

所以报错的原因其实就是因为,我是按照假设tb的输入只有A~F来写的,而实际上的tb输入不止这几个状态,并且在A~F以外的某些状态下,输出是不唯一确定的,有50%的随机性。