NXP(I.MX6uLL)DDR3实验(RAM)——DDR发展历史

目录

- 何为RAM 和ROM

- SRAM 简介

-

- ①、地址线

- ②、数据线

- ③、控制线

- SDRAM 简介

-

- ①、控制线(时钟、片选)

- ②、A10 地址线

- ③、地址线

- ④、BANK 选择线

- ⑤、BANK 区域

- ⑥、数据线

- ⑦、高低字节选择

- DDR 简介

-

- ①、控制线

- ②、地址线

- ③、BANK 选择线

- ④、BANK 区域

- ⑤、数据线

- ⑥、数据选通引脚

- ⑦、数据输入屏蔽引脚

- 内存,RAM(DDR),ROM(EEPROM、flash),存储卡(emmc,sd,tf)以及Cache的区别与联系

Linux是运行在内存RAM(DDR)里面的,前面裸机代码实现逻辑:I.MX6U内部bootroom读取SD卡程序的头文件将DDR初始化,然后将SD卡文件拷到DDR里面去运行。

I.MX6U-ALPHA 开发板上带有一个256MB/512MB 的DDR3 内存芯片,一般Cortex-A 芯片自带的RAM 很小,比如I.MX6U 只有128KB 的OCRAM。如果要运行Linux 的话完全不够用的,所以必须要外接一片RAM 芯片,I.MX6U 支持LPDDR2、LPDDR3/DDR3,I.MX6U-ALPHA开发板上选择的是DDR3(我自己电脑买的内存条就是DDR4的),本章就来学习如何驱动I.MX6U-ALPHA 开发板上的这片DDR3。

在正式学习DDR3 内存之前,我们要先了解一下DDR 内存的发展历史,通过对比SRAM、SDRAM、DDR、DDDR2 和DDR3 的区别,有助于我们更加深入的理解什么是DDR。

何为RAM 和ROM

相信大家在购买手机、电脑等电子设备的时候,通常都会听到RAM、ROM、硬盘等概念,很多人都是一头雾水的。普通用户区分不清楚RAM、ROM 到可以理解,但是作为一个嵌入式Linux 开发者,要是不清楚什么是RAM、什么是ROM 就绝对不行!RAM 和ROM 专业的解释如下:

- RAM:随机存储器,可以随时进行读写操作,速度很快,掉电以后数据会丢失。比如内存条、SRAM、SDRAM、DDR 等都是RAM。RAM 一般用来保存程序数据、中间结果,比如我们在程序中定义了一个变量a,然后对这个a 进行读写操作,示例代码如下:

int a;

a = 10;

a 是一个变量,我们需要很方便的对这个变量进行读写操作,方法就是直接“a”进行读写操作,不需要在乎具体的读写过程。我们可以随意的对RAM 中任何地址的数据(ROM需要地址概念,RAM随机就随机在地址上)进行读写操作,非常方便。

- ROM:只读存储器,笔者认为目前“只读存储器”这个定义不准确。比如我们买手机,通常会告诉你这个手机是4+64 或6+128 配置,说的就是RAM 为4GB 或6GB,ROM 为64G 或128GB。但是这个ROM 是Flash,比如EMMC 或UFS 存储器,因为历史原因,很多人还是将Flash 叫做ROM。但是EMMC 和UFS,甚至是NAND Flash,这些都是可以进行写操作的!只是写起来比较麻烦,要先进行擦除,然后再发送要写的地址或扇区,最后才是要写入的数据,学习过STM32,使用过WM25QXX 系列的SPI Flash 的同学应该深有体会。可以看出,相比于RAM,向ROM 或者Flash 写入数据要复杂很多,因此意味着速度就会变慢(相比RAM),但是ROM 和Flash 可以将容量做的很大,而且掉电以后数据不会丢失,适合用来存储资料,比如音乐、图片、视频等信息。

对比:

- RAM 速度快,可以直接和CPU 进行通信,但是掉电以后数据会丢失,容量不容易做大(和同价格的Flash 相比)。

- ROM(目前来说,更适合叫做Flash)速度虽然慢,但是容量大、适合存储数据。

对于正点原子的I.MX6U-ALPHA 开发板而言,256MB/512MB 的DDR3 就是RAM,而512MB NANF Flash 或8GB EMMC 就是ROM。

SRAM 简介

为什么要讲SRAM 呢?因为大多数的朋友最先接触RAM 芯片都是从SRAM 开始的,因为大量的STM32 单片机开发板都使用到了SRAM,比如F103、F407 等,基本都会外扩一个512KB 或1MB 的SRAM 的,因为STM32F103/F407 内部RAM 比较小,在一些比较耗费内存的应用中会出现内存捉紧的情况,比如emWin 做UI 界面。我们简单回顾一下SRAM,如果想要详细的了解SRAM 请阅读正点原子STM32F103 战舰开发板的开发指南。

SRAM 的全称叫做Static Random-Access Memory,也就是静态随机存储器,这里的“静态”说的就是只要SRAM 上电,那么SRAM 里面的数据就会一直保存着,直到SRAM 掉电。对于RAM 而言需要可以随机的读取任意一个地址空间内的数据,因此采用了地址线和数据线分离的方式。

这里以STM32F103/F407 开发板常用的IS62WV51216 这颗SRAM 芯片为例简单的讲解一下SRAM,这是一颗16 位宽(数据位为16 位)、1MB 大小的SRAM,芯片框图如图23.1.2.1所示:

图23.1.2.1 主要分为三部分,我们依次来看一下这三部分:

①、地址线

这部分是地址线,一共A0~A18,也就是19 根地址线,因此可访问的地址大小就是2^19=524288=512KB。不是说IS62WV51216 是个1MB 的SRAM 吗?为什么地址空间只有512KB?前面我们说了IS62WV51216 是16 位宽的,也就是一次访问2 个字节,因此需要对512KB 进行乘2处理,得到512KB*2=1MB。位宽的话一般有8 位/16 位/32 位,根据实际需求选择即可,一般都是根据处理器的SRAM 控制器位宽来选择SRAM 位宽。

②、数据线

这部分是SRAM 的数据线,根据SRAM 位宽的不同,数据线的数量要不同,8 位宽就有8根数据线,16 位宽就有16 根数据线,32 位宽就有32 根数据线。IS62WV51216 是一个16 位宽的SRAM,因此就有16 根数据线,一次访问可以访问16bit 的数据,也就是2 个字节。因此就有高字节和低字节数据之分,其中IO0~IO7 是低字节数据,IO8~IO15 是高字节数据。

③、控制线

SRAM 要工作还需要一堆的控制线:

- CS2 和CS1是片选信号,低电平有效,在一个系统中可能会有多片SRAM(目的是为了扩展SRAM 大小或位宽),这个时候就需要CS 信号来选择当前使用哪片SRAM。另外,有的SRAM 内部其实是由两片SRAM 拼接起来的,因此就会提供两个片选信号。

- OE 是输出使能信号,低电平有效,也就是主控从SRAM 读取数据。

- WE 是写使能信号,低电平有效,也就是主控向SRAM 写数据。

- UB 和LB 信号,前面我们已经说了,IS62WV51216 是个16 位宽的SRAM,分为高字节和低字节,那么如何来控制读取高字节数据还是低字节数据呢?这个就是UB 和LB 这两个控制线的作用,这两根控制线都是低电平有效。UB 为低电平的话表示访问高字节,LB 为低电平的话表示访问低字节(也就是前面讲的 IO0~ IO7 是低字节数据,IO8~IO15 是高字节数据)。关于IS62WV51216 的简单原理就讲解到这里。

【缺点】那么SRAM 有什么缺点没有?那必须有的啊,要不然就不可能有本章教程了,SRAM 最大的缺点就是成本高!价格高,大家可以在淘宝上搜索一下IS62WV51216 这个仅仅只有1MB大小的SRAM 售价为多少,大概为5,6块钱。大家再搜索一下32MB 的SDRAM 多钱,以华邦的W9825G6KH 为例,大概4,5 块钱,可以看出SDRAM 比SRAM 容量大,但是价格更低。

【优点】SRAM 突出的优点就是无需刷新(SDRAM 需要刷新,后面会讲解),读写速度快(和CPU频率一致 )!所以SRAM通常作为SOC 的内部RAM 使用或Cache 使用,比如STM32 内存的RAM 或I.MX6U 内部的OCRAM 都是SRAM。

SDRAM 简介

前面给大家简单讲解了SRAM,可以看出SRAM 最大的缺点就是价格高、容量小!但是应用对于内存的需求越来越高,必须提供大内存解决方案。为此半导体厂商想了很多办法,提出了很多解决方法,最终SDRAM 应运而生,得到推广。

SDRAM 全称是Synchronous Dynamic Random Access Memory,翻译过来就是同步动态随机存储器,“同步”的意思是SDRAM 工作需要时钟线,“动态”的意思是SDRAM 中的数据需要不断的刷新来保证数据不会丢失,“随机”的意思就是可以读写任意地址的数据。

与SRAM 相比,SDRAM 集成度高、功耗低、成本低、适合做大容量存储,但是需要定时刷新来保证数据不会丢失。因此SDRAM 适合用来做内存条,SRAM 适合做高速缓存或MCU内部的RAM。SDRAM 目前已经发展到了第四代,分别为:SDRAM、DDR SDRAM、DDR2SDRAM、DDR3 SDRAM、DDR4 SDRAM。STM32F429/F767/H743 等芯片支持SDRAM,学过

STM32F429/F767/H743 的朋友应该知道SDRAM。

这里我们就以STM32 开发板最常用的华邦W9825G6KH 为例,W9825G6KH 是一款16 位宽(数据位为16 位)、32MB 的SDRAM、速度一般为133MHz、166MHz 或200MHz。W9825G6KH 框图如图23.1.3.1 所示:

①、控制线(时钟、片选)

SDRAM 也需要很多控制线,我们依次来看一下:

- CLK:时钟线,SDRAM 是同步动态随机存储器,“同步”的意思就是时钟,因此需要一根额外的时钟线,这是和SRAM 最大的不同,SRAM 没有时钟线。

- CKE:时钟使能信号线,SRAM 没有CKE 信号。

- CS:片选信号,这个和SRAM 一样,都有片选信号。

- RAS:行选通信号,低电平有效,SDRAM 和SRAM 的寻址方式不同,SDRAM 按照行、列来确定某个具体的存储区域。因此就有行地址和列地址之分,行地址和列地址共同复用同一组地址线,要访问某一个地址区域,必须要发送行地址和列地址,指定要访问哪一行?哪一列?

- RAS 是行选通信号,表示要发送行地址,行地址和列地址访问方式如下图23.1.3.2 所示。

- CAS:列选通信号,和RAS 类似,低电平有效,选中以后就可以发送列地址了。

- WE:写使能信号,低电平有效。

②、A10 地址线

A10 是地址线,那么这里为什么要单独将A10 地址线给提出来呢?因为A10 地址线还有另外一个作用,A10 还控制着Auto-precharge,也就是预充电。这里又提到了预充电的概念,SDRAM芯片内部会分为多个BANK,关于BANK 我们稍后会讲解。SDRAM 在读写完成以后,如果要对同一个BANK 中的另一行进行寻址操作就必须将原来有效的行关闭,然后发送新的行/列地

址,关闭现在工作的行,准备打开新行的操作就叫做预充电。一般SDSRAM 都支持自动预充电的功能。

③、地址线

对于W9825G6KH 来说一共有A0~A12,共13 根地址线,但是我们前面说了SDRAM 寻址是按照行地址和列地址来访问的,因此这A0~A12 包含了行地址和列地址。不同的SDRAM 芯片,根据其位宽、容量等的不同,行列地址数是不同的,这个在SDRAM 的数据手册里面会也清楚的。比如W9825G6KH 的A0~ A8 是列地址,一共9 位列地址,A0~A12 是行地址,一共13位,因此可寻址范围为:29*213=4194304B=4MB,W9825G6KH 为16 位宽(2 个字节),因此还需要对4MB 进行乘2 处理,得到4*2=8MB,但是W9825G6KH 是一个32MB 的SDRAM 啊, 为什么算出来只有8MB,仅仅为实际容量的1/4。不要急,这个就是我们接下来要讲的BANK,8MB 只是一个BANK 的容量,W9825G6KH 一共有4 个BANK。

④、BANK 选择线

BS0 和BS1 是BANK 选择信号线(选择哪一块),在一片SDRAM 中因为技术、成本等原因,不可能做一个全容量的BANK。而且,因为SDRAM 的工作原理,单一的BANK 会带来严重的寻址冲突,减低内存访问效率。为此,人们在一片SDRAM 中分割出多块BANK,一般都是2 的n 次方,比如2,4,8 等。图23.1.1.2 中的⑤就是W9825G6KH 的4 个BANK 示意图,每个SDRAM

数据手册里面都会写清楚自己是几BANK。前面我们已经计算出来了一个BANK 的大小为8MB,那么四个BANK 的总容量就是8MB*4=32MB。

既然有4 个BANK,那么在访问的时候就需要告诉SDRAM,我们现在需要访问哪个BANK,BS0 和BS1 就是为此而生的,4 个BANK 刚好2 根线,如果是8 个BANK 的话就需要三根线,也就是BS0~BS2。BS0、BS1 这两个线也是SRAM 所没有的。

⑤、BANK 区域

关于BANK 的概念前面已经讲过了,这部分就是W9825G6KH 的4 个BANK 区域。这个概念也是SRAM 所没有的。

⑥、数据线

W9825G6KH 是16 位宽的SDRAM,因此有16 根数据线,DQ0~DQ15,不同的位宽其数据线数量不同,这个和SRAM 是一样的。

⑦、高低字节选择

W9825G6KH 是一个16 位的SDRAM,因此就分为低字节数据和高字节数据,LDQM 和UDQM 就是低字节和高字节选择信号,这个也和SRAM 一样。

DDR 简介

终于到了DDR 内存了,DDR 内存是SDRAM 的升级版本,SDRAM 分为SDR SDRAM、DDR SDRAM、DDR2 SDRAM、DDR3 SDRAM、DDR4 SDRAM。可以看出DDR 本质上还是SDRAM,只是随着技术的不断发展,DDR 也在不断的更新换代。

先来看一下DDR,也就是DDR1,人们对于速度的追求是永无止境的,当发现SDRAM 的速度不够快的时候人们就在思考如何提高SDRAM 的速度,DDR SDRAM 由此诞生。DDR 全称是Double Data Rate SDRAM,也就是双倍速率SDRAM,看名字就知道DDR 的速率(数据传输速率)比SDRAM 高1 倍!这1 倍的速度不是简简单单的将CLK 提高1 倍,SDRAM 在一个CLK 周期传输一次数据,DDR 在一个CLK 周期传输两次数据,也就是在上升沿和下降沿各传输一次数据,这个概念叫做预取(prefetch),相当于DDR 的预取为2bit,因此DDR 的速度直接加倍!比如SDRAM 速度一般是133 ~ 200MHz,对应的传输速度就是133 ~ 200MT/s,在描述DDR 速度的时候一般都使用MT/s,也就是每秒多少兆次数据传输。133MT/S 就是每秒133M 次数据传输,MT/s 描述的是单位时间内传输速率。同样133 ~ 200MHz的频率,DDR 的传输速度就变为了266~400MT/S,所以大家常说的DDR266、DDR400 就是这么来的。

DDR2 在DDR 基础上进一步增加预取(prefetch),增加到了4bit,相当于比DDR 多读取一倍的数据,因此DDR2 的数据传输速率就是533~800MT/s,这个也就是大家常说的DDR2 533、DDR2 800。当然了,DDR2 还有其他速度,这里只是说最常见的几种。

DDR3 在DDR2 的基础上将预取(prefetch)提高到8bit,因此又获得了比DDR2 高一倍的传输速率,因此在总线时钟同样为266~ 400MHz 的情况下,DDR3 的传输速率就是1066~1600MT/S。I.MX6U 的MMDC 外设用于连接DDR,支持LPDDR2、DDR3、DDR3L,最高支持16 位数据位宽。总线速度为400MHz(实际是396MHz),数据传输速率最大为800MT/S。

这里我们讲一下LPDDR3、DDR3 和DDR3L 的区别,这三个都是DDR3,但是区别主要在于工作电压,LPDDR3叫做低功耗DDR3,工作电压为1.2V。DDR3 叫做标压DDR3,工作电压为1.5V,一般台式内存条都是DDR3。DDR3L 是低压DDR3,工作电压为1.35V,一般手机、嵌入式、笔记本等都使用DDR3L。

正点原子的I.MX6U-ALPHA 开发板上接了一个256MB/512MB 的DDR3L,16 位宽,型号为NT5CC128M16JR/MT5CC256M16EP,nanya 公司出品的,分为对应256MB 和512MB 容量。

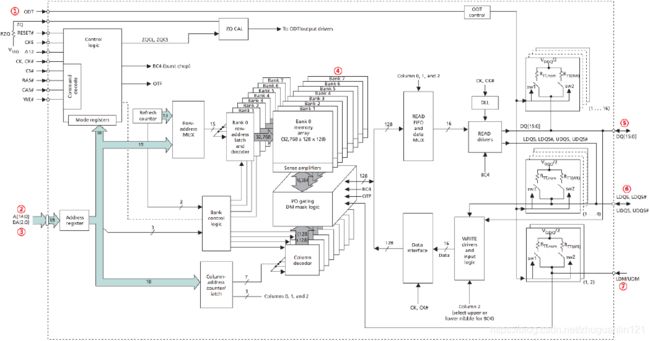

EMMC 核心板上用的512MB 容量的DDR3L,NAND 核心板上用的256MB 容量的DDR3L。本讲解我们就以EMMC 核心板上使用的NT5CC256M16EP-EK 为例讲解一下DDR3。可以到nanya官网去查找一下此型号,信息如图23.1.4.1 所示:

从图23.1.4.1 可以看出,NT5CC256M16EP-EK 是一款容量为4Gb,也就是512MB 大小、16 位宽、1.35V、传输速率为1866MT/S 的DDR3L 芯片。NT5CC256M16EP-EK 的数据手册没有在nanya 官网找到,但是找到了NT5CC256M16ER-EK 数据手册,在官网上没有看出这两个有什么区别,因此我们就直接用NT5CC256M16ER-EK 的数据手册。数据手册已经放到了开发板光盘中,路径为:6、硬件资料-》1、芯片资料-》NT5CC256M16EP-EK.pdf。但是数据手册并没有给出DDR3L 对的结构框图,这里我就直接用镁光MT41K256M16 数据手册里面的结构框图了,都是一样的,DDR3L 结构框图如图23.1.4.2 所示:

从图23.1.4.2 可以看出,DDR3L 和SDRAM 对的结构框图很类似,但是还是有点区别。

①、控制线

ODT:片上终端使能,ODT 使能和禁止片内终端电阻。

ZQ:输出驱动校准的外部参考引脚,此引脚应该外接一个240 欧的电阻到VSSQ 上,一般就是直接接地了。

RESET:复位引脚,低电平有效。

CKE:时钟使能引脚。

A12:A12 是地址引脚,但是有也有另外一个功能,因此也叫做BC 引脚,A12 会在READ和WRITE 命令期间被采样,以决定burst chop 是否会被执行。

CK 和CK#:时钟信号,DDR3 的时钟线是差分时钟线,所有的控制和地址信号都会在CK对的上升沿和CK#的下降沿交叉处被采集。

CS#:片选信号,低电平有效。

RAS#、CAS#和WE#:行选通信号、列选通信号和写使能信号。

②、地址线

A[14:0]为地址线,A0 ~ A14,一共15 根地址线,根据NT5CC256M16ER-EK 的数据手册可知,列地址为A0~ A9,共10 根,行地址为A0~A14,共15 根,因此一个BANK 的大小就是 2^10(地址行)* 2^15(地址列)*2(16位宽 2字节) = 32MB * 2=64MB,根据图23.1.4.2 可知一共有8个BANK,因此DDR3L的容量就是64 * 8=512MB。

③、BANK 选择线

一片DDR3 有8 个BANK,因此需要3 个线才能实现8 个BANK 的选择,BA0~BA2 就是用于完成BANK 选择的。

④、BANK 区域

DDR3 一般都是8 个BANK 区域。

⑤、数据线

因为是16 位宽的,因此有16 根数据线,分别为DQ0~DQ15。

⑥、数据选通引脚

DQS 和DQS#是数据选通引脚,为差分信号,读的时候是输出,写的时候是输入。LDQS(有的叫做DQSL)和LDQS#(有的叫做DQSL#)对应低字节,也就是DQ0~ 7,UDQS(有的叫做DQSU)和UDQS#(有的叫做DQSU#),对应高字节,也就是DQ8~15。

⑦、数据输入屏蔽引脚

DM 是写数据输入屏蔽引脚。

关于DDR3L 的框图就讲解到这里,想要详细的了解DDR3 的组成,请阅读相应对的数据手册。

内存,RAM(DDR),ROM(EEPROM、flash),存储卡(emmc,sd,tf)以及Cache的区别与联系

参考博文