2022-03-24 RK3566 MIPI屏 调试记录,panel-init-sequence 命令格式介绍

一、Single-channel mipi屏的硬件连接如下:

二、根据屏厂给的初始化代码配置dts了,屏厂给的初始化代码分几种形式,这个文章里面RK PX30_android8.1的mipi屏调试_要不要买菜!的博客-CSDN博客 有比较详细的介绍。

三、RK dts里面panel-init-sequence 命令格式介绍。

四、我现在调试的屏幕厂家ST7701S_5.0BOE_IPS_2LINE初始化给的初始化如下:

HSYNC:10

HBP:10

HADR:480

HFP:10

VSYNC:4

VBP:6

VADR:854

VFP:14

PCLK:27

U16 B0[17]={0xB0,0x00,0x0B,0x10,0x0D,0x11,0x06,0x01,0x08,0x08,0x1D,0x04,0x10,0x10,0x27,0x30,0x19};

U16 B1[17]={0xB1,0x00,0x0B,0x14,0x0C,0x11,0x05,0x03,0x08,0x08,0x20,0x04,0x13,0x10,0x28,0x30,0x19};

U16 E1[12]={0xE1,0x05,0x00,0x00,0x00,0x04,0x00,0x00,0x00,0x00,0x20,0x20};

U16 E2[14]={0xE2,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00};

U16 E5[17]={0xE5,0x07,0x34,0xA0,0xA0,0x05,0x34,0xA0,0xA0,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00};

U16 E8[17]={0xE8,0x06,0x34,0xA0,0xA0,0x04,0x34,0xA0,0xA0,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00};

U16 ED[17]={0xED,0xAA,0x54,0x0B,0xBF,0xFF,0xFF,0xFF,0xFF,0xFF,0xFF,0xFF,0xFF,0xFB,0xB0,0x45,0xAA};

Generic_Long_Write_5P(0xFF,0x77,0x01,0x00,0x00,0x10);

Generic_Long_Write_2P(0xC0,0xE9,0x03);//display line setting //800

Generic_Long_Write_2P(0xC1,0x08,0x02); //Porch control

Generic_Long_Write_2P(0xC2,0x31,0x08);

Generic_Short_Write_1P(0xCC,0x10);

Generic_Long_Write_FIFO(17,B0);

Generic_Long_Write_FIFO(17,B1);

Generic_Long_Write_5P(0xFF,0x77,0x01,0x00,0x00,0x11);

Generic_Short_Write_1P(0xB0,0x35);//4D

Generic_Short_Write_1P(0xB1,0x38);//21 71 VCOM

Generic_Short_Write_1P(0xB2,0x02); //VGH VOLTAGE SETTING

Generic_Short_Write_1P(0xB3,0x80);

Generic_Short_Write_1P(0xB5,0x4E); //VGL VOLTAGE SETTING

Generic_Short_Write_1P(0xB7,0x85);

Generic_Short_Write_1P(0xB8,0x20);

Generic_Short_Write_1P(0xB9,0x10);

//Generic_Short_Write_1P(0xC0,0x90);

Generic_Short_Write_1P(0xC1,0x78);

Generic_Short_Write_1P(0xC2,0x78);

Generic_Short_Write_1P(0xD0,0x88);

Delay (100);

//Generic_Short_Write_1P(0xEE,0x42);

Generic_Long_Write_3P(0xE0,0x00,0x00,0x02);

Generic_Long_Write_FIFO(12,E1);

Generic_Long_Write_FIFO(14,E2);

Generic_Long_Write_4P(0xE3,0x00,0x00,0x33,0x00);

Generic_Long_Write_2P(0xE4,0x22,0x00);

Generic_Long_Write_FIFO(17,E5);

Generic_Long_Write_4P(0xE6,0x00,0x00,0x33,0x00);

Generic_Long_Write_2P(0xE7,0x22,0x00);

Generic_Long_Write_FIFO(17,E8);

Generic_Long_Write_7P(0xEB,0x02,0x00,0x10,0x10,0x00,0x00,0x00);

Generic_Long_Write_2P(0xEC,0x02,0x00);

Generic_Long_Write_FIFO(17,ED);

//Generic_Long_Write_6P(0xeF,0x08,0x08,0x08,0x40,0x3F,0x64);

//Generic_Long_Write_5P(0xFF,0x77,0x01,0x00,0x00,0x13);

//Generic_Short_Write_1P(0x29,0x00);

//Generic_Long_Write_2P(0xE8,0x00,0x0E);

Generic_Long_Write_5P(0xFF,0x77,0x01,0x00,0x00,0x00);

Generic_Short_Write_1P(0x36,0x00);

DCS_Short_Write_NP(0x11);

Delay(120);

//Generic_Long_Write_5P(0xFF,0x77,0x01,0x00,0x00,0x13);

//Generic_Long_Write_2P(0xE8,0x00,0x0C);

Delay(10);

//Generic_Long_Write_2P(0xE8,0x00,0x00);

//Generic_Long_Write_5P(0xFF,0x77,0x01,0x00,0x00,0x00);

DCS_Short_Write_NP(0x29);

Delay(20);

五、转换成rk 的命令格式

dsi,lanes = <2>;

panel-init-sequence = [

39 00 06 FF 77 01 00 00 10

39 00 03 C0 E9 03

39 00 03 C1 08 02

39 00 03 C2 31 08

15 00 02 CC 10

39 00 11 B0 00 0B 10 0D 11 06 01 08 08 1D 04 10 10 27 30 19

39 00 11 B1 00 0B 14 0C 11 05 03 08 08 20 04 13 10 28 30 19

39 00 06 FF 77 01 00 00 11

15 00 02 B0 35

15 00 02 B1 38

15 00 02 B2 02

15 00 02 B3 80

15 00 02 B5 4E

15 00 02 B7 85

15 00 02 B8 20

15 00 02 B9 10

15 00 02 C1 78

15 00 02 C2 78

15 64 02 D0 88

39 00 04 E0 00 00 02

39 00 0C E1 05 00 00 00 04 00 00 00 00 20 20

39 00 0E E2 00 00 00 00 00 00 00 00 00 00 00 00 00

39 00 05 E3 00 00 33 00

39 00 03 E4 22 00

39 00 11 E5 07 34 A0 A0 05 34 A0 A0 00 00 00 00 00 00 00 00

39 00 05 E6 00 00 33 00

39 00 03 E7 22 00

39 00 11 E8 06 34 A0 A0 04 34 A0 A0 00 00 00 00 00 00 00 00

39 00 08 EB 02 00 10 10 00 00 00

39 00 03 EC 02 00

39 00 11 ED AA 54 0B BF FF FF FF FF FF FF FF FF FB B0 45 AA

39 00 06 FF 77 01 00 00 00

15 00 02 36 00

05 78 01 11

05 14 01 29

];六、配置的dts如下

&dsi1 {

status = "okay";

//rockchip,lane-rate = <1000>;

panel@0 {

compatible = "aoly,sl008pa21y1285-b00", "simple-panel-dsi";

reg = <0>;

backlight = <&backlight>;

//power-supply=<&vcc_3v3>;

enable-gpios = <&gpio0 RK_PC7 GPIO_ACTIVE_HIGH>;

reset-gpios = <&gpio0 RK_PC5 GPIO_ACTIVE_LOW>;

pinctrl-names = "default";

pinctrl-0 = <&lcd_enable_gpio>, <&lcd_rst_gpio>;

prepare-delay-ms = <120>;

reset-delay-ms = <120>;

init-delay-ms = <120>;

stbyb-delay-ms = <120>;

enable-delay-ms = <120>;

disable-delay-ms = <120>;

unprepare-delay-ms = <120>;

width-mm = <229>;

height-mm = <143>;

dsi,flags = <(MIPI_DSI_MODE_VIDEO | MIPI_DSI_MODE_VIDEO_BURST |

MIPI_DSI_MODE_LPM | MIPI_DSI_MODE_EOT_PACKET)>;

dsi,format = ;

dsi,lanes = <2>;

panel-init-sequence = [

39 00 06 FF 77 01 00 00 10

39 00 03 C0 E9 03

39 00 03 C1 08 02

39 00 03 C2 31 08

15 00 02 CC 10

39 00 11 B0 00 0B 10 0D 11 06 01 08 08 1D 04 10 10 27 30 19

39 00 11 B1 00 0B 14 0C 11 05 03 08 08 20 04 13 10 28 30 19

39 00 06 FF 77 01 00 00 11

15 00 02 B0 35

15 00 02 B1 38

15 00 02 B2 02

15 00 02 B3 80

15 00 02 B5 4E

15 00 02 B7 85

15 00 02 B8 20

15 00 02 B9 10

15 00 02 C1 78

15 00 02 C2 78

15 64 02 D0 88

39 00 04 E0 00 00 02

39 00 0C E1 05 00 00 00 04 00 00 00 00 20 20

39 00 0E E2 00 00 00 00 00 00 00 00 00 00 00 00 00

39 00 05 E3 00 00 33 00

39 00 03 E4 22 00

39 00 11 E5 07 34 A0 A0 05 34 A0 A0 00 00 00 00 00 00 00 00

39 00 05 E6 00 00 33 00

39 00 03 E7 22 00

39 00 11 E8 06 34 A0 A0 04 34 A0 A0 00 00 00 00 00 00 00 00

39 00 08 EB 02 00 10 10 00 00 00

39 00 03 EC 02 00

39 00 11 ED AA 54 0B BF FF FF FF FF FF FF FF FF FB B0 45 AA

39 00 06 FF 77 01 00 00 00

15 00 02 36 00

05 78 01 11

05 14 01 29

];

panel-exit-sequence = [

05 00 01 28

05 00 01 10

];

display-timings {

native-mode = <&timing0>;

timing0: timing0 {

clock-frequency = <27000000>;

hactive = <480>;

vactive = <854>;

hfront-porch = <150>;

hsync-len = <10>;

hback-porch = <10>;

vfront-porch = <14>;

vsync-len = <4>;

vback-porch = <6>;

hsync-active = <1>;

vsync-active = <1>;

de-active = <0>;

pixelclk-active = <1>;

};

};

ports {

#address-cells = <1>;

#size-cells = <0>;

port@0 {

reg = <0>;

panel_in_dsi: endpoint {

remote-endpoint = <&dsi_out_panel>;

};

};

};

};

ports {

#address-cells = <1>;

#size-cells = <0>;

port@1 {

reg = <1>;

dsi_out_panel: endpoint {

remote-endpoint = <&panel_in_dsi>;

};

};

};

};

&dsi1_in_vp0 {

status = "disabled";

};

&dsi1_in_vp1 {

status = "okay";

};

六、reset和enable 都配对,顺利的化就会显示了。

七、调试中遇到的问题

1、clock-frequency 配置的过低的话,会不显示或者显示的画面有闪烁,log也会提示异常。

2、clock-frequency 配置的过高的话,显示的画面会乱,如下:

3、dsi,lanes 配置得不对的话,是不会显示的。

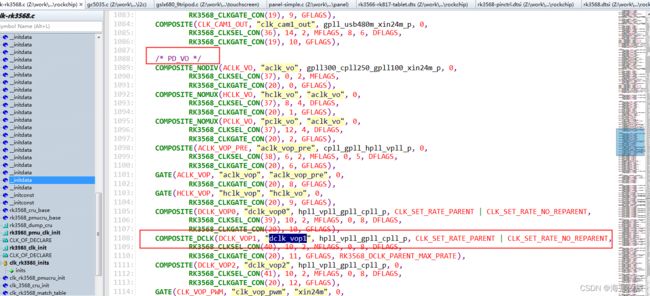

八、/sys/class/drm/card0-DSI-1 目录下查看屏幕的参数,cat d/clk/clk_summary | grep dclk_vop1查看clock-frequency。

九、特别说一下clock-frequency是如何配置的,如何来的。

十、最后上一个调试好的图。

十一、调另外一个屏幕

#define LCD_XSIZE 800

#define LCD_YSIZE 1280

#define LCD_BPP 24 //16 24位选择

#define FRAME_RATE 60

#define LCD_ROTATE 0

#define HBPD 140 //20

#define HFPD 24 //32

#define HSPW 4 //6

#define VBPD 16 //15

#define VFPD 16 //32

#define VSPW 2 //4

/*============================================================================*/

//* VIDCON0

#define VIDOUT (0)

#define L1_DATA16 (4)

#define L0_DATA16 (4)

#define PNRMODE (0)

#define CLKVALUP (1)

#define CLKVAL_F (1) //VCLK = (HCLK or LCD video Clock) / [CLKVAL+1] ( CLKVAL ≥ 1 )

#define CLKDIR (0) //是否分频?【1:使用CLKVAL_F分频】 【0:直接使用时钟源】

#define CLKSEL_F (1) //VCLK时钟源选择 【 0:HCLK】 【 1:EPLL 】 HCLK=133M

#define IVCLK (1) //rVIDCON1寄存器 VCLK极性 【0:上升沿】 【1:下降沿】

// Vclk_MHZ = (hsync_cnt*vclk_cnt*lcd_frame_rate)/1000000;

#define Vclk_MHZ 60 //当时钟源为EPLL的时候 设置此频率

// Vclk_MHZ 目前预定值有 36 48 60 72 84 96 108 120

GP_COMMAD_PA(4);W_D(0xFF);W_D(0x98);W_D(0x81);W_D(0x03);

//GIP_1

GP_COMMAD_PA(2); W_D(0x01); W_D(0x00);

GP_COMMAD_PA(2); W_D(0x02); W_D(0x00);

GP_COMMAD_PA(2); W_D(0x03); W_D(0x5D); //STVA

GP_COMMAD_PA(2); W_D(0x04); W_D(0x17); //STVB

GP_COMMAD_PA(2); W_D(0x05); W_D(0x00); //STVC

GP_COMMAD_PA(2); W_D(0x06); W_D(0x0E); //STVA_Rise

GP_COMMAD_PA(2); W_D(0x07); W_D(0x00); //STVB_Rise

GP_COMMAD_PA(2); W_D(0x08); W_D(0x00); //STVC_Rise

GP_COMMAD_PA(2); W_D(0x09);W_D(0x21); //FTI1R(A)

GP_COMMAD_PA(2); W_D(0x0a); W_D(0x21); //FTI2R(B)

GP_COMMAD_PA(2); W_D(0x0b); W_D(0x00); //FTI3R(C)

GP_COMMAD_PA(2); W_D(0x0c); W_D(0x06); //FTI1F(A)

GP_COMMAD_PA(2); W_D(0x0d); W_D(0x06); //FTI2F(B)

GP_COMMAD_PA(2); W_D(0x0e); W_D(0x00); //FTI2F(C)

GP_COMMAD_PA(2); W_D(0x0f); W_D(0x22); //CLW1(ALR) 前削

GP_COMMAD_PA(2); W_D(0x10); W_D(0x22); //CLW2(ARR) 前削

GP_COMMAD_PA(2); W_D(0x11);W_D(0x00);

GP_COMMAD_PA(2); W_D(0x12); W_D(0x00);

GP_COMMAD_PA(2); W_D(0x13); W_D(0x05); //CLWX(ATF) 后削

GP_COMMAD_PA(2); W_D(0x14); W_D(0x00);

GP_COMMAD_PA(2); W_D(0x15); W_D(0x00); //GPMRi(ALR)

GP_COMMAD_PA(2); W_D(0x16); W_D(0x00); //GPMRii(ARR)

GP_COMMAD_PA(2); W_D(0x17); W_D(0x00); //GPMFi(ALF)

GP_COMMAD_PA(2); W_D(0x18); W_D(0x00); //GPMFii(AFF)

GP_COMMAD_PA(2); W_D(0x19); W_D(0x00);

GP_COMMAD_PA(2); W_D(0x1a); W_D(0x00);

GP_COMMAD_PA(2); W_D(0x1b); W_D(0x00);

GP_COMMAD_PA(2); W_D(0x1c); W_D(0x00);

GP_COMMAD_PA(2); W_D(0x1d); W_D(0x00);

GP_COMMAD_PA(2); W_D(0x1e); W_D(0x40); //CLKA 40自動反 C0手動反(X8參考CLKB)

GP_COMMAD_PA(2); W_D(0x1f); W_D(0xC0); //C0

GP_COMMAD_PA(2); W_D(0x20); W_D(0x0E); //CLKA_Rise

GP_COMMAD_PA(2); W_D(0x21); W_D(0x09); //CLKA_Fall

GP_COMMAD_PA(2); W_D(0x22); W_D(0x0F); //CLKB_Rise(keep toggle需設CLK A後一格)

GP_COMMAD_PA(2); W_D(0x23); W_D(0x00); //CLKB_Fall

GP_COMMAD_PA(2); W_D(0x24); W_D(0x8A); //CLK keep toggle(AL) 8X往左看

GP_COMMAD_PA(2); W_D(0x25); W_D(0x8A); //CLK keep toggle(AR) 8X往左看

GP_COMMAD_PA(2); W_D(0x26); W_D(0x00);

GP_COMMAD_PA(2); W_D(0x27); W_D(0x00);

GP_COMMAD_PA(2); W_D(0x28); W_D(0x77); //CLK Phase

GP_COMMAD_PA(2); W_D(0x29); W_D(0x77); //CLK overlap

GP_COMMAD_PA(2); W_D(0x2a); W_D(0x00);

GP_COMMAD_PA(2); W_D(0x2b); W_D(0x00);

GP_COMMAD_PA(2); W_D(0x2c); W_D(0x02); //GCH R

GP_COMMAD_PA(2); W_D(0x2d); W_D(0x02); //GCL R

GP_COMMAD_PA(2); W_D(0x2e); W_D(0x07); //GCH F 0B

GP_COMMAD_PA(2); W_D(0x2f); W_D(0x07); //GCL F 0B

GP_COMMAD_PA(2); W_D(0x30); W_D(0x00);

GP_COMMAD_PA(2); W_D(0x31); W_D(0x00);

GP_COMMAD_PA(2); W_D(0x32); W_D(0x22); //GCH/L ext2/1行為 5E 01:31 5E 00:42

GP_COMMAD_PA(2); W_D(0x33); W_D(0x00);

GP_COMMAD_PA(2); W_D(0x34); W_D(0x00); //VDD1&2 non-overlap 04:2.62us

GP_COMMAD_PA(2); W_D(0x35); W_D(0x0A); //GCH/L 區間 00:VS前 01:VS後 10:跨VS 11:frame中

GP_COMMAD_PA(2); W_D(0x36); W_D(0x00);

GP_COMMAD_PA(2); W_D(0x37); W_D(0x08); //GCH/L

GP_COMMAD_PA(2); W_D(0x38); W_D(0x3C); //VDD1&2 toggle 1sec

GP_COMMAD_PA(2); W_D(0x39); W_D(0x00);

GP_COMMAD_PA(2); W_D(0x3a); W_D(0x00);

GP_COMMAD_PA(2); W_D(0x3b); W_D(0x00);

GP_COMMAD_PA(2); W_D(0x3c); W_D(0x00);

GP_COMMAD_PA(2); W_D(0x3d); W_D(0x00);

GP_COMMAD_PA(2); W_D(0x3e); W_D(0x00);

GP_COMMAD_PA(2); W_D(0x3f); W_D(0x00);

GP_COMMAD_PA(2); W_D(0x40); W_D(0x00);

GP_COMMAD_PA(2); W_D(0x41); W_D(0x00);

GP_COMMAD_PA(2); W_D(0x42); W_D(0x00);

GP_COMMAD_PA(2); W_D(0x43); W_D(0x08); //GCH/L

GP_COMMAD_PA(2); W_D(0x44); W_D(0x00);

//GIP_2

GP_COMMAD_PA(2); W_D(0x50); W_D(0x01);

GP_COMMAD_PA(2); W_D(0x51); W_D(0x23);

GP_COMMAD_PA(2); W_D(0x52); W_D(0x45);

GP_COMMAD_PA(2); W_D(0x53); W_D(0x67);

GP_COMMAD_PA(2); W_D(0x54); W_D(0x89);

GP_COMMAD_PA(2); W_D(0x55); W_D(0xab);

GP_COMMAD_PA(2); W_D(0x56); W_D(0x01);

GP_COMMAD_PA(2); W_D(0x57); W_D(0x23);

GP_COMMAD_PA(2); W_D(0x58); W_D(0x45);

GP_COMMAD_PA(2); W_D(0x59); W_D(0x67);

GP_COMMAD_PA(2); W_D(0x5a); W_D(0x89);

GP_COMMAD_PA(2); W_D(0x5b); W_D(0xab);

GP_COMMAD_PA(2); W_D(0x5c); W_D(0xcd);

GP_COMMAD_PA(2); W_D(0x5d); W_D(0xef);

//GIP_3

GP_COMMAD_PA(2); W_D(0x5e); W_D(0x00);

GP_COMMAD_PA(2); W_D(0x5f); W_D(0x02); //FW_CGOUT_L[1] VGL

GP_COMMAD_PA(2); W_D(0x60); W_D(0x02); //FW_CGOUT_L[2] VGL

GP_COMMAD_PA(2); W_D(0x61); W_D(0x06); //FW_CGOUT_L[3] VST_R

GP_COMMAD_PA(2); W_D(0x62); W_D(0x0F); //FW_CGOUT_L[4] XCLK_R4

GP_COMMAD_PA(2); W_D(0x63); W_D(0x0F); //FW_CGOUT_L[5] XCLK_R4

GP_COMMAD_PA(2); W_D(0x64); W_D(0x13); //FW_CGOUT_L[6] CLK_R4

GP_COMMAD_PA(2); W_D(0x65); W_D(0x13); //FW_CGOUT_L[7] CLK_R4

GP_COMMAD_PA(2); W_D(0x66); W_D(0x0E); //FW_CGOUT_L[8] XCLK_R3

GP_COMMAD_PA(2); W_D(0x67); W_D(0x0E); //FW_CGOUT_L[9] XCLK_R3

GP_COMMAD_PA(2); W_D(0x68); W_D(0x12); //FW_CGOUT_L[10] CLK_R3

GP_COMMAD_PA(2); W_D(0x69); W_D(0x12); //FW_CGOUT_L[11] CLK_R3

GP_COMMAD_PA(2); W_D(0x6a); W_D(0x0D); //FW_CGOUT_L[12] XCLK_R2

GP_COMMAD_PA(2); W_D(0x6b); W_D(0x0D); //FW_CGOUT_L[13] XCLK_R2

GP_COMMAD_PA(2); W_D(0x6c); W_D(0x11); //FW_CGOUT_L[14] CLK_R2

GP_COMMAD_PA(2); W_D(0x6d); W_D(0x11); //FW_CGOUT_L[15] CLK_R2

GP_COMMAD_PA(2); W_D(0x6e); W_D(0x0C); //FW_CGOUT_L[16] XCLK_R1

GP_COMMAD_PA(2); W_D(0x6f); W_D(0x0C); //FW_CGOUT_L[17] XCLK_R1

GP_COMMAD_PA(2); W_D(0x70); W_D(0x10); //FW_CGOUT_L[18] CLK_R1

GP_COMMAD_PA(2); W_D(0x71); W_D(0x10); //FW_CGOUT_L[19] CLK_R1

GP_COMMAD_PA(2); W_D(0x72); W_D(0x00); //FW_CGOUT_L[20] D2U 00

GP_COMMAD_PA(2); W_D(0x73); W_D(0x16); //FW_CGOUT_L[21] U2D 01

GP_COMMAD_PA(2); W_D(0x74); W_D(0x08); //FW_CGOUT_L[22] VEND

GP_COMMAD_PA(2); W_D(0x75); W_D(0x02); //BW_CGOUT_L[1]

GP_COMMAD_PA(2); W_D(0x76); W_D(0x02); //BW_CGOUT_L[2]

GP_COMMAD_PA(2); W_D(0x77); W_D(0x08); //BW_CGOUT_L[3]

GP_COMMAD_PA(2); W_D(0x78); W_D(0x0F); //BW_CGOUT_L[4]

GP_COMMAD_PA(2); W_D(0x79); W_D(0x0F); //BW_CGOUT_L[5]

GP_COMMAD_PA(2); W_D(0x7a); W_D(0x13); //BW_CGOUT_L[6]

GP_COMMAD_PA(2); W_D(0x7b); W_D(0x13); //BW_CGOUT_L[7]

GP_COMMAD_PA(2); W_D(0x7c); W_D(0x0E); //BW_CGOUT_L[8]

GP_COMMAD_PA(2); W_D(0x7d); W_D(0x0E); //BW_CGOUT_L[9]

GP_COMMAD_PA(2); W_D(0x7e); W_D(0x12); //BW_CGOUT_L[10]

GP_COMMAD_PA(2); W_D(0x7f); W_D(0x12); //BW_CGOUT_L[11]

GP_COMMAD_PA(2); W_D(0x80); W_D(0x0D); //BW_CGOUT_L[12]

GP_COMMAD_PA(2); W_D(0x81); W_D(0x0D); //BW_CGOUT_L[13]

GP_COMMAD_PA(2); W_D(0x82); W_D(0x11); //BW_CGOUT_L[14]

GP_COMMAD_PA(2); W_D(0x83); W_D(0x11); //BW_CGOUT_L[15]

GP_COMMAD_PA(2); W_D(0x84); W_D(0x0C); //BW_CGOUT_L[16]

GP_COMMAD_PA(2); W_D(0x85); W_D(0x0C); //BW_CGOUT_L[17]

GP_COMMAD_PA(2); W_D(0x86); W_D(0x10); //BW_CGOUT_L[18]

GP_COMMAD_PA(2); W_D(0x87); W_D(0x10); //BW_CGOUT_L[19]

GP_COMMAD_PA(2); W_D(0x88); W_D(0x17); //BW_CGOUT_L[20]

GP_COMMAD_PA(2); W_D(0x89); W_D(0x01); //BW_CGOUT_L[21]

GP_COMMAD_PA(2); W_D(0x8A); W_D(0x06); //BW_CGOUT_L[22]

//CMD_Page 4

GP_COMMAD_PA(4); W_D(0xFF); W_D(0x98); W_D(0x81); W_D(0x04);

GP_COMMAD_PA(2); W_D(0x6E); W_D(0x2A); //VGH 15V

GP_COMMAD_PA(2); W_D(0x6F); W_D(0x37); // reg vcl + pumping ratio VGH=3x VGL=-3x

GP_COMMAD_PA(2); W_D(0x3A); W_D(0xA4); //POWER SAVING

GP_COMMAD_PA(2); W_D(0x8D); W_D(0x25); //1A //VGL -11V

GP_COMMAD_PA(2); W_D(0x87); W_D(0xBA); //ESD

GP_COMMAD_PA(2); W_D(0xB2); W_D(0xD1);

GP_COMMAD_PA(2); W_D(0x88); W_D(0x0B);

GP_COMMAD_PA(2); W_D(0x38); W_D(0x01);

GP_COMMAD_PA(2); W_D(0x39); W_D(0x00);

GP_COMMAD_PA(2); W_D(0xB5); W_D(0x07); //gamma bias

GP_COMMAD_PA(2); W_D(0x31); W_D(0x75); //source bias

GP_COMMAD_PA(2); W_D(0x3B); W_D(0x98);

//CMD_Page 1

GP_COMMAD_PA(4); W_D(0xFF); W_D(0x98); W_D(0x81); W_D(0x01);

GP_COMMAD_PA(2); W_D(0x22); W_D(0x0A); //BGR SS

GP_COMMAD_PA(2); W_D(0x31); W_D(0x0A); //Z inversion

GP_COMMAD_PA(2); W_D(0x35); W_D(0x07); //CHOPPER

GP_COMMAD_PA(2); W_D(0x52); W_D(0x00); //VCOM1[8]

GP_COMMAD_PA(2); W_D(0x53); W_D(0x73); //3D //VCOM1[7:0]

GP_COMMAD_PA(2); W_D(0x54); W_D(0x00); //VCOM2[8]

GP_COMMAD_PA(2); W_D(0x55); W_D(0x3D); //VCOM2[7:0]

GP_COMMAD_PA(2); W_D(0x50); W_D(0xD0); //D0=VREG1OUT 5.208V 95=VREG1OUT 4.5V

GP_COMMAD_PA(2); W_D(0x51); W_D(0xCB); //CB=VREG2OUT -5.208V 90=VREG2OUT -4.5V

GP_COMMAD_PA(2); W_D(0x60); W_D(0x14); //SDT=2.0

GP_COMMAD_PA(2); W_D(0x62); W_D(0x01); //EQ

GP_COMMAD_PA(2); W_D(0x63); W_D(0x01); //PC

//============Gamma START=============

//Pos Register

GP_COMMAD_PA(2); W_D(0xA0); W_D(0x00);

GP_COMMAD_PA(2); W_D(0xA1); W_D(0x18);

GP_COMMAD_PA(2); W_D(0xA2); W_D(0x28);

GP_COMMAD_PA(2); W_D(0xA3); W_D(0x17);

GP_COMMAD_PA(2); W_D(0xA4); W_D(0x1C);

GP_COMMAD_PA(2); W_D(0xA5); W_D(0x30);

GP_COMMAD_PA(2); W_D(0xA6); W_D(0x24);

GP_COMMAD_PA(2); W_D(0xA7); W_D(0x24);

GP_COMMAD_PA(2); W_D(0xA8); W_D(0x85);

GP_COMMAD_PA(2); W_D(0xA9); W_D(0x1C);

GP_COMMAD_PA(2); W_D(0xAA); W_D(0x26);

GP_COMMAD_PA(2); W_D(0xAB); W_D(0x66);

GP_COMMAD_PA(2); W_D(0xAC); W_D(0x19);

GP_COMMAD_PA(2); W_D(0xAD); W_D(0x18);

GP_COMMAD_PA(2); W_D(0xAE); W_D(0x4F);

GP_COMMAD_PA(2); W_D(0xAF); W_D(0x24);

GP_COMMAD_PA(2); W_D(0xB0); W_D(0x2B);

GP_COMMAD_PA(2); W_D(0xB1); W_D(0x4A);

GP_COMMAD_PA(2); W_D(0xB2); W_D(0x59);

GP_COMMAD_PA(2); W_D(0xB3); W_D(0x23);

//Neg Register

GP_COMMAD_PA(2); W_D(0xC0); W_D(0x00);

GP_COMMAD_PA(2); W_D(0xC1); W_D(0x18);

GP_COMMAD_PA(2); W_D(0xC2); W_D(0x28);

GP_COMMAD_PA(2); W_D(0xC3); W_D(0x17);

GP_COMMAD_PA(2); W_D(0xC4); W_D(0x1B);

GP_COMMAD_PA(2); W_D(0xC5); W_D(0x2F);

GP_COMMAD_PA(2); W_D(0xC6); W_D(0x22);

GP_COMMAD_PA(2); W_D(0xC7); W_D(0x22);

GP_COMMAD_PA(2); W_D(0xC8); W_D(0x87);

GP_COMMAD_PA(2); W_D(0xC9); W_D(0x1C);

GP_COMMAD_PA(2); W_D(0xCA); W_D(0x27);

GP_COMMAD_PA(2); W_D(0xCB); W_D(0x66);

GP_COMMAD_PA(2); W_D(0xCC); W_D(0x19);

GP_COMMAD_PA(2); W_D(0xCD); W_D(0x1A);

GP_COMMAD_PA(2); W_D(0xCE); W_D(0x4E);

GP_COMMAD_PA(2); W_D(0xCF); W_D(0x24);

GP_COMMAD_PA(2); W_D(0xD0); W_D(0x2A);

GP_COMMAD_PA(2); W_D(0xD1); W_D(0x4C);

GP_COMMAD_PA(2); W_D(0xD2); W_D(0x5A);

GP_COMMAD_PA(2); W_D(0xD3); W_D(0x23);

//============ Gamma END===========

//CMD_Page 0

GP_COMMAD_PA(4); W_D(0xFF); W_D(0x98); W_D(0x81); W_D(0x00);

GP_COMMAD_PA(2);

W_D(0x11);W_D(0x00); // Sleep Out

delay_ms(120) ;

W_D(0x29); W_D(0x00); // Display On

delay_ms(200) ;

&dsi0 {

status = "okay";

//rockchip,lane-rate = <1000>;

panel@0 {

compatible = "aoly,sl008pa21y1285-b00", "simple-panel-dsi";

reg = <0>;

backlight = <&backlight>;

//power-supply=<&vcc_3v3>;

enable-gpios = <&gpio0 RK_PC7 GPIO_ACTIVE_HIGH>;

reset-gpios = <&gpio0 RK_PA6 GPIO_ACTIVE_LOW>;

pinctrl-names = "default";

pinctrl-0 = <&lcd_enable_gpio>, <&lcd_rst_gpio>;

prepare-delay-ms = <120>;

reset-delay-ms = <120>;

init-delay-ms = <120>;

stbyb-delay-ms = <120>;

enable-delay-ms = <120>;

disable-delay-ms = <120>;

unprepare-delay-ms = <120>;

width-mm = <229>;

height-mm = <143>;

dsi,flags = <(MIPI_DSI_MODE_VIDEO | MIPI_DSI_MODE_VIDEO_BURST |

MIPI_DSI_MODE_LPM | MIPI_DSI_MODE_EOT_PACKET)>;

dsi,format = ;

dsi,lanes = <4>;

panel-init-sequence = [

39 00 04 FF 98 81 03

15 00 02 01 00

15 00 02 02 00

15 00 02 03 5d

15 00 02 04 17

15 00 02 05 00

15 00 02 06 0E

15 00 02 07 00

15 00 02 08 00

15 00 02 09 21

15 00 02 0a 21

15 00 02 0b 00

15 00 02 0c 06

15 00 02 0d 06

15 00 02 0e 00

15 00 02 0f 22

15 00 02 10 22

15 00 02 11 00

15 00 02 12 00

15 00 02 13 05

15 00 02 14 00

15 00 02 15 00

15 00 02 16 00

15 00 02 17 00

15 00 02 18 00

15 00 02 19 00

15 00 02 1a 00

15 00 02 1b 00

15 00 02 1c 00

15 00 02 1d 00

15 00 02 1e 40

15 00 02 20 0E

15 00 02 21 09

15 00 02 22 0F

15 00 02 23 00

15 00 02 24 8A

15 00 02 25 8A

15 00 02 26 00

15 00 02 27 00

15 00 02 28 77

15 00 02 29 77

15 00 02 2a 00

15 00 02 2b 00

15 00 02 2c 02

15 00 02 2d 02

15 00 02 2e 07

15 00 02 2f 07

15 00 02 30 00

15 00 02 31 00

15 00 02 32 22

15 00 02 33 00

15 00 02 34 00

15 00 02 35 0A

15 00 02 36 00

15 00 02 37 08

15 00 02 38 3C

15 00 02 39 00

15 00 02 3a 00

15 00 02 3b 00

15 00 02 3c 00

15 00 02 3d 00

15 00 02 3e 00

15 00 02 3f 00

15 00 02 40 00

15 00 02 41 00

15 00 02 42 00

15 00 02 43 08

15 00 02 44 00

15 00 02 50 01

15 00 02 51 23

15 00 02 52 45

15 00 02 53 67

15 00 02 54 89

15 00 02 55 ab

15 00 02 56 01

15 00 02 57 23

15 00 02 58 45

15 00 02 59 67

15 00 02 5a 89

15 00 02 5b ab

15 00 02 5c cd

15 00 02 5d ef

15 00 02 5e 00

15 00 02 5f 02

15 00 02 60 02

15 00 02 61 06

15 00 02 62 0F

15 00 02 63 0F

15 00 02 64 13

15 00 02 65 13

15 00 02 66 0E

15 00 02 67 0E

15 00 02 68 12

15 00 02 69 12

15 00 02 6a 0D

15 00 02 6b 0D

15 00 02 6c 11

15 00 02 6d 11

15 00 02 6e 0C

15 00 02 6f 0C

15 00 02 70 10

15 00 02 71 10

15 00 02 72 00

15 00 02 73 16

15 00 02 74 08

15 00 02 75 02

15 00 02 76 02

15 00 02 77 08

15 00 02 78 0F

15 00 02 79 0F

15 00 02 7a 13

15 00 02 7b 13

15 00 02 7c 0E

15 00 02 7d 0E

15 00 02 7e 12

15 00 02 7f 12

15 00 02 80 0D

15 00 02 81 0D

15 00 02 82 11

15 00 02 83 11

15 00 02 84 0C

15 00 02 85 0C

15 00 02 86 10

15 00 02 87 10

15 00 02 88 17

15 00 02 89 01

15 00 02 8A 06

39 00 04 FF 98 81 04

15 00 02 6E 2A

15 00 02 6F 37

15 00 02 3A A4

15 00 02 8D 25

15 00 02 87 BA

15 00 02 B2 D1

15 00 02 88 0B

15 00 02 38 01

15 00 02 39 00

15 00 02 B5 07

15 00 02 31 75

15 00 02 3B 98

39 00 04 FF 98 81 01

15 00 02 22 0A

15 00 02 31 0A

15 00 02 35 07

15 00 02 52 00

15 00 02 53 73

15 00 02 54 00

15 00 02 55 3D

15 00 02 50 D0

15 00 02 51 CB

15 00 02 60 14

15 00 02 62 01

15 00 02 63 01

15 00 02 A0 00

15 00 02 A1 18

15 00 02 A2 28

15 00 02 A3 17

15 00 02 A4 1C

15 00 02 A5 30

15 00 02 A6 24

15 00 02 A7 24

15 00 02 A8 85

15 00 02 A9 1C

15 00 02 AA 26

15 00 02 AB 66

15 00 02 AC 19

15 00 02 AD 18

15 00 02 AE 4F

15 00 02 AF 24

15 00 02 B0 2B

15 00 02 B1 4A

15 00 02 B2 59

15 00 02 B3 23

15 00 02 C0 00

15 00 02 C1 18

15 00 02 C2 28

15 00 02 C3 17

15 00 02 C4 1B

15 00 02 C5 2F

15 00 02 C6 22

15 00 02 C7 22

15 00 02 C8 87

15 00 02 C9 1C

15 00 02 CA 27

15 00 02 CB 66

15 00 02 CC 19

15 00 02 CD 1A

15 00 02 CE 4E

15 00 02 CF 24

15 00 02 D0 2A

15 00 02 D1 4C

15 00 02 D3 23

39 00 04 FF 98 81 00

15 78 02 11 00

15 78 02 29 00

];

panel-exit-sequence = [

05 dc 01 28

05 78 01 10

];

display-timings {

native-mode = <&timing0>;

timing0: timing0 {

clock-frequency = <60000000>;

hactive = <800>;

vactive = <1280>;

hsync-len = <1>;//19

hback-porch = <140>;//40

hfront-porch = <24>;//123

vsync-len = <1>;

vback-porch = <16>;

vfront-porch = <16>;

hsync-active = <0>;

vsync-active = <0>;

de-active = <0>;

pixelclk-active = <1>;

};

};

ports {

#address-cells = <1>;

#size-cells = <0>;

port@0 {

reg = <0>;

panel_in_dsi: endpoint {

remote-endpoint = <&dsi_out_panel>;

};

};

};

};

ports {

#address-cells = <1>;

#size-cells = <0>;

port@1 {

reg = <1>;

dsi_out_panel: endpoint {

remote-endpoint = <&panel_in_dsi>;

};

};

};

};

&dsi0_in_vp0 {

status = "disabled";

};

&dsi0_in_vp1 {

status = "okay";

}; 十二、参考文章

[RK3288][Android7.1] 调试笔记 --- 点MIPI屏初始化命令详解 - 灰信网(软件开发博客聚合)

RK PX30_android8.1的mipi屏调试_要不要买菜!的博客-CSDN博客