Vivado时序分析

文章目录

- 时序分析的基本方法

-

- 策略

- 延时计算方法

- 时序路径分析方法

-

- 触发器到触发器

-

- setup

- hold

- 输入端到触发器

-

- setup

- hold

- 触发器到输出端

-

- setup

- hold

- 输入到输出端

-

- step

- hold

- 分析模式

-

- 单一分析

- 最坏最好分析

- OCV

- 例子1:vivado约束

-

- sa->sb_reg建立时间

-

- Data Path

- Clock Path

- sa->sb_reg保持时间

-

- Data Path

- Clock Path

- sb_reg->sb建立时间

-

- Data Path

- Clock Path

- sb_reg->保持时间

-

- Data Path

- Clock Path

- 例子2:vivado约束

-

- sb_reg->sc_reg建立时间

-

- Data Path

- Clock Path

- sb_reg->sc_reg保持时间

-

- Data Path

- Clock Path

时序分析的基本方法

策略

- 基于路径的分析策略,在时序图中找到从起点和终点的所有路径并进行计算。

- 基于模块的分析策略,在时序图中中只侧重分析该路径下延迟最严重的节点进行计算

延时计算方法

- 组合逻辑

- 任意时刻的输出只取决于输入,与电路的原来状态无关,但是实际在电路中延时计算需要指导输入上拉和下拉的延时。

- 时序逻辑

- 任意时刻的输出取决于输入和原来的电路状态,但是时序逻辑仅在时钟有效沿工作,分别需要计算数据和时钟的路径延时

时序路径分析方法

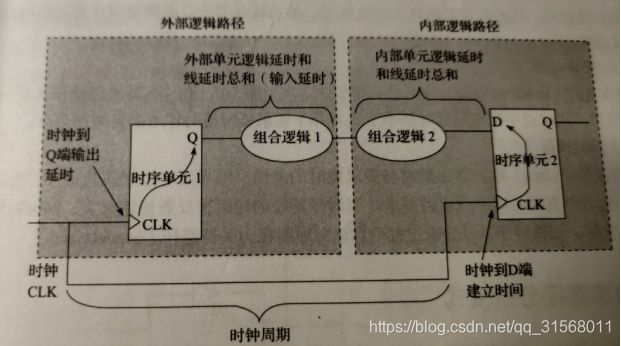

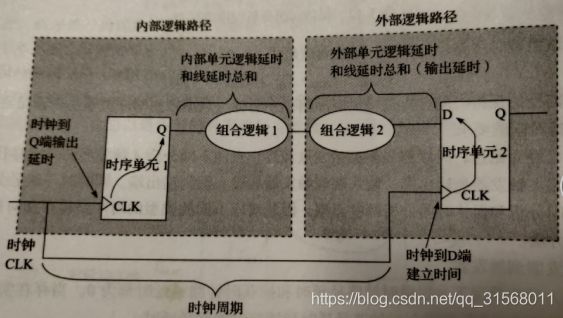

触发器到触发器

setup

c l k l a u n c h + F F 1 C L K − > Q + L o g i c ⩽ c l k c a p t u r e + c l k p e r i o d − F F 2 s e t u p clk_{launch}+FF1_{CLK->Q}+Logic \leqslant\\ clk_{capture}+clk_{period}-FF2_{setup} clklaunch+FF1CLK−>Q+Logic⩽clkcapture+clkperiod−FF2setup

hold

c l k l a u n c h + F F 1 C L K − > Q + L o g i c ⩾ c l k c a p t u r e + F F 2 h o l d clk_{launch}+FF1_{CLK->Q}+Logic \geqslant\\ clk_{capture}+FF2_{hold} clklaunch+FF1CLK−>Q+Logic⩾clkcapture+FF2hold

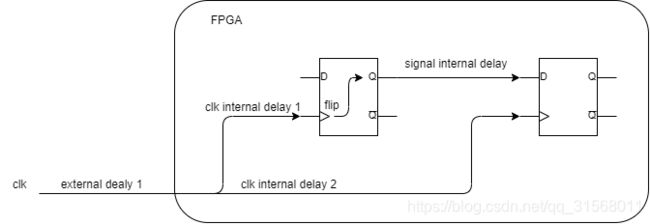

输入端到触发器

输入端到触发器的模型类似于触发器到触发器的模型,只需要将外部模型当作FF1就可以了,该路径的发射时延通过设置虚拟时钟来实现。

setup

v i r t u a l c l k l a u n c h + F F 1 C L K − > Q + L o g i c 1 + L o g i c 2 ⩽ c l k c a p t u r e + c l k p e r i o d − F F 2 s e t u p virtualclk_{launch}+FF1_{CLK->Q}+Logic1+Logic2 \leqslant\\ clk_{capture}+clk_{period}-FF2_{setup}\\ virtualclklaunch+FF1CLK−>Q+Logic1+Logic2⩽clkcapture+clkperiod−FF2setup

hold

v i r t u a l c l k l a u n c h + I n p u t d e a l a y + L o g i c 2 ⩾ c l k c a p t u r e + F F 2 h o l d virtualclk_{launch}+Input_{dealay}+Logic2 \geqslant\\ clk_{capture}+FF2_{hold}\\ virtualclklaunch+Inputdealay+Logic2⩾clkcapture+FF2hold

触发器到输出端

触发器到输出端模型同样类似于触发器到触发器的模型,只需要将外部模型当作FF2就可以了,该捕获的发射时延也通过设置虚拟时钟来实现

setup

c l k l a u n c h + F F 1 C L K − > Q + L o g i c 1 + L o g i c 2 ⩽ v i r t u a l c l k c a p t u r e + c l k p e r i o d − F F 2 s e t u p clk_{launch}+FF1_{CLK->Q}+Logic1+Logic2 \leqslant\\ virtualclk_{capture}+clk_{period}-FF2_{setup} clklaunch+FF1CLK−>Q+Logic1+Logic2⩽virtualclkcapture+clkperiod−FF2setup

hold

c l k l a u n c h + F F 1 C L K − > Q + L o g i c 1 + L o g i c 2 ⩾ v i r t u a l c l k c a p t u r e + F F 2 h o l d clk_{launch}+FF1_{CLK->Q}+Logic1+Logic2 \geqslant\\ virtualclk_{capture}+FF2_{hold} clklaunch+FF1CLK−>Q+Logic1+Logic2⩾virtualclkcapture+FF2hold

输入到输出端

step

L o g i c ⩽ v i r t u a l p e r i o d − I n p u t − O u t p u t Logic\leqslant virtual_{period} - Input - Output Logic⩽virtualperiod−Input−Output

hold

L o g i c ⩾ F F h o l d − I n p u t − O u t p u t Logic\geqslant FF_{hold} - Input - Output Logic⩾FFhold−Input−Output

分析模式

- 最快路径:信号传输延时计算调用最快工艺参数的路径

- 最慢路径:信号传输延时计算调用最慢工艺参数的路径

单一分析

- 最好的:较小的工艺偏差、较低的工作温度、较高的工作电压

- 最坏的:较大的工艺偏差、较高的工作温度、较低工作电压

- 典型位于两者之间

单一静态时序分析将指定其中一种工作条件下检查建立时间和保持时间

最坏最好分析

将在最好和最坏下进行分析和单一分析的计算方式一样,不同在于所使用的延时时序库的参数不同,计算建立用最大的延时库,计算保持用最小延时库

OCV

和前面的计算方法一样,不同在于计算最快和最慢路径有差别,最慢路径下调用最大延时,最快路径下调用最短延时。快慢的路径得出依赖于逻辑深度和逻辑单元的延时

例子1:vivado约束

以下面的例子介绍不同的约束手段

module time_practice(

input clk,

input sa,

output reg sb

);

always @(posedge clk)begin

if(sa)

sb <= 1'b1;

else

sb <= 1'b0;

end

endmodule

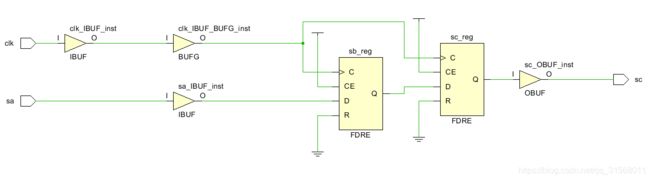

芯片时xc7a35t实际上芯片在这里不重要

create_clock -period 20.000 -name sys_clk -waveform {0.000 10.000} [get_ports clk]

set_property PACKAGE_PIN R2 [get_ports sa]

set_property IOSTANDARD LVCMOS33 [get_ports sa]

set_property PACKAGE_PIN R3 [get_ports sb]

set_property IOSTANDARD LVCMOS33 [get_ports sb]

set_input_delay -clock sys_clk -max 1.0 [get_ports sa]

set_input_delay -clock sys_clk -min 0.5 [get_ports sa]

set_output_delay -clock sys_clk -max 1.0 [get_ports sb]

set_output_delay -clock sys_clk -min 0.5 [get_ports sb]

综合后的图,vivado自动给我们添加IBUF BUFG 和OBUF

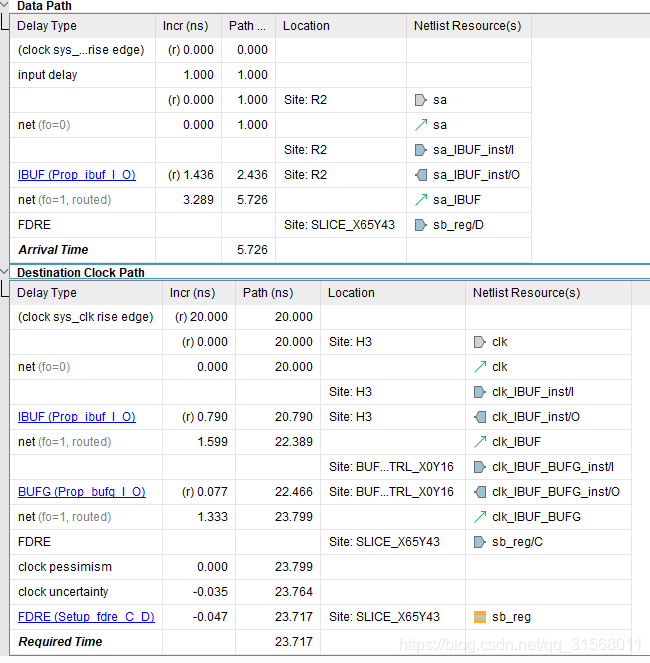

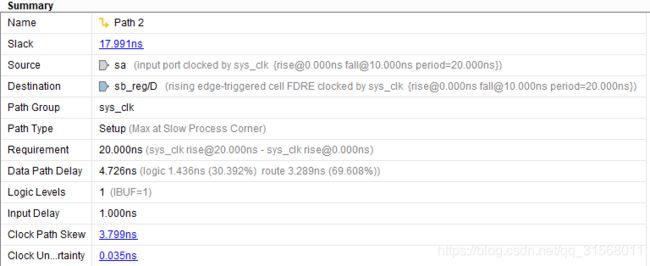

sa->sb_reg建立时间

vivado分析信号sa到触发器的D的建立时间路径如下:

实际时序分析的模型是从输入的到触发器,其中建立公式

c l k l a u c h = c l k e x t e r n a l _ 1 + e x 1 d e l a y c l k c a p t u r e = c l k e x t e r n a l _ 2 + c l k i n t e r n a l _ d e l a y c l k l a u c h + e x 2 d e l a y + e x 3 d e l a y + e x 4 d e l a y + s i g n a l i n t e r n a l _ d e l a y ⩽ c l k c a p t u r e + C L K p e r i o d − D s e t u p clk_{lauch} = clk_{external\_1}+ex1_{delay}\\ clk_{capture} = clk_{external\_2}+clk_{internal\_delay}\\ clk_{lauch}+ex2_{delay}+ex3_{delay}+ex4_{delay}+signal_{internal\_delay}\leqslant clk_{capture}+CLK_{period}-D_{setup} clklauch=clkexternal_1+ex1delayclkcapture=clkexternal_2+clkinternal_delayclklauch+ex2delay+ex3delay+ex4delay+signalinternal_delay⩽clkcapture+CLKperiod−Dsetup

在vivado中分析认为

e x 1 d e l a y + e x 2 d e l a y + e x 3 d e l a y + + e x 4 d e l a y = i n p u t _ d e a l y c l k e x t e r n a l _ 1 = c l k e x t e r n a l _ 2 ex1_{delay}+ex2_{delay}+ex3_{delay}++ex4_{delay} = input\_dealy\\ clk_{external\_1} =clk_{external\_2} ex1delay+ex2delay+ex3delay++ex4delay=input_dealyclkexternal_1=clkexternal_2

化简后

i n p u t _ d e a l y + s i g n a l i n t e r n a l _ d e l a y ⩽ c l k i n t e r n a l _ d e l a y + C L K p e r i o d − D s e t u p input\_dealy+signal_{internal\_delay}\leqslant clk_{internal\_delay}+CLK_{period}-D_{setup} input_dealy+signalinternal_delay⩽clkinternal_delay+CLKperiod−Dsetup

vivado从极端的条件下考虑,总是将等式左边的等式的变化量取极大值,右边的等式变化量取极小值。

Data Path

将sa信号的套入上面的式子

i n p u t _ d e a l y = 1 s i g n a l i n t e r n a l _ d e l a y = 1.436 ( I B U F ) + 3.289 ( n e t ) i n p u t _ d e a l y + s i g n a l i n t e r n a l _ d e l a y = 5.726 \begin{aligned} input\_dealy &= 1\\ signal_{internal\_delay} &=1.436(IBUF)+3.289(net)\\ input\_dealy+signal_{internal\_delay}&=5.726 \end{aligned} input_dealysignalinternal_delayinput_dealy+signalinternal_delay=1=1.436(IBUF)+3.289(net)=5.726

i n p u t _ d e a l y input\_dealy input_dealy 在这里是1,因为有约束sa信号最大的输入延时是1,若以最大的延时计算都能满足等式,自然其他时候也能够满足条件。

Clock Path

c l k i n t e r n a l _ d e l a y = 0.79 ( I B U F ) + 1.599 ( n e t ) + 0.077 ( B U F G ) + 1.333 ( n e t ) C L K p e r i o d = 20 D s e t u p = 0.047 c l k u n c e r t a i n t y = 0.035 c l k i n t e r n a l _ d e l a y + C L K p e r i o d − D s e t u p − c l k u n c e r t a i n t y = 23.717 \begin{aligned} clk_{internal\_delay}&=0.79(IBUF)+1.599(net)+0.077(BUFG)+1.333(net)\\ CLK_{period}& = 20\\ D_{setup} &=0.047\\ clk_{uncertainty} &=0.035\\ clk_{internal\_delay}+CLK_{period}-D_{setup}-clk_{uncertainty} &=23.717 \end{aligned} clkinternal_delayCLKperiodDsetupclkuncertaintyclkinternal_delay+CLKperiod−Dsetup−clkuncertainty=0.79(IBUF)+1.599(net)+0.077(BUFG)+1.333(net)=20=0.047=0.035=23.717

在vivado分析种还有clock pessimism (时序悲观,存在于有共同路径上,没有所以0)和 clock uncertainty(时序不确定性,在极端条件要影响这个等式不满足只能把它往左边的等式加,因为在将它往左边等式加的过程中如果依然满足等式条件,那么没有它存在自然也满足)。

s l a c k = C l o c k P a t h − D a t a P a h = 17.991 slack = Clock Path - DataPah = 17.991 slack=ClockPath−DataPah=17.991

可以看到分析建立时间的路径采用最慢路径的最大时延工艺参数。

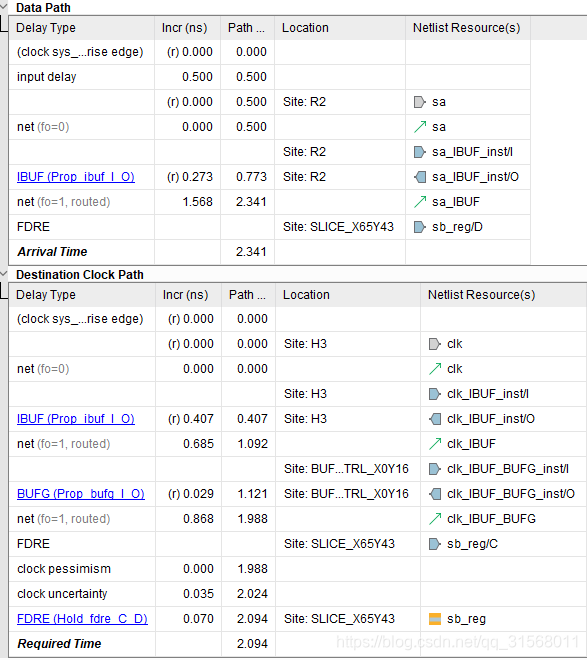

sa->sb_reg保持时间

其中保持时间公式

c l k l a u c h = c l k e x t e r n a l _ 1 + e x 1 d e l a y c l k c a p t u r e = c l k e x t e r n a l _ 2 + c l k i n t e r n a l _ d e l a y c l k l a u c h + e x 2 d e l a y + e x 3 d e l a y + e x 4 d e l a y + s i g n a l i n t e r n a l _ d e l a y ⩾ c l k c a p t u r e + D h o l d clk_{lauch} = clk_{external\_1}+ex1_{delay}\\ clk_{capture} = clk_{external\_2}+clk_{internal\_delay}\\ clk_{lauch}+ex2_{delay}+ex3_{delay}+ex4_{delay}+signal_{internal\_delay}\geqslant clk_{capture}+D_{hold} clklauch=clkexternal_1+ex1delayclkcapture=clkexternal_2+clkinternal_delayclklauch+ex2delay+ex3delay+ex4delay+signalinternal_delay⩾clkcapture+Dhold

化简

i n p u t _ d e a l y + s i g n a l i n t e r n a l _ d e l a y ⩾ c l k i n t e r n a l _ d e l a y + D h o l d input\_dealy+signal_{internal\_delay}\geqslant clk_{internal\_delay}+D_{hold} input_dealy+signalinternal_delay⩾clkinternal_delay+Dhold

vivado从极端的条件下考虑,总是将等式左边的等式的变化量取极小值,右边的等式变化量取极大值。

Data Path

i n p u t _ d e a l y = 0.5 s i g n a l i n t e r n a l _ d e l a y = 0.273 ( I B U F ) + 1.568 ( n e t ) i n p u t _ d e a l y + s i g n a l i n t e r n a l _ d e l a y = 2.341 \begin{aligned} input\_dealy &= 0.5\\ signal_{internal\_delay} &=0.273(IBUF)+1.568(net)\\ input\_dealy+signal_{internal\_delay}&=2.341 \end{aligned} input_dealysignalinternal_delayinput_dealy+signalinternal_delay=0.5=0.273(IBUF)+1.568(net)=2.341

i n p u t _ d e a l y input\_dealy input_dealy 在这里是0.5,因为有约束sa信号最小的输入延时是0.5,若以最小的延时计算都能满足等式,自然其他时候也能够满足条件。

Clock Path

c l k i n t e r n a l = 0.407 ( I B U F ) + 0.685 ( n e t ) + 0.029 ( B U F G ) + 0.868 ( n e t ) D h o l d = 0.070 c l k u n c e r t a i n t y = 0.035 c l k i n t e r n a l + D h o l d + c l k u n c e r t a i n t y = 2.094 \begin{aligned} clk_{internal}&=0.407(IBUF)+0.685(net)+0.029(BUFG)+0.868(net)\\ D_{hold} &=0.070\\ clk_{uncertainty} &=0.035\\ clk_{internal}+D_{hold}+clk_{uncertainty} &=2.094 \end{aligned} clkinternalDholdclkuncertaintyclkinternal+Dhold+clkuncertainty=0.407(IBUF)+0.685(net)+0.029(BUFG)+0.868(net)=0.070=0.035=2.094

同样在vivado分析种还有clock pessimism (时序悲观,存在于有共同路径上,没有所以0)和 clock uncertainty(时序不确定性,时序不确定性,在极端条件要影响这个等式不满足只能把它往右边的等式加,因为在将它往右边等式加的过程中如果依然满足等式条件,那么没有它存在自然也满足)。

s l a c k = D a t a P a h − C l o c k P a t h = 0.248 slack = DataPah - Clock Path = 0.248 slack=DataPah−ClockPath=0.248

可以看到分析保持的路径采用最快路径的最小时延工艺参数。

这也就解释了为什么在 c l k i n t e r n a l clk_{internal} clkinternal一样的路径下得到的延时参数不一致。

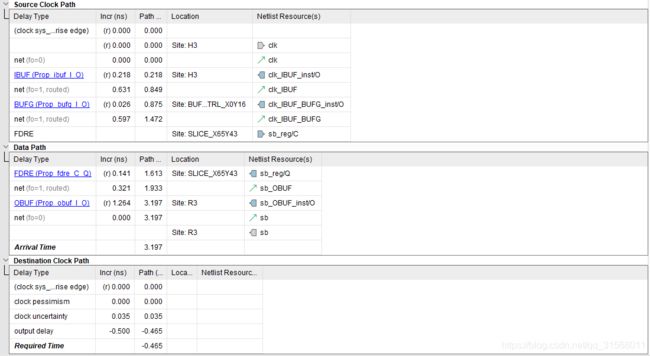

sb_reg->sb建立时间

实际时序分析的模型是从触发器到输出端,其中建立公式

c l k l a u c h = c l k e x t e r n a l _ 1 + c l k i n t e r n a l _ d e l a y c l k c a p t u r e = c l k e x t e r n a l _ 2 + e x 3 d e l a y c l k l a u c h + f l i p d e l a y + s i g n a l i n t e r n a l _ d e l a y + e x 1 d e l a y + e x 2 d e l a y ⩽ c l k c a p t u r e + C L K p e r i o d − D s e t u p clk_{lauch} = clk_{external\_1}+clk_{internal\_delay}\\ clk_{capture} = clk_{external\_2}+ex3_{delay}\\ clk_{lauch}+flip_{delay}+signal_{internal\_delay}+ex1_{delay}+ex2_{delay}\leqslant clk_{capture}+CLK_{period}-D_{setup} clklauch=clkexternal_1+clkinternal_delayclkcapture=clkexternal_2+ex3delayclklauch+flipdelay+signalinternal_delay+ex1delay+ex2delay⩽clkcapture+CLKperiod−Dsetup

在vivado中分析认为

e x 1 d e l a y + e x 2 d e l a y + D s e t u p − e x 3 d e l a y = o u t p u t _ d e a l y c l k e x t e r n a l _ 1 = c l k e x t e r n a l _ 2 ex1_{delay}+ex2_{delay}+D_{setup}-ex3_{delay}= output\_dealy\\ clk_{external\_1} =clk_{external\_2} ex1delay+ex2delay+Dsetup−ex3delay=output_dealyclkexternal_1=clkexternal_2

化简后

c l k i n t e r n a l _ d e l a y + f l i p d e l a y + + s i g n a l i n t e r n a l ⩽ C L K p e r i o d − o u t p u t d e l a y clk_{internal\_delay}+flip_{delay}++signal_{internal} \leqslant CLK_{period}-output_delay clkinternal_delay+flipdelay++signalinternal⩽CLKperiod−outputdelay

vivado从极端的条件下考虑,总是将等式左边的等式的变化量取极小值,右边的等式变化量取极大值。

Data Path

c l k i n t e r n a l _ d e l a y = 0.921 ( I B U F ) + 1.689 ( n e t ) + 0.081 ( B U F G ) + 1.443 ( n e t ) f l i p _ d e a l y = 0.379 ( F D R E ) s i g n a l i n t e r n a l _ d e l a y = 1.385 ( n e t ) + 3.309 ( O B U F ) c l k i n t e r n a l _ d e l a y + f l i p _ d e a l y + s i g n a l i n t e r n a l _ d e l a y = 9.206 \begin{aligned} clk_{internal\_delay} &=0.921(IBUF)+1.689(net)+0.081(BUFG)+1.443(net)\\ flip\_dealy&=0.379(FDRE)\\ signal_{internal\_delay}&=1.385(net)+3.309(OBUF)\\ clk_{internal\_delay}+flip\_dealy+signal_{internal\_delay} &=9.206 \end{aligned} clkinternal_delayflip_dealysignalinternal_delayclkinternal_delay+flip_dealy+signalinternal_delay=0.921(IBUF)+1.689(net)+0.081(BUFG)+1.443(net)=0.379(FDRE)=1.385(net)+3.309(OBUF)=9.206

Clock Path

C L K p e r i o d = 20 c l k u n c e r t a i n t y = 0.035 o u t p u t d e l a y = 1 C L K p e r i o d − o u t p u t d e l a y − c l k u n c e r t a i n t y = 18.965 \begin{aligned} CLK_{period}&=20\\ clk_{uncertainty} &=0.035\\ output_{delay} &=1\\ CLK_{period}-output_{delay}-clk_{uncertainty} &=18.965 \end{aligned} CLKperiodclkuncertaintyoutputdelayCLKperiod−outputdelay−clkuncertainty=20=0.035=1=18.965

o u t p u t d e l a y output_{delay} outputdelay在这里是1,因为有约束sb信号最大的输出延时是1,若以最大的输出延时计算都能满足等式,自然其他时候也能够满足条件。

在vivado分析种还有clock pessimism (时序悲观,存在于有共同路径上,没有所以0)和 clock uncertainty(时序不确定性,在极端条件要影响这个等式不满足只能把它往左边的等式加,因为在将它往左边等式加的过程中如果依然满足等式条件,那么没有它存在自然也满足)。

可以看到分析建立时间的路径采用最慢路径的最大时延工艺参数。

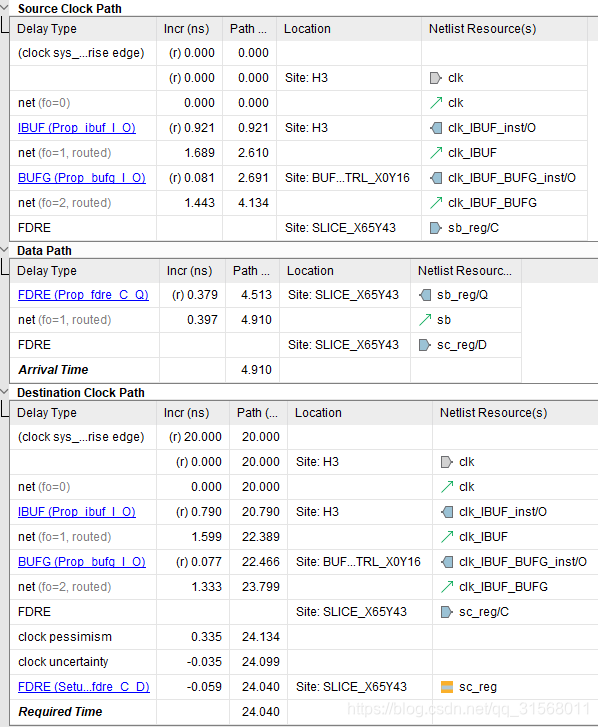

sb_reg->保持时间

其中保持时间公式

c l k l a u c h = c l k e x t e r n a l _ 1 + c l k i n t e r n a l _ d e l a y c l k c a p t u r e = c l k e x t e r n a l _ 2 + e x 3 d e l a y c l k l a u c h + f l i p d e l a y + s i g n a l i n t e r n a l _ d e l a y + e x 1 d e l a y + e x 2 d e l a y ⩾ c l k c a p t u r e + D h o l d clk_{lauch} = clk_{external\_1}+clk_{internal\_delay}\\ clk_{capture} = clk_{external\_2}+ex3_{delay}\\ clk_{lauch}+flip_{delay}+signal_{internal\_delay}+ex1_{delay}+ex2_{delay}\geqslant clk_{capture}+D_{hold} clklauch=clkexternal_1+clkinternal_delayclkcapture=clkexternal_2+ex3delayclklauch+flipdelay+signalinternal_delay+ex1delay+ex2delay⩾clkcapture+Dhold

在vivado中分析认为

e x 1 d e l a y + e x 2 d e l a y − D h o l d − e x 3 d e l a y = o u t p u t _ d e a l y c l k e x t e r n a l _ 1 = c l k e x t e r n a l _ 2 ex1_{delay}+ex2_{delay}-D_{hold}-ex3_{delay}= output\_dealy\\ clk_{external\_1} =clk_{external\_2} ex1delay+ex2delay−Dhold−ex3delay=output_dealyclkexternal_1=clkexternal_2

化简后

c l k i n t e r n a l _ d e l a y + f l i p d e l a y + + s i g n a l i n t e r n a l ⩾ − o u t p u t d e l a y clk_{internal\_delay}+flip_{delay}++signal_{internal} \geqslant -output_{delay} clkinternal_delay+flipdelay++signalinternal⩾−outputdelay

vivado从极端的条件下考虑,总是将等式左边的等式的变化量取极小值,右边的等式变化量取极大值。

Data Path

c l k i n t e r n a l _ d e l a y = 0.218 ( I B U F ) + 0.631 ( n e t ) + 0.026 ( B U F G ) + 0.597 ( n e t ) f l i p d e l a y = 0.141 ( F D R E ) s i g n a l i n t e r n a l _ d e l a y = 0.321 ( n e t ) + 1.264 ( O B U F ) c l k i n t e r n a l _ d e l a y + f l i p d e l a y + s i g n a l i n t e r n a l _ d e l a y = 3.197 \begin{aligned} clk_{internal\_delay} &= 0.218(IBUF)+0.631(net)+0.026(BUFG)+0.597(net)\\ flip_{delay} &=0.141(FDRE)\\ signal_{internal\_delay} &=0.321(net)+1.264(OBUF)\\ clk_{internal\_delay}+flip_{delay}+signal_{internal\_delay} &=3.197\\ \end{aligned} clkinternal_delayflipdelaysignalinternal_delayclkinternal_delay+flipdelay+signalinternal_delay=0.218(IBUF)+0.631(net)+0.026(BUFG)+0.597(net)=0.141(FDRE)=0.321(net)+1.264(OBUF)=3.197

Clock Path

c l k u n c e r t a i n t y = 0.035 o u t p u t d e l a y = 0.5 c l k u n c e r t a i n t y − o u t p u t d e l a y = − 0.465 \begin{aligned} clk_{uncertainty} &=0.035\\ output_{delay} &=0.5\\ clk_{uncertainty}-output_{delay} &=-0.465 \end{aligned} clkuncertaintyoutputdelayclkuncertainty−outputdelay=0.035=0.5=−0.465

o u t p u t d e l a y output_{delay} outputdelay在这里是0.5,因为有约束sb信号最小的输出延时是0.5,若以最小的输出延时计算都能满足等式,自然其他时候也能够满足条件。

同样在vivado分析中还有clock pessimism (时序悲观,存在于有共同路径上,没有所以0)和 clock uncertainty(时序不确定性,在极端条件要影响这个等式不满足只能把它往右边的等式加,因为在将它往右边等式加的过程中如果依然满足等式条件,那么没有它存在自然也满足)。

可以看到分析保持时间的路径采用最快路径的最小时延工艺参数。

因此按照分析原则,vivado默认的静态时序分析模式是OCV

例子2:vivado约束

module time_practice(

input clk,

input sa,

output reg sc

);

reg sb;

always @(posedge clk)begin

if(sa)

sb <= 1'b1;

else

sb <= 1'b0;

end

always @(posedge clk)begin

sc<=sb;

end

endmodule

芯片时xc7a35t实际上芯片在这里不重要

create_clock -period 20.000 -name sys_clk -waveform {0.000 10.000} [get_ports clk]

set_property PACKAGE_PIN R2 [get_ports sa]

set_property IOSTANDARD LVCMOS33 [get_ports sa]

set_property PACKAGE_PIN R3 [get_ports sc]

set_property IOSTANDARD LVCMOS33 [get_ports sc]

set_input_delay -clock sys_clk -max 1.0 [get_ports sa]

set_input_delay -clock sys_clk -min 0.5 [get_ports sa]

set_output_delay -clock sys_clk -max 1.0 [get_ports sc]

set_output_delay -clock sys_clk -min 0.5 [get_ports sc]

综合后的图,vivado自动给我们添加IBUF BUFG 和OBUF,不过这里分析sb到sc的信号

sb_reg->sc_reg建立时间

其中建立公式

c l k l a u c h = c l k e x t e r n a l _ 1 + c l k i n t e r n a l _ d e l a y _ 1 c l k c a p t u r e = c l k e x t e r n a l _ 1 + c l k i n t e r n a l _ d e l a y _ 2 c l k l a u c h + f l i g d e l a y + s i g n a l i n t e r n a l _ d e l a y ⩽ c l k c a p t u r e + C L K p e r i o d − D s e t u p clk_{lauch} = clk_{external\_1}+clk_{internal\_delay\_1}\\ clk_{capture} = clk_{external\_1}+clk_{internal\_delay\_2}\\ clk_{lauch}+flig_{delay}+signal_{internal\_delay}\leqslant clk_{capture}+CLK_{period}-D_{setup} clklauch=clkexternal_1+clkinternal_delay_1clkcapture=clkexternal_1+clkinternal_delay_2clklauch+fligdelay+signalinternal_delay⩽clkcapture+CLKperiod−Dsetup

化简

c l k i n t e r n a l _ d e l a y _ 1 + f l i p d e l a y + s i g n a l i n t e r n a l _ d e l a y ⩽ c l k i n t e r n a l _ d e l a y _ 2 + C L K p e r i o d − D s e t u p clk_{internal\_delay\_1}+flip_{delay}+signal_{internal\_delay}\leqslant clk_{internal\_delay\_2}+CLK_{period}-D_{setup} clkinternal_delay_1+flipdelay+signalinternal_delay⩽clkinternal_delay_2+CLKperiod−Dsetup

vivado从极端的条件下考虑,总是将等式左边的等式的变化量取极大值,右边的等式变化量取极小值。

Data Path

c l k i n t e r n a l _ d e l a y _ 1 = 0.921 ( I B U F ) + 1.689 ( n e t ) + 0.081 ( B U F G ) + ( 1.443 ) n e t f l i p d e l a y = 0.379 ( F D R E ) s i g n a l i n t e r n a l _ d e l a y = 0.397 ( n e t ) c l k i n t e r n a l _ d e l a y _ 1 + f l i p d e l a y + s i g n a l i n t e r n a l _ d e l a y = 4.910 \begin{aligned} clk_{internal\_delay\_1} & =0.921(IBUF)+1.689(net)+0.081(BUFG)+(1.443)net\\ flip_{delay} & =0.379(FDRE)\\ signal_{internal\_delay} & =0.397(net)\\ clk_{internal\_delay\_1}+flip_{delay}+signal_{internal\_delay} & =4.910 \end{aligned} clkinternal_delay_1flipdelaysignalinternal_delayclkinternal_delay_1+flipdelay+signalinternal_delay=0.921(IBUF)+1.689(net)+0.081(BUFG)+(1.443)net=0.379(FDRE)=0.397(net)=4.910

Clock Path

c l k i n t e r n a l _ d e l a y _ 2 = 0.79 ( I B U F ) + 1.599 ( n e t ) + 0.077 ( B U F G ) + ( 1.333 ) n e t C L K p e r i o d = 20 D s e t u p = 0.059 ( n e t ) c l o c k p e s s i m i s m = 0.335 c l o c k u n c e r t a i n t y = 0.035 c l k i n t e r n a l _ d e l a y _ 2 + C L K p e r i o d − D s e t u p + c l o c k p e s s i m i s m − c l o c k u n c e r t a i n t y = 24.040 \begin{aligned} clk_{internal\_delay\_2} & =0.79(IBUF)+1.599(net)+0.077(BUFG)+(1.333)net\\ CLK_{period} & =20\\ D_{setup} & =0.059(net)\\ clock_{pessimism}&=0.335\\ clock_{uncertainty}&=0.035\\ clk_{internal\_delay\_2}+CLK_{period}-D_{setup}+clock_{pessimism}-clock_{uncertainty} & =24.040 \end{aligned} clkinternal_delay_2CLKperiodDsetupclockpessimismclockuncertaintyclkinternal_delay_2+CLKperiod−Dsetup+clockpessimism−clockuncertainty=0.79(IBUF)+1.599(net)+0.077(BUFG)+(1.333)net=20=0.059(net)=0.335=0.035=24.040

-

clock pessimism

- 时序悲观,可以看到到sb_reg和sc_reg的时钟路径上其实是同一路径也就是说 c l k i n t e r n a l _ d e l a y _ 1 clk_{internal\_delay\_1} clkinternal_delay_1和 c l k i n t e r n a l _ d e l a y _ 2 clk_{internal\_delay\_2} clkinternal_delay_2在综合图上路径是一致的,因此实际上延迟是一致的,不应该为了极端方式在路径上 c l k i n t e r n a l _ d e l a y _ 1 clk_{internal\_delay\_1} clkinternal_delay_1使用最慢路径,在路径上 c l k i n t e r n a l _ d e l a y _ 2 clk_{internal\_delay\_2} clkinternal_delay_2使用最快路径。为了补偿他们的差值

c l o c k p e s s i m i s m = c l k i n t e r n a l _ d e l a y _ 1 − c l k i n t e r n a l _ d e l a y _ 2 = 0.335 clock_{pessimism}=clk_{internal\_delay\_1}-clk_{internal\_delay\_2}=0.335\\ clockpessimism=clkinternal_delay_1−clkinternal_delay_2=0.335

- clock uncertainty

- 时序不确定性,在极端条件要影响这个等式不满足只能把它往左边的等式加,因为在将它往左边等式加的过程中如果依然满足等式条件,那么没有它存在自然也满足。

s l a c k = C l o c k P a t h − D a t a P a t h = 19.130 slack = ClockPath-DataPath=19.130 slack=ClockPath−DataPath=19.130

分析建立时间使用了最慢路径的最大延时工艺参数

sb_reg->sc_reg保持时间

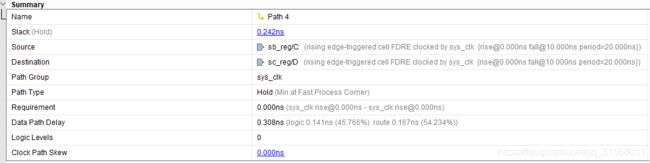

vivado分析信号sb到sc的D的保持时间路径如下:

其中保持公式

c l k l a u c h = c l k e x t e r n a l _ 1 + c l k i n t e r n a l _ d e l a y _ 1 c l k c a p t u r e = c l k e x t e r n a l _ 1 + c l k i n t e r n a l _ d e l a y _ 2 c l k l a u c h + f l i g d e l a y + s i g n a l i n t e r n a l _ d e l a y ⩾ c l k c a p t u r e + D h o l d clk_{lauch} = clk_{external\_1}+clk_{internal\_delay\_1}\\ clk_{capture} = clk_{external\_1}+clk_{internal\_delay\_2}\\ clk_{lauch}+flig_{delay}+signal_{internal\_delay}\geqslant clk_{capture}+D_{hold} clklauch=clkexternal_1+clkinternal_delay_1clkcapture=clkexternal_1+clkinternal_delay_2clklauch+fligdelay+signalinternal_delay⩾clkcapture+Dhold

化简

c l k i n t e r n a l _ d e l a y _ 1 + f l i p d e l a y + s i g n a l i n t e r n a l _ d e l a y ⩾ c l k i n t e r n a l _ d e l a y _ 2 + D h o l d clk_{internal\_delay\_1}+flip_{delay}+signal_{internal\_delay}\geqslant clk_{internal\_delay\_2}+D_{hold} clkinternal_delay_1+flipdelay+signalinternal_delay⩾clkinternal_delay_2+Dhold

Data Path

c l k i n t e r n a l _ d e l a y _ 1 = 0.218 ( I B U F ) + 0.631 ( n e t ) + 0.026 ( B U F G ) + ( 0.597 ) n e t f l i p d e l a y = 0.141 ( F D R E ) s i g n a l i n t e r n a l _ d e l a y = 0.167 ( n e t ) c l k i n t e r n a l _ d e l a y _ 1 + f l i p d e l a y + s i g n a l i n t e r n a l _ d e l a y = 1.780 \begin{aligned} clk_{internal\_delay\_1} & =0.218(IBUF)+0.631(net)+0.026(BUFG)+(0.597)net\\ flip_{delay} & =0.141(FDRE)\\ signal_{internal\_delay} & =0.167(net)\\ clk_{internal\_delay\_1}+flip_{delay}+signal_{internal\_delay} & =1.780 \end{aligned} clkinternal_delay_1flipdelaysignalinternal_delayclkinternal_delay_1+flipdelay+signalinternal_delay=0.218(IBUF)+0.631(net)+0.026(BUFG)+(0.597)net=0.141(FDRE)=0.167(net)=1.780

Clock Path

c l k i n t e r n a l _ d e l a y _ 2 = 0.407 ( I B U F ) + 0.685 ( n e t ) + 0.029 ( B U F G ) + ( 0.868 ) n e t D h o l d = 0.066 ( n e t ) c l o c k p e s s i m i s m = − 0.517 c l k i n t e r n a l _ d e l a y _ 2 + D h o l d + c l o c k p e s s i m i s m = 24.040 \begin{aligned} clk_{internal\_delay\_2} & =0.407(IBUF)+0.685(net)+0.029(BUFG)+(0.868)net\\ D_{hold} & =0.066(net)\\ clock_{pessimism}&=-0.517\\ clk_{internal\_delay\_2}+D_{hold}+clock_{pessimism} & =24.040 \end{aligned} clkinternal_delay_2Dholdclockpessimismclkinternal_delay_2+Dhold+clockpessimism=0.407(IBUF)+0.685(net)+0.029(BUFG)+(0.868)net=0.066(net)=−0.517=24.040

clock pessimism

- 时序悲观,可以看到到sb_reg和sc_reg的时钟路径上其实是同一路径也就是说 c l k i n t e r n a l _ d e l a y _ 1 clk_{internal\_delay\_1} clkinternal_delay_1和 c l k i n t e r n a l _ d e l a y _ 2 clk_{internal\_delay\_2} clkinternal_delay_2在综合图上路径是一致的,因此实际上延迟是一致的,不应该为了极端方式在路径上 c l k i n t e r n a l _ d e l a y _ 1 clk_{internal\_delay\_1} clkinternal_delay_1使用最快路径,在路径上 c l k i n t e r n a l _ d e l a y _ 2 clk_{internal\_delay\_2} clkinternal_delay_2使用最慢路径。为了补偿他们的差值

c l o c k p e s s i m i s m = c l k i n t e r n a l _ d e l a y _ 1 − c l k i n t e r n a l _ d e l a y _ 2 = − 0.517 clock_{pessimism}=clk_{internal\_delay\_1}-clk_{internal\_delay\_2}=-0.517\\ clockpessimism=clkinternal_delay_1−clkinternal_delay_2=−0.517

s l a c k = C l o c k P a t h − D a t a P a t h = 19.130 slack = ClockPath-DataPath=19.130 slack=ClockPath−DataPath=19.130

但是这里突然没有 c l o c k u n c e r t a i n t y clock_{uncertainty} clockuncertainty感觉有些奇怪。

c l k i n t e r n a l _ d e l a y _ 2 = 0.407 ( I B U F ) + 0.685 ( n e t ) + 0.029 ( B U F G ) + ( 0.868 ) n e t D h o l d = 0.066 ( n e t ) c l o c k p e s s i m i s m = − 0.517 c l k i n t e r n a l _ d e l a y _ 2 + D h o l d + c l o c k p e s s i m i s m = 24.040 \begin{aligned} clk_{internal\_delay\_2} & =0.407(IBUF)+0.685(net)+0.029(BUFG)+(0.868)net\\ D_{hold} & =0.066(net)\\ clock_{pessimism}&=-0.517\\ clk_{internal\_delay\_2}+D_{hold}+clock_{pessimism} & =24.040 \end{aligned} clkinternal_delay_2Dholdclockpessimismclkinternal_delay_2+Dhold+clockpessimism=0.407(IBUF)+0.685(net)+0.029(BUFG)+(0.868)net=0.066(net)=−0.517=24.040

clock pessimism

- 时序悲观,可以看到到sb_reg和sc_reg的时钟路径上其实是同一路径也就是说 c l k i n t e r n a l _ d e l a y _ 1 clk_{internal\_delay\_1} clkinternal_delay_1和 c l k i n t e r n a l _ d e l a y _ 2 clk_{internal\_delay\_2} clkinternal_delay_2在综合图上路径是一致的,因此实际上延迟是一致的,不应该为了极端方式在路径上 c l k i n t e r n a l _ d e l a y _ 1 clk_{internal\_delay\_1} clkinternal_delay_1使用最快路径,在路径上 c l k i n t e r n a l _ d e l a y _ 2 clk_{internal\_delay\_2} clkinternal_delay_2使用最慢路径。为了补偿他们的差值

c l o c k p e s s i m i s m = c l k i n t e r n a l _ d e l a y _ 1 − c l k i n t e r n a l _ d e l a y _ 2 = − 0.517 clock_{pessimism}=clk_{internal\_delay\_1}-clk_{internal\_delay\_2}=-0.517\\ clockpessimism=clkinternal_delay_1−clkinternal_delay_2=−0.517

s l a c k = C l o c k P a t h − D a t a P a t h = 19.130 slack = ClockPath-DataPath=19.130 slack=ClockPath−DataPath=19.130

但是这里突然没有 c l o c k u n c e r t a i n t y clock_{uncertainty} clockuncertainty感觉有些奇怪。

分析建立时间使用了最快路径的最小延时工艺参数。