s3c6410_时钟初始化

参考:

1)《USER'S MANUAL-S3C6410X》第三章 SYSTEM CONTROLLER

2)u-boot/board/samsumg/smdk6410/lowlevel_init.S

1. PLL与CLK的关系:

详细关系图见用户手册122页Figure 3-2 The block diagram of clock generator。

三种PLL:APLL,MPLL,EPLL

四种CLK:ACLK,HCLK,PCLK

1)APLL产生ACLK,,ACLK为CPU提供时钟;

2)同步模式下APLL产生HCLK/PCLK,异步模式下MPLL产生HCLK/PCLK,HCLK为AXI/AHB总线上的外设提供时钟,PCLK为APB总线上的外设提供时钟;

3)EPLL主要为音频相关的外设提供时钟;

2. 时钟初始化的步骤

假设我们的目标时钟大小为:

ACLK: 532M

HCLK: 133M

PCLK: 66.5M

1)设置同步/异步模式

寄存器:OTHERS

地址:0x7E00F900

方法:

同步模式:设置[7][6]位为11,等待[11:8]位变成1111;

异步模式:设置[7][6]位为00,等待[11:8]位变成0000;

2)设置各PLL的锁定时间

寄存器:

APLL_LOCK

MPLL_LOCK

EPLL_LOCK

地址:

0x7E00F000

0x7E00F004

0x7E00F008

方法:

将三种PLL的锁定时间均设成最大值0xffff。

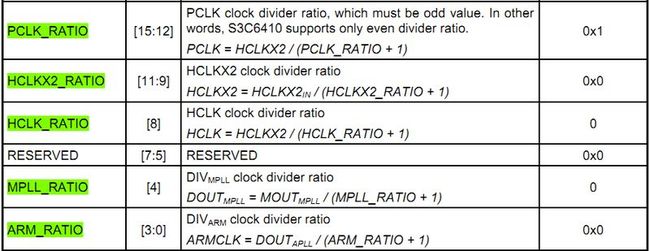

3)设置各CLK的分频系数

寄存器:

CLK_DIV0

地址:

0x7E00F020

方法:

各个CLK的输出频率,输入频率,分频系数的关系如下图:

为了得到预期的频率(532_133_66),各个RATIO取如下值:

#define PCLK_RATIO 3 //PCLK=266M/(3+1)=66.5M

#define HCLKX2_RATIO 1 //HCLKX2=532/(1+1)=266M

#define HCLK_RATIO 1 //HCLK=266/(1+1)=133M

#define MPLL_RATIO 1

#define ARM_RATIO 0 //ACLK=532M/(0+1)=532M

#define CLK_DIV0_VAL ((PCLK_RATIO<<12)|(HCLKX2_RATIO<<9)|(HCLK_RATIO<<8)|(MPLL_RATIO<<4)|(ARM_RATIO))

4)设置各PLL的输出频率

寄存器:

APLL_CON

MPLL_CON

EPLL_CON0

EPLL_CON1

地址:

0x7E00F00C

0x7E00F010

0x7E00F014

0x7E00F018

方法:

(1)APLL/MPLL

APLL_CON/MPLL_CON中有三个参数:MDIV,PDIV,SDIV共同决定APLL/MPLL的输出频率:

FOUT = MDIV * FIN / (PDIV * 2^SDIV)

FIN,FOUT,MDIV,PDIV,SDIV的常见组合如下:

这里我们要产生533M的APLL/MPLL,故MDIV,PDIV,SDIV的取值如下:

#define APLL_MDIV 266

#define APLL_PDIV 3

#define APLL_SDIV 1

#define APLL_CON_VAL ((1<<31)|(APLL_MDIV<<16)|(APLL_PDIV<<8)|(APLL_SDIV))

#define MPLL_MDIV 266

#define MPLL_PDIV 3

#define MPLL_SDIV 1

#define MPLL_CON_VAL ((1<<31)|(MPLL_MDIV<<16)|(MPLL_PDIV<<8)|(MPLL_SDIV))

(2)EPLL

EPLL_CON0和EPLL_CON1中四个参数:MDIV,PDIV,SDIV,KDIV共同决定EPLL的输出频率:

FOUT = (MDIV + KDIV / 2^16 ) * FIN / (PDIV * 2 ^SDIV)

FIN,FOUT,MDIV,PDIV,SDIV,KDIV的常见组合如下:

这里我们要产生96M的EPLL,故MDIV,PDIV,SDIV,KDIV的取值如下:

#define EPLL_MDIV 32

#define EPLL_PDIV 1

#define EPLL_SDIV 2

#define EPLL_KDIV 0

#define EPLL_CON0_VAL ((1<<31)|(EPLL_MDIV<<16)|(EPLL_PDIV<<8)|(EPLL_SDIV))

#define EPLL_CON1_VAL (EPLL_KDIV)

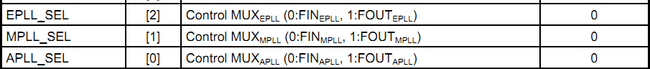

5)选择时钟源

寄存器:

CLK_SRC

地址:

0x7E00F01C

方法:

我们选择PLL的输出作为时钟源,设置CLK_SRC的低三位为111。

我们选择PLL的输出作为时钟源,设置CLK_SRC的低三位为111。

3. 时钟初始化的汇编代码实现

clock.S

/* ACLK: 532M HCLK: 133M PCLK: 66M */ #include "clock.h" .global clock_init clock_init: ldr r0, =ELFIN_CLOCK_POWER_BASE /*step1: set synchronous mode*/ ldr r1, [r0, #OTHERS_OFFSET] mov r2, #0x40 orr r1, r1, r2 str r1, [r0, #OTHERS_OFFSET] nop nop nop nop nop mov r2, #0x80 orr r1, r1, r2 str r1, [r0, #OTHERS_OFFSET] check_syncack: ldr r1, [r0, #OTHERS_OFFSET] mov r2, #0xf00 and r1, r1, r2 cmp r1, #0xf00 bne check_syncack /*step2: set pll lock time*/ mov r1, #0xff00 orr r1, r1, #0xff str r1, [r0, #APLL_LOCK_OFFSET] str r1, [r0, #MPLL_LOCK_OFFSET] str r1, [r0, #EPLL_LOCK_OFFSET] /*step3: set clk divider ratio*/ ldr r1, [r0, #CLK_DIV0_OFFSET] bic r1, r1, #0xff00 bic r1, r1, #0x00ff ldr r2, =CLK_DIV0_VAL orr r1, r1, r2 str r1, [r0, #CLK_DIV0_OFFSET] /*step4: set pll output frequency*/ ldr r1, =APLL_CON_VAL str r1, [r0, #APLL_CON_OFFSET] ldr r1, =MPLL_CON_VAL str r1, [r0, #MPLL_CON_OFFSET] ldr r1, =EPLL_CON0_VAL str r1, [r0, #EPLL_CON0_OFFSET] ldr r1, =EPLL_CON1_VAL str r1, [r0, #EPLL_CON1_OFFSET] /*step5: set clk src*/ ldr r1, [r0, #CLK_SRC_OFFSET] mov r2, #0x7 orr r1, r1, r2 str r1, [r0, #CLK_SRC_OFFSET] /*wait at least 200us to stablize all clock*/ mov r1, #0x10000

1: subs r1, r1, #1 bne 1b mov pc, lr

4. 实验验证

编写一个流水灯的裸机程序,对比进行时钟初始化和不进行时钟初始化两种情况下流水灯闪烁的快慢。

频率对比如下:

| APLL | MPLL | EPLL | ACLK | HCLKX2 | HCLK | PCLK | |

| 默认值(M) | 400 | 133 | 97.7 | 400 | 133 | 133 | 66.5 |

| 当前值(M) | 532 | 266 | 96 | 532 | 266 | 133 | 66.5 |

不进行时钟初始化时,CPU的默认频率是400M,

进行时钟初始化后,CPU的频率是532M,

故在时钟初始化的情况下,流水灯的闪烁速度要快一些。

实验代码这里不贴出,点击可下载。