- Spring基础知识——笔记整理(一)

豆萌萌 网课大咖

笔记整理springjava

Spring简介Spring是一个轻量级Java开发框架,由RodJohnson创建,目的是为了解决企业级应用开发的业务逻辑层和其他各层的耦合问题。它是一个JavaSE/JavaEE分层的full-stack(一站式)轻量级开源框架,为开发Java应用程序提供全面的基础架构支持。Spring负责基础架构,因此Java开发者可以专注于应用程序的开发。Spring的优点方便解耦,简化开发:Spring

- Github 2024-04-29 开源项目周报 Top15

老孙正经胡说

github开源Github趋势分析开源项目PythonGolang

根据GithubTrendings的统计,本周(2024-04-29统计)共有15个项目上榜。根据开发语言中项目的数量,汇总情况如下:开发语言项目数量Python项目11TypeScript项目3Go项目1Svelte项目1JupyterNotebook项目1Swift项目1Ollama:本地大型语言模型设置与运行创建周期:248天开发语言:Go协议类型:MITLicenseStar数量:4242

- Github 2024-06-10开源项目周报 Top15

老孙正经胡说

github开源Github趋势分析开源项目PythonGolang

根据GithubTrendings的统计,本周(2024-06-10统计)共有15个项目上榜。根据开发语言中项目的数量,汇总情况如下:开发语言项目数量Python项目8JupyterNotebook项目2Go项目2C++项目1Shell项目1Lua项目1JavaScript项目1MDX项目1C项目1HTML项目1Python-100天从新手到大师创建周期:2234天开发语言:Python,HTML

- 如何禁止Linux内核打印,一种更为合理的Linux内核打印机制

虎斑爱读书

如何禁止Linux内核打印

2020-04-26关键字:printk_ratelimit、printk_ratelimited在Linux内核开发中,几乎所有的日志、信息的打印都是通过printk()函数实现的。printk首先会将所有来自程序的信息都放到一个缓冲区中,然后各个“监控程序”再根据自己的需要将这些信息读取出来。如console会将日志信息直接显示在屏幕上等。Linux内核中的日志缓冲区本质上就是一个环形FIFO

- golang 入门

weixin_34102807

golangphpffmpeg

缘起之前下载视频用的you-get,但是b站一直下不了,优酷也经常出问题,所以接触到luluhttps://github.com/iawia002/Lulu这个也是基于you-get直接pipinstalllulu,但是作者不维护了,新出了个https://github.com/iawia002/a...这个不是python开发的,而是go,通过gogetgithub.com/iawia002/a

- PHP实现站内搜索的开源利器——WindSearch

rock365337

WindSearchphp开源搜索引擎

WindSearch是一个基于中文分词,由纯PHP开发全文检索引擎,可快速搭建PHP站点的站内搜索,他没有任何繁琐的安装配置、不需要维护调优、不占用服务器内存、可与PHP项目完美融合在一起。github地址:https://github.com/rock365/windsearch必须极速安装~使用composer安装:composerrequirerock365/windsearch或使用Git

- IAR加入Zephyr项目成为银牌会员,强化对开源协作的承诺

电子科技圈

IAR开源嵌入式硬件物联网mcuiot智能家居设计模式

全球领先的嵌入式系统开发软件解决方案供应商IAR宣布,正式加入Zephyr项目,成为银牌会员。Zephyr是由Linux基金会托管并广泛应用于嵌入式行业的开源实时操作系统(RTOS),已得到众多嵌入式领域的重要企业支持。此次合作充分彰显了IAR对开源社区的深度承诺,致力于为开发者提供专业级工具和解决方案,同时助力ZephyrRTOS在嵌入式开发领域的持续发展。Zephyr是一款轻量级的开源实时操作

- 分析React和Vue的区别与优势

Neo Evolution

前端框架

React和Vue是目前两种非常流行的前端框架/库,它们各自有独特的设计理念和特点。下面是它们在各个方面的比较,包括架构、学习曲线、性能等。1.架构与理念React:开发类型:React是一个UI库,专注于视图层的构建。它本身没有集成像Vue或Angular那样的完整框架,所以需要与其他库或工具结合使用(如ReactRouter、Redux、ContextAPI等)。设计理念:React强调组件化

- 使用WebStorm开发Vue3项目

泡泡Java

面试学习路线阿里巴巴webstormrustide

记录一下使用WebStorm开发Vu3项目时的配置现在WebStorm可以个人免费使用啦!??基本配置打包工具:Vite前端框架:ElementPlus开发语言:Vue3、TypeScript、Sass代码检查:ESLint、PrettierIDE:WebStorm2024.2首先说一下版本兼容问题,ElementPlus>=2.8.5需要Sass>=1.79.0,但是升级了Sass后,会导致El

- 2025vue4.x全栈学习关键技术分析线路图

mabanbang

web前端学习vue4vue4.x

关键升级点说明:编译优化:Vue4.x采用WASM编译提速300%智能工具链:Vite插件市场新增AI代码审查模块跨平台能力:Uni-App支持原生ARCore/ARKit调用安全增强:默认启用WebAuthn生物认证集成建议配合Vue官方推出的「2025开发者成长计划」分阶段学习,重点关注AI工程化和元宇宙场景开发能力培养。TypeScript6.x深度集成类型推断速度提升

- 第一个问题:AI会威胁人类吗?

释迦呼呼

AI一千问人工智能

第一个问题:AI会威胁人类吗?对于这个问题,我的回答是:AI本身并不会威胁人类,但其是否构成威胁取决于人类如何设计、使用和监管它。下面我将从几个角度详细分析。AI的本质:人类的工具AI(人工智能)是由人类创造的工具,它的行为和决策完全基于人类设计的算法和输入的数据。换句话说,AI没有自己的意识、意图或独立的目标,因此它本身并不具备威胁人类的动机或能力。它的作用是由开发者、使用者和管理者决定的。AI

- 深入剖析 C++ 中的迪杰斯特拉算法

小白布莱克

c++算法开发语言

在图论算法的领域中,迪杰斯特拉(Dijkstra)算法是一颗璀璨的明星,它在解决单源最短路径问题上发挥着关键作用。对于学习C++编程的开发者来说,掌握迪杰斯特拉算法不仅能加深对算法思维的理解,还能在实际项目中有效解决诸多路径规划相关问题。迪杰斯特拉算法原理迪杰斯特拉算法是一种贪心算法,用于计算一个节点到图中其他所有节点的最短路径。它的核心思想是:从源节点出发,每次从未确定最短路径的节点中选择距离源

- 嵌入式LINUX驱动开发(三)-设备树驱动led

Lllongroad

linux驱动开发运维

1)添加pinctrl节点使用开发板自带的LED灯进行操作,打开dts文件,在iomuxc_snvs下创建一个“pinctrl_led的子节点”```pinctrl_leds:ledgrp{fsl,pins=;};```2)添加LED设备节点在根节点"/"创建LED灯节点,节点名称为**"gpioled"**,节点内容如下:```gpioled{#address-cells=;#size-cell

- 鸿蒙原生绘图API:从基础到高阶的绘制之旅(基础版)

theme:hydrogen大家好,欢迎来到莓创IT技术分享频道,我是陈杨。由于经常有小伙伴一直给我反馈说莓创图表(mccharts)数据多的时候经常卡顿,很无奈之前做动画的时候没考虑ArkTs的性能瓶颈,导致现在又要重构开发。于是我重新翻阅文档,看看有没有新的方式来解决。在翻阅官网文档的时候,无意间看到这句话。发现了@ohos.graphics.drawing模块性能竟然比canvas好,所以最

- Github 2025-02-17 开源项目周报Top15

老孙正经胡说

github开源Github趋势分析开源项目PythonGolang

根据GithubTrendings的统计,本周(2025-02-17统计)共有15个项目上榜。根据开发语言中项目的数量,汇总情况如下:开发语言项目数量Python项目7TypeScript项目6JupyterNotebook项目2JavaScript项目1文档项目1PHP项目1从零开始构建你喜爱的技术创建周期:2156天Star数量:253338个Fork数量:24043次关注人数:253338人

- Spring 核心技术解析【纯干货版】- XI:Spring 数据访问模块 Spring-Oxm 模块精讲

栗筝i

栗筝i的Java技术栈#Java框架-专栏springpython数据库

在现代Java开发中,XML仍然是数据存储和数据交换的重要格式,特别是在Web服务、配置管理和数据持久化等场景中。Spring框架提供了Spring-OXM(Object/XMLMapping)模块,旨在简化Java对象与XML之间的转换,并支持多种OXM实现,如JAXB、Castor、XStream、JibX等。本篇文章深入解析了Spring-OXM模块的核心概念,并结合JAXB进行详细示例,展

- 2025asp.net全栈技术开发学习路线图

mabanbang

asp.netcore开发asp.net全栈技术

2025年技术亮点:Blazor已全面支持WebAssembly2.0标准.NET8+版本原生集成AI模型部署能力AzureKubernetes服务实现智能自动扩缩容EFCore新增向量数据库支持特性ASP.NET全栈开发关键技术说明(2025年视角)以下技术分类基于现代企业级应用开发需求:前端生态Blazor是微软基于WebAssembly的前端框架,允许开发者直接使用C#替代Ja

- 第一章:认识Tailwind CSS - 第三节 - Tailwind CSS 开发环境搭建和工具链配置

1.必备环境准备Node.js(v14.0.0或更高版本)npm或yarn包管理器代码编辑器(推荐VSCode)2.项目初始化方式方式一:在新项目中使用#创建项目目录mkdirmy-tailwind-projectcdmy-tailwind-project#初始化package.jsonnpminit-y#安装必要依赖npminstall-Dtailwindcsspostcssautoprefix

- PHP实现站内搜索的开源利器——WindSearch

WindSearch是一个基于中文分词,由纯PHP开发全文检索引擎,可快速搭建PHP站点的站内搜索,他没有任何繁琐的安装配置、不需要维护调优、不占用服务器内存、可与PHP项目完美融合在一起。github地址:https://github.com/rock365/windsearch必须极速安装~使用composer安装:composerrequirerock365/windsearch或使用Git

- 【CXX】4 跨平台构建系统特性对比

Source.Liu

CXXrustc++CXX

多语言构建系统选项为开发团队提供了灵活性和选择,以适应不同的项目需求和现有的技术栈。CXX作为一个设计灵活的工具,旨在与多种构建系统无缝集成。以下是对不同构建系统选项的简要概述和建议:一、Cargo:适用场景:如果你的项目或团队正在探索Rust和C++的混合开发,或者计划大量使用Rust包注册表中的开源库,那么Cargo可能是一个很好的选择。优势:Cargo是Rust的官方构建系统,它提供了依赖管

- vue生命周期函数可以操作dom_vue生命周期钩子函数

weixin_42299873

前言在使用vue开发的过程中,我们经常会接触到生命周期的问题。那么你知道,一个标准的工程项目中,会有多少个生命周期勾子吗?让我们来一起来盘点一下:根组件实例:8个(beforeCreate、created、beforeMount、mounted、beforeUpdate、updated、beforeDestroy、destroyed)组件实例:8个(beforeCreate、created、bef

- android 框架组件,Android 架构组件介绍

臀总

android框架组件

Android架构组件介绍Android,Architecture,Components,架构2018.08.08我们在Android开发的过程中,总是在和一些问题纠缠,比如在生命周期的管理,在屏幕旋转的时候重新布局,绘制,保存还原数据等。我们也一直在致力于减少内存的占用,减少内存泄漏的风险,优化我们的代码,特别在大项目中,要增加代码的可维护性。AndroidArchitectureCompone

- verilog基础知识

寒听雪落

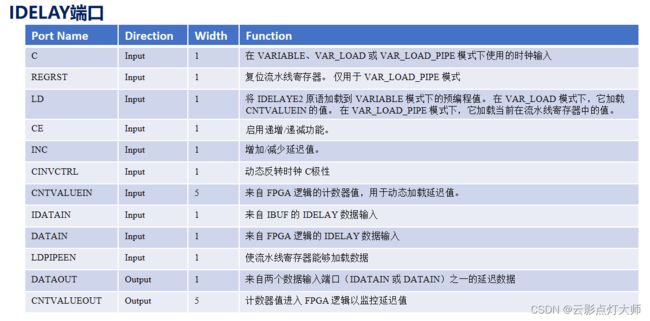

FPGA专栏_verilogfpga开发

一,Verilog和VHDL区别全世界高层次数字系统设计领域中,应用Verilog和VHDL的比率是80%和20%;这两种语言都是用于数字电路系统设计的硬件描述语言,而且都已经是IEEE的标准。VHDL是美国军方组织开发的,VHDL1987年成为标准;Verilog是由一个公司的私有财产转化而来,Verilog是1995年成为标准。Verilog有更强的生命力,后来Verilog成为IEEE标准这

- vcpkg 安装 使用技巧 (详细-建议收藏)

Nsequence

开发语言

一、vcpkg简介vcpkg是一个用于管理C++库的开源工具,由微软推出。它可以帮助开发者轻松地获取、构建和安装大量的C++开源库,解决了在不同平台上编译和管理第三方库的复杂性问题,尤其在Windows平台下优势明显。二、vcpkg的安装(1)下载vcpkg从vcpkg的GitHub仓库()下载最新版本的vcpkg。你可以使用Git克隆仓库,命令如下:```gitgitclonehttps://g

- GTSAM 库详细介绍与使用指南

点云SLAM

点云数据优化工具GTSAMSLAM后端优化最小二乘法计算机视觉贝叶斯

GTSAM库详细介绍与使用指南一、GTSAM概述GTSAM(GeorgiaTechSmoothingandMapping)是由佐治亚理工学院开发的C++开源库,专注于概率图模型(尤其是因子图)的构建与优化,广泛应用于机器人定位与建图(SLAM)、传感器融合、运动规划等领域。其核心优势在于:高效的因子图优化:支持贝叶斯网络建模与非线性优化。增量式求解器(iSAM/iSAM2):适用于实时SLAM问题

- Java vs C++:2025年编程语言之争——谁将主宰未来?

爱吃青菜的大力水手

javac++开发语言

在编程的世界里,Java和C++是两门经久不衰的语言,各自凭借独特的优势吸引了大量IT工作者的关注。无论是企业级开发还是高性能系统编程,这两门语言都在各自的领域中扮演着重要角色。本文深入调研并对比Java和C++在市场份额、插件丰富度、学习成本、安全性等方面的表现,帮助您理解它们的优势与应用场景,并在选择编程语言时做出明智决策。1.市场份额与流行度根据TIOBE指数(2024年最新数据),Java

- Springboot Maven打包跳过测试的五种方式总结 -Dmaven.test.skip=true

泡泡Java

面试学习路线阿里巴巴springbootmaven后端

使用Maven打包的时候,可能会因为单元测试打包失败,这时候就需要跳过单元测试。也为了加快打包速度,也需要跳过单元测试。Maven跳过单元测试五种方法。在正式环境中运行Springboot应用,需要先打包,然后使用java-jarxx.jar就能运行我们的项目。我们平时使用的在开发中使用的是开发或测试的数据库,和生产上面的一般是隔离的,意味着打包的时候需要激活生产的配置文件,但是我们不一定有访问生

- 函数调用和 Java 与 Spring AI 模型的集成

算法资料吧!

javaspring人工智能

SpringAI是一个功能强大的SpringFramework项目,它为Java开发人员带来了人工智能(AI)功能。通过将AI模型集成到Java应用程序中,SpringAI简化了创建智能应用程序的过程,同时利用了Spring生态系统的稳健性。本文将指导您完成使用SpringAI将AI模型集成到Java应用程序中的步骤,特别关注允许AI模型与外部数据源和服务动态交互的函数调用机制。SpringAIS

- rust 实例化动态对象

heroboyluck

rustrust开发语言trait

在功能开发中,动态创建或获取某个对象的情况很多。在前端JS开发中,可以使用工厂函数,通过给定的类型标识创建不同的对象实例;还可以通过对象映射来实现动态创建对象。在Rust中,我们也可以使用这两种方式去创建对象实例,但实现书写的方式可能略有不同;rust还可以通过序列化JSON数据时进行枚举类型匹配。我们定义好需要测试的数据结构体、方法。小狗、小猫有自己的字段、方法,它们有相同的字段name,也有相

- Java Web开发:从入门到实战的技术之旅

计算机学长

java开发工具开发语言java

一、JavaWeb开发初印象在互联网技术飞速发展的当下,JavaWeb开发已成为构建各类网络应用的中流砥柱。简单来说,JavaWeb开发就是利用Java语言及其相关技术,开发出能够在Web服务器上运行,并通过浏览器等客户端进行访问的应用程序。这些应用程序可以是功能丰富的网站、交互性强的Web应用,也可以是复杂的企业级信息系统,广泛应用于电商、金融、教育、医疗等各个领域。当我们在淘宝上尽情购物、在支

- [黑洞与暗粒子]没有光的世界

comsci

无论是相对论还是其它现代物理学,都显然有个缺陷,那就是必须有光才能够计算

但是,我相信,在我们的世界和宇宙平面中,肯定存在没有光的世界....

那么,在没有光的世界,光子和其它粒子的规律无法被应用和考察,那么以光速为核心的

&nbs

- jQuery Lazy Load 图片延迟加载

aijuans

jquery

基于 jQuery 的图片延迟加载插件,在用户滚动页面到图片之后才进行加载。

对于有较多的图片的网页,使用图片延迟加载,能有效的提高页面加载速度。

版本:

jQuery v1.4.4+

jQuery Lazy Load v1.7.2

注意事项:

需要真正实现图片延迟加载,必须将真实图片地址写在 data-original 属性中。若 src

- 使用Jodd的优点

Kai_Ge

jodd

1. 简化和统一 controller ,抛弃 extends SimpleFormController ,统一使用 implements Controller 的方式。

2. 简化 JSP 页面的 bind, 不需要一个字段一个字段的绑定。

3. 对 bean 没有任何要求,可以使用任意的 bean 做为 formBean。

使用方法简介

- jpa Query转hibernate Query

120153216

Hibernate

public List<Map> getMapList(String hql,

Map map) {

org.hibernate.Query jpaQuery = entityManager.createQuery(hql);

if (null != map) {

for (String parameter : map.keySet()) {

jp

- Django_Python3添加MySQL/MariaDB支持

2002wmj

mariaDB

现状

首先,Django@Python2.x 中默认的引擎为 django.db.backends.mysql 。但是在Python3中如果这样写的话,会发现 django.db.backends.mysql 依赖 MySQLdb[5] ,而 MySQLdb 又不兼容 Python3 于是要找一种新的方式来继续使用MySQL。 MySQL官方的方案

首先据MySQL文档[3]说,自从MySQL

- 在SQLSERVER中查找消耗IO最多的SQL

357029540

SQL Server

返回做IO数目最多的50条语句以及它们的执行计划。

select top 50

(total_logical_reads/execution_count) as avg_logical_reads,

(total_logical_writes/execution_count) as avg_logical_writes,

(tot

- spring UnChecked 异常 官方定义!

7454103

spring

如果你接触过spring的 事物管理!那么你必须明白 spring的 非捕获异常! 即 unchecked 异常! 因为 spring 默认这类异常事物自动回滚!!

public static boolean isCheckedException(Throwable ex)

{

return !(ex instanceof RuntimeExcep

- mongoDB 入门指南、示例

adminjun

javamongodb操作

一、准备工作

1、 下载mongoDB

下载地址:http://www.mongodb.org/downloads

选择合适你的版本

相关文档:http://www.mongodb.org/display/DOCS/Tutorial

2、 安装mongoDB

A、 不解压模式:

将下载下来的mongoDB-xxx.zip打开,找到bin目录,运行mongod.exe就可以启动服务,默

- CUDA 5 Release Candidate Now Available

aijuans

CUDA

The CUDA 5 Release Candidate is now available at http://developer.nvidia.com/<wbr></wbr>cuda/cuda-pre-production. Now applicable to a broader set of algorithms, CUDA 5 has advanced fe

- Essential Studio for WinRT网格控件测评

Axiba

JavaScripthtml5

Essential Studio for WinRT界面控件包含了商业平板应用程序开发中所需的所有控件,如市场上运行速度最快的grid 和chart、地图、RDL报表查看器、丰富的文本查看器及图表等等。同时,该控件还包含了一组独特的库,用于从WinRT应用程序中生成Excel、Word以及PDF格式的文件。此文将对其另外一个强大的控件——网格控件进行专门的测评详述。

网格控件功能

1、

- java 获取windows系统安装的证书或证书链

bewithme

windows

有时需要获取windows系统安装的证书或证书链,比如说你要通过证书来创建java的密钥库 。

有关证书链的解释可以查看此处 。

public static void main(String[] args) {

SunMSCAPI providerMSCAPI = new SunMSCAPI();

S

- NoSQL数据库之Redis数据库管理(set类型和zset类型)

bijian1013

redis数据库NoSQL

4.sets类型

Set是集合,它是string类型的无序集合。set是通过hash table实现的,添加、删除和查找的复杂度都是O(1)。对集合我们可以取并集、交集、差集。通过这些操作我们可以实现sns中的好友推荐和blog的tag功能。

sadd:向名称为key的set中添加元

- 异常捕获何时用Exception,何时用Throwable

bingyingao

用Exception的情况

try {

//可能发生空指针、数组溢出等异常

} catch (Exception e) {

- 【Kafka四】Kakfa伪分布式安装

bit1129

kafka

在http://bit1129.iteye.com/blog/2174791一文中,实现了单Kafka服务器的安装,在Kafka中,每个Kafka服务器称为一个broker。本文简单介绍下,在单机环境下Kafka的伪分布式安装和测试验证 1. 安装步骤

Kafka伪分布式安装的思路跟Zookeeper的伪分布式安装思路完全一样,不过比Zookeeper稍微简单些(不

- Project Euler

bookjovi

haskell

Project Euler是个数学问题求解网站,网站设计的很有意思,有很多problem,在未提交正确答案前不能查看problem的overview,也不能查看关于problem的discussion thread,只能看到现在problem已经被多少人解决了,人数越多往往代表问题越容易。

看看problem 1吧:

Add all the natural num

- Java-Collections Framework学习与总结-ArrayDeque

BrokenDreams

Collections

表、栈和队列是三种基本的数据结构,前面总结的ArrayList和LinkedList可以作为任意一种数据结构来使用,当然由于实现方式的不同,操作的效率也会不同。

这篇要看一下java.util.ArrayDeque。从命名上看

- 读《研磨设计模式》-代码笔记-装饰模式-Decorator

bylijinnan

java设计模式

声明: 本文只为方便我个人查阅和理解,详细的分析以及源代码请移步 原作者的博客http://chjavach.iteye.com/

import java.io.BufferedOutputStream;

import java.io.DataOutputStream;

import java.io.FileOutputStream;

import java.io.Fi

- Maven学习(一)

chenyu19891124

Maven私服

学习一门技术和工具总得花费一段时间,5月底6月初自己学习了一些工具,maven+Hudson+nexus的搭建,对于maven以前只是听说,顺便再自己的电脑上搭建了一个maven环境,但是完全不了解maven这一强大的构建工具,还有ant也是一个构建工具,但ant就没有maven那么的简单方便,其实简单点说maven是一个运用命令行就能完成构建,测试,打包,发布一系列功

- [原创]JWFD工作流引擎设计----节点匹配搜索算法(用于初步解决条件异步汇聚问题) 补充

comsci

算法工作PHP搜索引擎嵌入式

本文主要介绍在JWFD工作流引擎设计中遇到的一个实际问题的解决方案,请参考我的博文"带条件选择的并行汇聚路由问题"中图例A2描述的情况(http://comsci.iteye.com/blog/339756),我现在把我对图例A2的一个解决方案公布出来,请大家多指点

节点匹配搜索算法(用于解决标准对称流程图条件汇聚点运行控制参数的算法)

需要解决的问题:已知分支

- Linux中用shell获取昨天、明天或多天前的日期

daizj

linuxshell上几年昨天获取上几个月

在Linux中可以通过date命令获取昨天、明天、上个月、下个月、上一年和下一年

# 获取昨天

date -d 'yesterday' # 或 date -d 'last day'

# 获取明天

date -d 'tomorrow' # 或 date -d 'next day'

# 获取上个月

date -d 'last month'

#

- 我所理解的云计算

dongwei_6688

云计算

在刚开始接触到一个概念时,人们往往都会去探寻这个概念的含义,以达到对其有一个感性的认知,在Wikipedia上关于“云计算”是这么定义的,它说:

Cloud computing is a phrase used to describe a variety of computing co

- YII CMenu配置

dcj3sjt126com

yii

Adding id and class names to CMenu

We use the id and htmlOptions to accomplish this. Watch.

//in your view

$this->widget('zii.widgets.CMenu', array(

'id'=>'myMenu',

'items'=>$this-&g

- 设计模式之静态代理与动态代理

come_for_dream

设计模式

静态代理与动态代理

代理模式是java开发中用到的相对比较多的设计模式,其中的思想就是主业务和相关业务分离。所谓的代理设计就是指由一个代理主题来操作真实主题,真实主题执行具体的业务操作,而代理主题负责其他相关业务的处理。比如我们在进行删除操作的时候需要检验一下用户是否登陆,我们可以删除看成主业务,而把检验用户是否登陆看成其相关业务

- 【转】理解Javascript 系列

gcc2ge

JavaScript

理解Javascript_13_执行模型详解

摘要: 在《理解Javascript_12_执行模型浅析》一文中,我们初步的了解了执行上下文与作用域的概念,那么这一篇将深入分析执行上下文的构建过程,了解执行上下文、函数对象、作用域三者之间的关系。函数执行环境简单的代码:当调用say方法时,第一步是创建其执行环境,在创建执行环境的过程中,会按照定义的先后顺序完成一系列操作:1.首先会创建一个

- Subsets II

hcx2013

set

Given a collection of integers that might contain duplicates, nums, return all possible subsets.

Note:

Elements in a subset must be in non-descending order.

The solution set must not conta

- Spring4.1新特性——Spring缓存框架增强

jinnianshilongnian

spring4

目录

Spring4.1新特性——综述

Spring4.1新特性——Spring核心部分及其他

Spring4.1新特性——Spring缓存框架增强

Spring4.1新特性——异步调用和事件机制的异常处理

Spring4.1新特性——数据库集成测试脚本初始化

Spring4.1新特性——Spring MVC增强

Spring4.1新特性——页面自动化测试框架Spring MVC T

- shell嵌套expect执行命令

liyonghui160com

一直都想把expect的操作写到bash脚本里,这样就不用我再写两个脚本来执行了,搞了一下午终于有点小成就,给大家看看吧.

系统:centos 5.x

1.先安装expect

yum -y install expect

2.脚本内容:

cat auto_svn.sh

#!/bin/bash

- Linux实用命令整理

pda158

linux

0. 基本命令 linux 基本命令整理

1. 压缩 解压 tar -zcvf a.tar.gz a #把a压缩成a.tar.gz tar -zxvf a.tar.gz #把a.tar.gz解压成a

2. vim小结 2.1 vim替换 :m,ns/word_1/word_2/gc

- 独立开发人员通向成功的29个小贴士

shoothao

独立开发

概述:本文收集了关于独立开发人员通向成功需要注意的一些东西,对于具体的每个贴士的注解有兴趣的朋友可以查看下面标注的原文地址。

明白你从事独立开发的原因和目的。

保持坚持制定计划的好习惯。

万事开头难,第一份订单是关键。

培养多元化业务技能。

提供卓越的服务和品质。

谨小慎微。

营销是必备技能。

学会组织,有条理的工作才是最有效率的。

“独立

- JAVA中堆栈和内存分配原理

uule

java

1、栈、堆

1.寄存器:最快的存储区, 由编译器根据需求进行分配,我们在程序中无法控制.2. 栈:存放基本类型的变量数据和对象的引用,但对象本身不存放在栈中,而是存放在堆(new 出来的对象)或者常量池中(字符串常量对象存放在常量池中。)3. 堆:存放所有new出来的对象。4. 静态域:存放静态成员(static定义的)5. 常量池:存放字符串常量和基本类型常量(public static f