FPGA同步复位异步复位

今天看了篇博客,

是拿altera的芯片和软件作例子的,讲同步异步复位的:

http://blog.sina.com.cn/s/blog_bff0927b0101aaii.html

还有一个博客,

http://bbs.ednchina.com/BLOG_ARTICLE_201656_2.HTM

想起<设计与验证>这本书也讲过,

顺便说一下,这是一本非常好的书!

拿 ISE实验了一下,器件选了ZC702,发现看到的RTL级电路,都不一样,

个人觉得现在的FPGA与综合工具都很智能了,

很多小问题都不用太在意,比如下面这几个例子中,ISE会自动选择不同的D触发器去适应...

then why bother...

同事也常说,好的时序是设计出来的,不是约束出来的...好像和这个没多大关系,

嗯...比如常用的"打一拍",时钟相位修改,合理的乒乓,缓存RAM,FIFO的使用...

在大多数情况下都可以解决问题;

同步异步复位的优缺点,书中有讲,大概在80页左右;

如下:

[同步复位]

优点,有效去毛刺,因为只有在时钟沿到来时,复位才能生效;

缺点,多消耗了组合逻辑资源,复位时间不能太短,否则复位不完全;

如代码段,

module reset( input clk, input reset, input in, output out ); reg test; always @( posedge clk ) if(reset) test <= 1'b0; else test <= in; assign out = test; endmodule

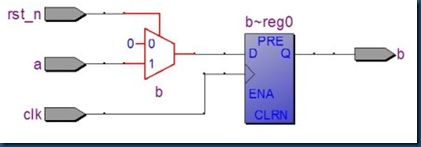

博客和书中说,大多数FPGA中的触发器没有同步复位端,所以会多出一些组合逻辑,如

盗个图,

这就是多出来的资源,另外FPGA中DFF资源多一些,组合逻辑少一些;

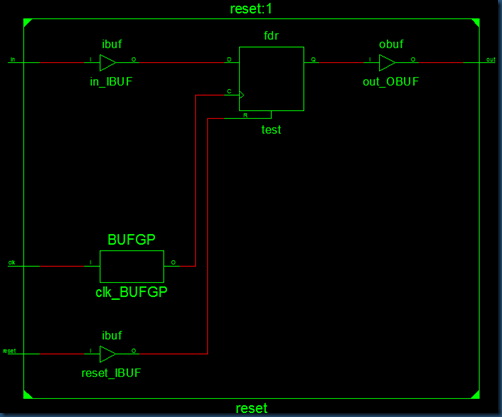

而我用ISE出来的是,并没有额外多出组合逻辑,

查了fdr的源语,

// FDRE: Single Data Rate D Flip-Flop with Synchronous Reset and // Clock Enable (posedge clk). // Artix-7 // Xilinx HDL Language Template, version 14.4 FDRE #( .INIT(1'b0) // Initial value of register (1'b0 or 1'b1) ) FDRE_inst ( .Q(Q), // 1-bit Data output .C(C), // 1-bit Clock input .CE(CE), // 1-bit Clock enable input .R(R), // 1-bit Synchronous reset input .D(D) // 1-bit Data input ); // End of FDRE_inst instantiation

既然是源语,所以我觉得这个片子里是有,带同步复位的D-FF的,

也许现在大多数FPGA都有了...

如果有同学说,再底层是不是还是普通的D-FF+组合逻辑,那就不清楚了...

所以个人觉得使用类似FPGA用同步复位时也不必再担心浪费资源了;

[异步复位]

优点,快速复位,消耗资源少;

缺点,不利于时序约束,复位也容易受到毛刺影响,从而造成不稳定;

如代码段,

module reset( input clk, input reset, input in, output out ); reg test; always @( posedge clk or posedge reset ) if(reset) test <= 1'b0; else test <= in; assign out = test; endmodule

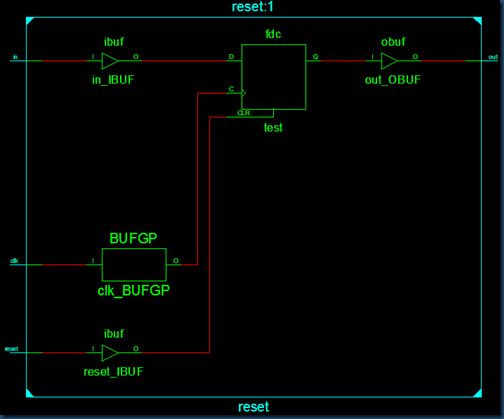

书中说,大多数FPGA,CPLD都有异步复位端,所以RTL级图如下,

异步清零的DFF

// FDCE: Single Data Rate D Flip-Flop with Asynchronous Clear and // Clock Enable (posedge clk). // Artix-7 // Xilinx HDL Language Template, version 14.4 FDCE #( .INIT(1'b0) // Initial value of register (1'b0 or 1'b1) ) FDCE_inst ( .Q(Q), // 1-bit Data output .C(C), // 1-bit Clock input .CE(CE), // 1-bit Clock enable input .CLR(CLR), // 1-bit Asynchronous clear input .D(D) // 1-bit Data input ); // End of FDCE_inst instantiation

[另外]

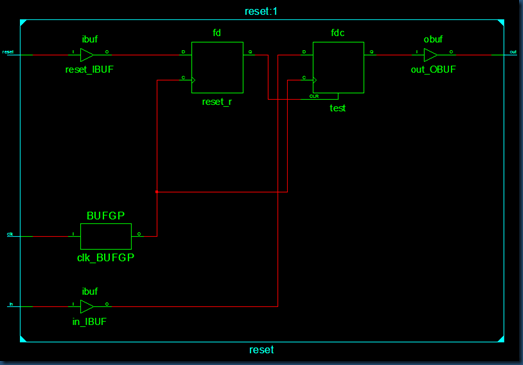

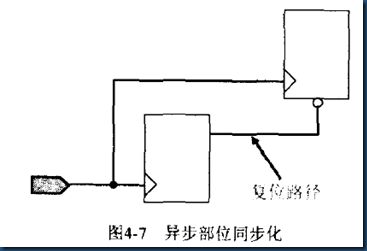

书中和博客中给出了解决方法,就是把异步复位信号,"打一拍"再使用,

叫同步释放,异步复位,代码段

module reset( input clk, input reset, input in, output out ); reg test; reg reset_r; always @( posedge clk ) begin reset_r <= reset; end always @( posedge clk or posedge reset_r) if(reset_r) test <= 1'b0; else test <= in; assign out = test; endmodule

ISE下RTL图,如下,

即书中的图,

这样做肯定更好,更容易去掉毛刺;

但如果时序没那么差,而且FPGA内部有了同步复位的DFF,能省则省了;

另外复位的重要性与同步复位的复位时间要求,书中有介绍;