ARM Cortex-A学习(3):MMU内存管理单元

内存管理单元(MMU)负责虚拟地址到物理地址的转换。MMU通过翻译表将程序使用的虚拟地址映射到实际的物理内存位置,实现对内存的动态管理和隔离。这不仅允许更灵活的内存分配,还提高了系统的安全性和稳定性。了解MMU的工作原理对于开发底层代码、BootLoader和驱动程序都很重要。

文章目录

- 1 虚拟地址和物理地址

- 2 MMU

-

- 2.1 表的条目

- 2.2 表的查找

- 2.3 多级页表

- 3 例:ARMv8-A的地址空间

- 4 总结

1 虚拟地址和物理地址

关于虚拟地址的概念,可以参考我的这篇文章:物理地址、链接地址、加载地址、虚拟/逻辑地址的区别

虚拟地址允许操作系统控制呈现给应用程序的内存视图,如操作系统可以控制内存的可见性和访问权限。这使得操作系统能够对应用程序进行沙盒化,并提供对底层硬件的抽象。它的好处如下:

-

操作系统可以将多个分散的物理内存区域呈现为一个连续的虚拟地址空间供应用程序使用。

-

软件开发人员无需关心物理内存,地址转换是由操作系统和硬件共同完成的。

在实际应用中,每个应用程序可以使用自己的一组虚拟地址,将其映射到物理系统中的不同位置。当操作系统将控制权从一个应用程序转移到另一个应用程序时,它会更新内部的映射表,以确保当前运行的应用程序的虚拟地址正确地映射到物理内存中的相应位置。这样,即使不同应用程序使用相同的虚拟地址,它们实际上指向不同的物理内存位置,从而实现了应用程序之间的隔离和独立性。

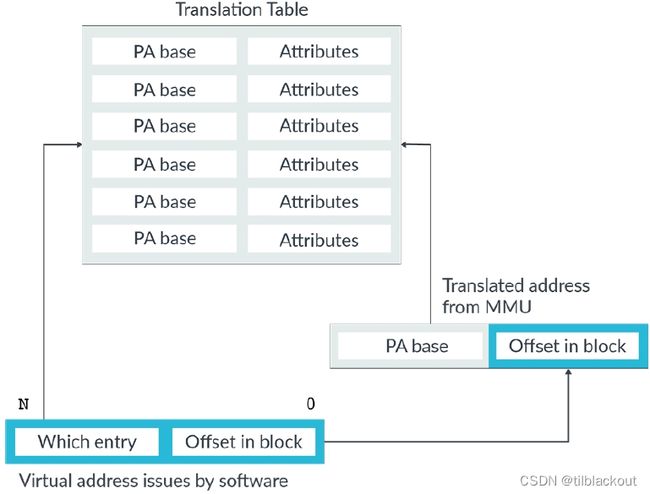

虚拟地址和物理地址之间通过翻译页表进行映射:

翻译页表存储在内存中,通常由操作系统进行管理。页表的映射可以通过软件配置,从而改变虚拟地址和物理地址之间的映射关系。

2 MMU

MMU执行地址转换操作,它包含以下组成部分:

- 表遍历单元:包含从内存读取翻译页表的逻辑

- 翻译后备缓冲区(

TLBs,Translation Lookaside Buffers):用于缓存最近使用的页表翻译转换结果,这可以加快内存的访问速度

由软件发出的内存地址都是虚拟的,虚拟地址传递给MMU,MMU检查TLBs缓存,若缓存未命中,则表遍历单元将从主存中读取数据并缓存,如下所示:

在访问内存之前,虚拟地址必须被翻译为物理地址。另外,在Armv6及更高版本的处理器上,数据缓存使用物理地址(物理标记的地址)存储数据。所以,在进行缓存查找时,需要提前将虚拟地址翻译为物理地址。

2.1 表的条目

翻译页表通过将虚拟地址空间分成相等大小的块,并为每个块在表中提供一个条目来实现。

- 翻译表的每个条目对应着虚拟地址空间中的一个块,而这些块会被映射到物理地址空间的相应块。

- 表中的第0个条目对应着虚拟地址空间中的块0,第1个条目对应着块1,以此类推。

- 表中条目包含相应物理内存块的地址以及访问该物理地址时要使用的属性(如读/写/缓存策略等)。

2.2 表的查找

表查找发生在虚拟地址转化为物理地址的时候。此时,由软件发出的虚拟地址被分为两部分:

上图为单层查找的例子。其中:

Which entry:应该查找哪个块条目,并将其用作对表的索引,该块条目包含虚拟地址对应的物理地址Offset in block:块内的偏移,翻译过程中不会改变

2.3 多级页表

在2.1中的图为单级查找,虚拟地址空间被分割成相等的大小。但在实际的页表实现中是使用多级页表实现的。

一级表将虚拟地址空间分割成大块,该表中的每个条目可以指向相等大小的物理内存块,或者它可以指向另一个表,该表将块细分为更小的块。下图是三级多级页表的示例:

在Armv8-A架构中,多级表的最大级别为四级(0到3)。虚拟地址空间被划分为不同级别的表,第一级表负责将虚拟地址空间分成大块,而每个表项可以指向相等大小的物理内存块,或者指向另一个表,该表将块细分为更小的块。这种多级结构的设计使得系统可以同时处理大范围的内存块和较小的内存块,从而在灵活性和效率之间找到平衡。

- 大块相对于小块需要更少的读取级别来进行转换,大块在

TLB中缓存更高效 - 小块使软件能够对内存分配进行精细控制,但小块在

TLB中的缓存效率较低,因为小块需要通过多个级别进行多次读取以进行转换 - 为了平衡使用大映射的效率与使用小映射的灵活性以获得最佳性能,操作系统必须管理这种权衡

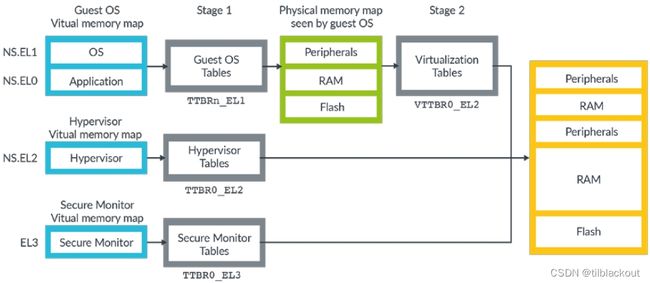

3 例:ARMv8-A的地址空间

不同的异常等级(Exception Level,EL)通常对应于不同的特权级别和内存空间。每个EL都有其自己的地址空间和访问权限。这种设计提供了对系统资源的分隔和管理,同时允许在不同特权级别上运行不同的软件实体,如用户空间应用程序、操作系统内核、虚拟化管理器等。

这里以ARMv8-A为例,在ARMv8-A架构中有以下4种EL:

- EL0(用户空间): 通常用于运行普通应用程序代码,访问受限制的用户空间内存。

- EL1(内核空间): 用于运行操作系统内核代码,具有更高的特权级别和对系统资源的更广泛访问权限。

- EL2(hypervisor级别): 通常用于虚拟化支持,允许运行多个虚拟机实例。它有自己的地址空间和控制权,可以管理虚拟机的运行。

- EL3(监管者级别): 可能用于处理一些与系统安全性相关的任务,例如启动过程中的安全任务。它也有自己的地址空间和特权级别。

-

图中

EL前面的NS表示Non-Secure,图表中未显示Secure EL0、Secure EL1和Secure EL2的虚拟地址空间,实际上EL0-EL3也是有安全空间的。 -

由于存在多个虚拟地址空间,指定一个地址属于哪个地址空间变得很重要

- 例如,

NS.EL2:0x8000指的是在非安全hypervisor级别(NS.EL2)的虚拟地址空间中的0x8000。在其它的EL中也可以有自己的0x8000.

- 例如,

虚拟化

从上图还可知,Non-secure EL0和Non-secure EL1的虚拟地址经过两组表。这些表支持虚拟化,并允许hypervisor(即虚拟机监控程序,位于NS.EL2)虚拟化虚拟机所看到的物理内存视图。

虚拟化分为两个阶段:

(1)第一阶段:表由操作系统控制,它将虚拟地址翻译为中间物理地址(intermediate physical addresses,IPA)。在第一阶段中,操作系统认为这些IPAs是物理地址空间。

(2)第二阶段:虚拟机监控程序(hypervisor)控制第二组翻译,它将IPAs翻译为物理地址

尽管表格格式存在细微的差异,但通常阶段1和2的地址翻译过程是相同的。

4 总结

本文大概地介绍了一下ARM中MMU的概念,主要是了解一下在Cortex-A核中有这样一个内存管理单元,它可以将虚拟地址转化为物理地址。对于具体地,内存是如何映射的,TLB表格是如何缓存的等知识,都与操作系统的实现有关,后续我们学到Linux再介绍。