vivado 使用项目摘要、配置项目设置、仿真设置

使用项目摘要

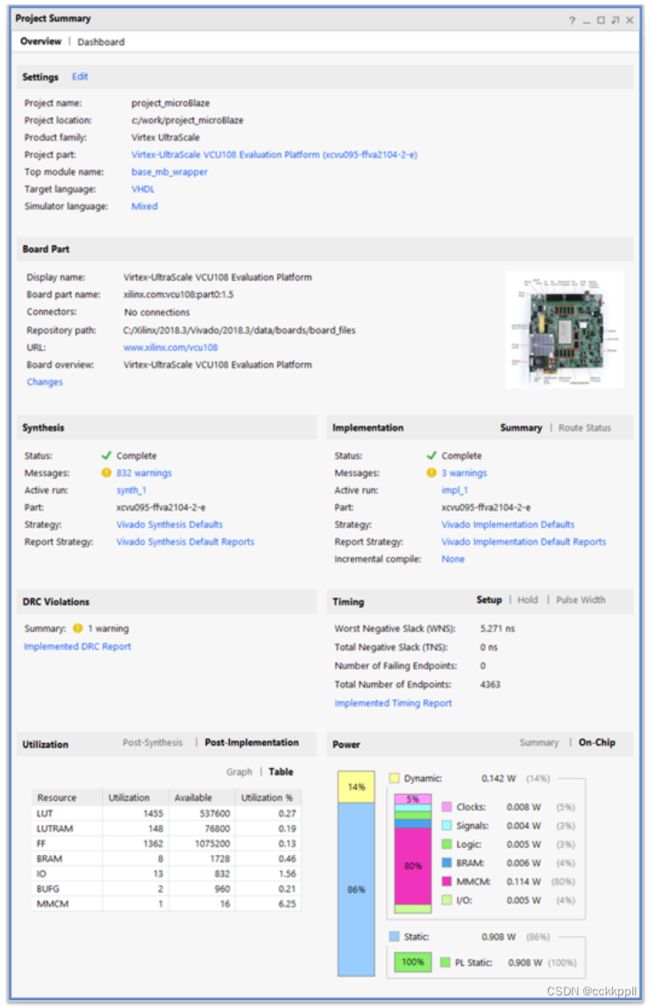

Vivado IDE包括一个交互式项目摘要,可根据设计动态更新命令被运行,并且随着设计在设计流程中的进展。项目摘要包括概览选项卡和用户可配置的仪表板,如下图所示。有关信息,请参阅《Vivado Design Suite用户指南:使用Vivado IDE(UG893)》中的此链接。

要打开“项目摘要”,请执行以下任一操作:

•选择Windows → 项目摘要。

•选择“项目摘要”工具栏按钮。

注意:默认情况下会显示“项目摘要”中的“概述”选项卡。

配置项目设置

您可以配置设置以满足每个项目的特定需要。设置包括常规与顶部模块定义相关的设置以及以下设置:仿真,合成、实现、比特流和IP。

要打开“设置”对话框,请使用以下任意方法:

•选择工具 → 设置。

•单击“设置”工具栏按钮。

•在“流导航器”中,单击“项目管理器”部分中的“设置”,或右键单击其中一个以下内容:

•SIMULATION:打开模拟设置

•RTL分析:打开精化设置

•合成:打开合成设置

•实施:打开实施设置

•程序和调试:打开比特流设置

•在“项目摘要”中,单击“设置”标题旁边的“编辑”链接,或单击策略或“合成”或“实现”部分中的流程。

根据调用“设置”对话框的方式,相应的类别显示为违约例如,如果单击“流导航器”中的“模拟设置”,则“模拟”类别显示在“设置”对话框中。以下各节提供了详细信息对于每个类别。

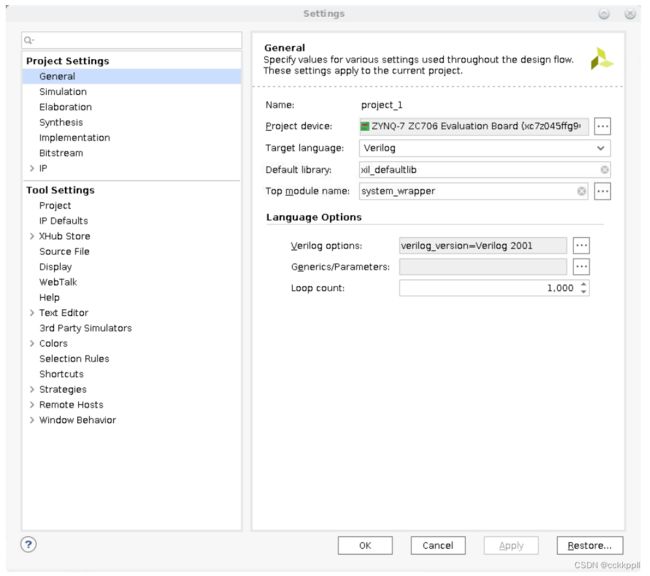

常规设置

常规设置允许您指定项目名称、零件、目标语言、目标模拟器、顶部模块名称和语言选项。

•名称:指定项目名称。

•项目设备:指定要用作合成和实施单击浏览按钮打开选择设备对话框以选择装置

注意:如果您有多个合成或实现运行,您也可以更改用于通过在“运行属性”窗口中更改运行设置,可以执行特定的运行。有关更多信息,请参阅Vivado Design Suite用户指南:使用Vivado IDE(UG893)。

•目标语言:指定设计的目标输出语言为Verilog或VHDL。该工具以指定的目标语言从设计中生成RTL输出。由目标语言控制的输出的具体示例是合成、模拟、顶级包装器、测试台和IP实例化模板。

•默认库:指定项目的默认库。没有显式库的所有文件规范在这个库中编译。可以选择库名称,也可以指定新库名称,方法是在库文本字段中键入。

•顶部模块名称:指定设计的顶部RTL模块名称。您也可以输入较低级别的模块名称,用于在特定模块上进行合成实验。单击浏览按钮自动搜索顶部模块并显示可能的顶部模块列表。

•语言选项:

重要!此处的设置适用于合成。您还可以定义Verilog选项和Generics/“设置-仿真”对话框中的“参数”选项。模拟设置应用于模拟文件集并影响模拟,但不影响合成。

•Verilog选项:单击浏览按钮在Verilog中设置以下选项“选项”对话框。

•Verilog Include Files Search Paths:指定搜索引用文件的路径'在源Verilog文件中包含语句。

•定义:指定项目的Verilog宏定义。

•大写所有标识符:将所有Verilog标识符设置为大写。

•泛型/参数:VHDL支持泛型,而Verilog支持定义参数对于常数值。这两种技术都允许参数化设计

在不同的情况下重复使用。单击浏览按钮以定义常规和参数值来覆盖在源文件中定义的默认值。

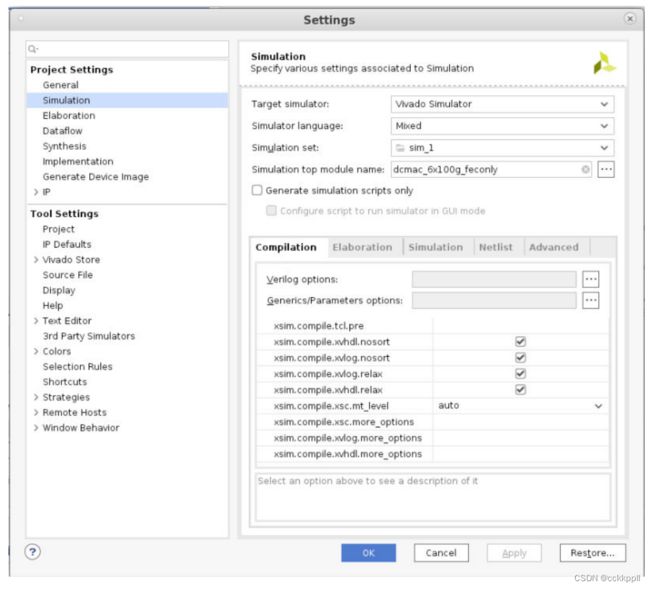

仿真设置

通过模拟设置,可以指定模拟集,即模拟顶部模块名称,以及编译和模拟选项的选项卡列表。您可以选择一个选项来查看对话框底部的说明。有关“仿真设置”的详细信息,请参阅《Vivado Design Suite用户指南:逻辑仿真》中的“使用仿真设置”部分(UG900)。

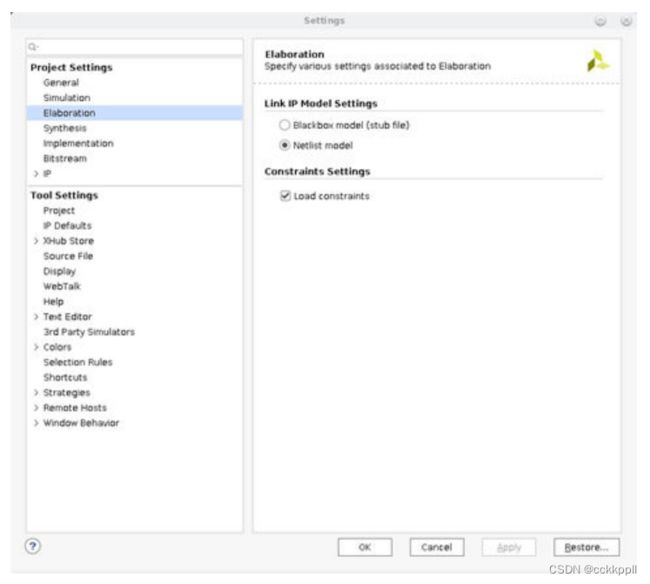

精化设置

在打开详细设计时,如第4章:RTL分析中所述,有两个可以启用或禁用的设置,以更改RTL设计的细节,如所示如下图所示。精化页面允许您为精化网表视图设置选项。此视图是可从RTL分析中的流导航器获得 → 开放式精心设计。

•链接IP模块选项:黑盒模型(存根文件):将所有断章取义合成的IP视为黑盒。网表模型:使用IP的合成网表断章取义地合成。

•约束选项:载荷约束:将所有活动约束应用于详细设计(时间和物理)。可以在源文件集上定义以下Tcl命令,以实现RTL细化设置: