【FPGA & Modsim】数字时钟

实验题目: 数字时钟设计

实验目的: 掌握数字时钟的工作原理;掌握使用数字逻辑设计集成开发环境分模块设计数字时钟的方法。

实验内容:

1、创建一个数字时钟工程,使用六位数码管实时显示时/分/秒。

3、时钟应具有稳定的计时功能,能够连续运行并准确显示时间。

实验步骤:

1、明确实验要求,确定系统功能,设计整体方案。

2、按照实现功能将数字时钟设计系统划分为时钟基准、显示驱动、按键控制等模块。

3、使用 Verilog HDL 编写各模块的逻辑代码。

4、在仿真环境中测试各模块的功能。

实验数据记录:

分模块写出编写的Verilog HDL源程序。

1、时钟顶层模块:

Module Clocktime(

input clk,

input rst_n,

output [5:0] seconds,

output [5:0] minutes,

output [5:0] hours,

output [7:0] seg,

output [3:0] digit,

output clk_base1

);

clk_base Uclk_base(

.clk(clk),

.rst_n(rst_n),

.clk_in(clk_base1) //生成基准时钟

);

clock_generator Uclock_generator( //根据基准时钟进行计数

.clk(clk_base1),

.rst_n(rst_n),

.seconds(seconds),

.minutes(minutes),

.hours(hours)

);

display_driver Udisplay_driver (

.seconds(seconds),

.minutes(minutes),

.hours(hours),

.seg(seg),

.digit(digit)

);

endmodule

endmodule

2、显示驱动模块(Display Driver):

module display_driver (

input wire [5:0] seconds,

input wire [5:0] minutes,

input wire [5:0] hours,

output reg [7:0] seg,

output reg [3:0] digit

);

always @(*) begin

case ({hours, minutes, seconds})

6'b000000: begin seg = 8'b11111100; digit = 4'b0000; end// 0

6'b000001: begin seg = 8'b01100000; digit = 4'b0001; end// 1

6'b000010: begin seg = 8'b11011011; digit = 4'b0010; end// 2

6'b000011: begin seg = 8'b11110010; digit = 4'b0011; end// 3

6'b000100: begin seg = 8'b01100111; digit = 4'b0100; end// 4

6'b000101: begin seg = 8'b10110110; digit = 4'b0101; end// 5

6'b000110: begin seg = 8'b10111111; digit = 4'b0110; end// 6

6'b000111: begin seg = 8'b11100001; digit = 4'b0111; end// 7

6'b001000: begin seg = 8'b11111111; digit = 4'b1000; end// 8

6'b001001: begin seg = 8'b11110111; digit = 4'b1001; end// 9

default: begin seg = 8'b00000000; digit = 4'b0000; end// Error

endcase

end

Endmodule

3.时间基准模块

module clk_base

(

input clk,

input rst_n,

//分频后的时钟

output reg clk_in

//输出时钟

);

reg [25:0]ct ;

//时钟分频计数

//时钟分频,生成500KHz的测试时钟

always@(posedge clk or negedge rst_n) begin

if(rst_n== 1 'b0) begin

ct<= 0;

clk_in<= 0 ;

end

else begin

if(ct==26'd24999999) begin

ct<= 26'd0;

clk_in<=~clk_in;

end

else

ct<=ct + 1'b1 ;

end

end

endmodule

4.时钟参考信号

module clock_generator (

input wire clk,

input wire rst_n,

output reg [5:0] seconds,

output reg [5:0] minutes,

output reg [5:0] hours

);

always @(posedge clk or negedge rst_n) begin

if (~rst_n) begin

seconds <= 6'd0;

minutes <= 6'd0;

hours <= 6'd0;

end else begin

seconds <= seconds + 6'd1;

if (seconds == 6'd60) begin // 一分钟的秒数

seconds <= 6'd0;

minutes <= minutes + 6'd1;

end

if (minutes == 6'd60) begin // 一小时的分钟数

minutes <= 6'd0;

hours <= hours + 6'd1;

end

end

end

Endmodule

- 测试文件

`timescale 1ns/ 1ps

module Clocktime_tb() ;

reg clk;

reg rst_n;

wire[7:0] seg;

wire[3:0] digit;

wire [5:0] sec;

wire [5:0] min;

wire [5:0] hour;

wire clk_base1;

Clocktime u2(

.clk(clk),

.rst_n(rst_n),

.seg(seg),

.digit(digit),

.seconds(sec),

.minutes(min),

.hours(hour),

.clk_base1(clk_base1)

);

initial begin

clk=0 ;

rst_n=0 ;

#10 rst_n=1 ;

end

always #10 clk=~clk;

endmodule

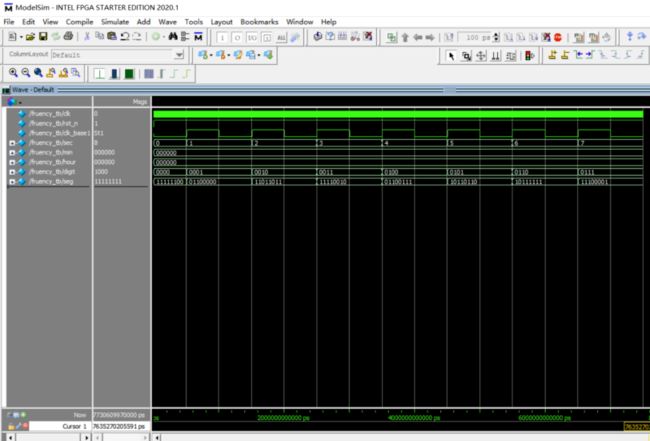

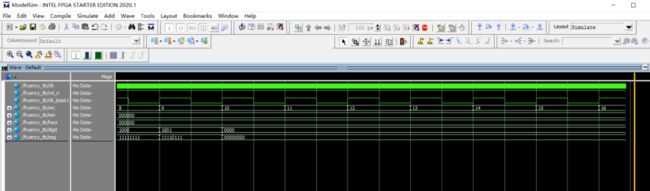

仿真截图: