【USTC】verilog 习题练习 11-15

11向量_续 1

题目描述

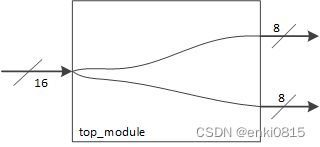

创建一 Verilog 模块,将 16bit 输入信号 in 分成两个 8bit 的信号 out_hi、out_lo,然后输出,如下图所示:

输入格式

输入信号 in, 位宽 16bit,类型为 wire。

输出格式

输出信号 out_hi,位宽 8bit,为输入信号的高 8 位。 输出信号 out_lo,位宽 8bit,为输入信号的低 8 位。

`default_nettype none // Disable implicit nets. Reduces some types of bugs.

module top_module(

input wire [15:0] in,

output wire [7:0] out_hi,

output wire [7:0] out_lo

);

// Write your code here

assign out_hi = in[15:7];

assign out_lo = in[7:0];

endmodule12 向量_续2

题目描述

一个32bit的向量信号包含有4个字节(bit[31:24]、bit[23:16]等),创建一个电路,用以调整4个字节的顺序,该电路经常用于在不同大小端系统之间进行数据交互:

AaaaaaaaBbbbbbbbCcccccccDddddddd => DdddddddCcccccccBbbbbbbbAaaaaaaa

提示:part-select操作即可以用于赋值语句的左侧也可用于右侧。

输入格式

1个 32bit 位宽的向量信号 in

输出格式

1个 32bit 位宽的向量信号 out

module top_module(

input [31:0] in,

output [31:0] out

);

// assign out[31:24] = ...;

assign out[31:24] = in[7:0];

assign out[23:16] = in[15:8];

assign out[15:8] = in[23:16];

assign out[7:0] = in[31:24];

endmodule13 位操作

题目描述

创建一个电路,包含两个 3bit 的输入信号 a 和 b,分别对 ab 进行按位或、逻辑或操作,以及将 ab 拼接成 6bit 信号后进行按位取反,如下图所示:

输入格式

a = 3'b101 b = 3'b000

输出格式

按位或:3'b101 逻辑或:1 拼接ab后再按位取反:6'b111010

module top_module(

input [2:0] a,

input [2:0] b,

output [2:0] out_or_bitwise,

output out_or_logical,

output [5:0] out_not,

output [5:0] out_not_1

);

// Write your code here

assign out_or_bitwise = a|b;

assign out_or_logical = a||b;

assign out_not_1 = {b,a};

assign out_not = ~out_not_1;

endmodule14 位操作

题目描述

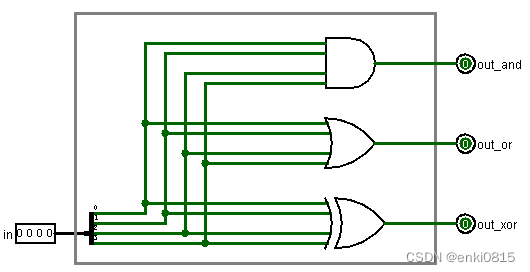

创建一个组合逻辑电路,包含4bit输入(in[3:0]),和3个输出,分别为:

-out_and:四输入与门的输出信号

-out_or:四输入或门的输出信号

-out_xor:四输出异或门的输出信号

电路结构如下图所示

输入格式

0 0 0 0

输出格式

0 0 0

module top_module(

input [3:0] in,

output out_and,

output out_or,

output out_xor

);

assign out_and = ∈

assign out_or = |in;

assign out_xor = ^in;

endmodule

15 向量拼接

题目描述

part_selection用于选择向量信号中的一部分,而向量拼接算子{a,b,c}用于将多个信号组合成一个位宽更大的向量信号,如:

{3'b111, 3'b000} 等同于 6'b111000

{1'b1, 1'b0, 3'b101} 等同于5'b10101

{4'ha, 4'd10} 等同于 8'b10101010 // 4'ha and 4'd10 are both 4'b1010 in binary

向量拼接时,每个信号都需要有明确的位宽,这样拼接后的信号才会有明确的位宽。例如,{1,2,3}就是非法的,因为无法确定各信号的位宽,语法检查时会报错。

向量拼接算子既可以用于赋值语句的左侧,也可用于右侧,如下所示:

input [15:0] in;

output [23:0] out;

assign {out[7:0], out[15:8]} = in;

assign out[15:0] = {in[7:0], in[15:8]};

assign out = {in[7:0], in[15:8]};

创建Verilog电路,将6个5bit位宽的输入信号,以及2bit的常量信号2’b11拼接成32bit的向量信号,并将其拆成4个8bit的信号,分别赋值给4个输出信号,如下图所示:

输入格式

6个5位宽的输入信号a,b,c,d,e,f

输出格式

4个8位宽的信号w,x,y,z

module top_module (

input [4:0] a, b, c, d, e, f,

output [7:0] w, x, y, z );

// assign { ... } = { ... };

assign w = {a[4:0],b[4:2]};

assign x = {b[1:0],c[4:0],d[4:4]};

assign y = {d[3:0],e[4:1]};

assign z = {e[0:0],f[4:0],2'b11};

endmodule