RT-Thread 27. UART设备

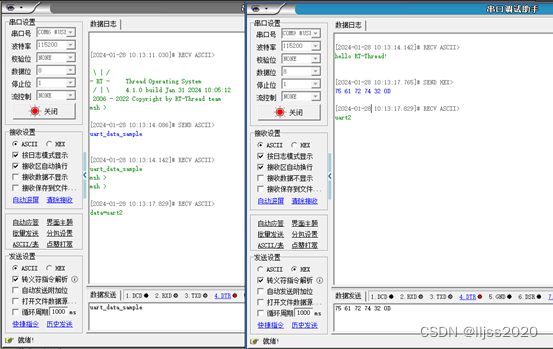

1.实现串口通信

这里实现uart0的485通信

MSH命令输入:uart_data_sample,开启线程执行。

输入一段字符串,以’\r’ (0x0D)结尾,回显输入的字符串

2. 代码

//rt_uart.c

#include //delay.c

#include "delay.h"

//

static uint32_t fac_us=72; //us延时倍乘数

//初始化延迟函数

//当使用ucos的时候,此函数会初始化ucos的时钟节拍

//SYSTICK的时钟固定为AHB时钟的1/8

//SYSCLK:系统时钟频率,MHz

void delay_init(uint8_t SYSCLK)

{

fac_us=SYSCLK;

}

//延时nus

//nus为要延时的us数.

//注意:nus的值不要大于1000us

void delay_us(uint32_t nus)

{

uint32_t ticks;

uint32_t told,tnow,tcnt=0;

uint32_t reload=SysTick->LOAD; //LOAD的值

ticks=nus*fac_us; //需要的节拍数

told=SysTick->VAL; //刚进入时的计数器值

while(1)

{

tnow=SysTick->VAL;

if(tnow!=told)

{

if(tnow<told)tcnt+=told-tnow; //这里注意一下SYSTICK是一个递减的计数器就可以了.

else tcnt+=reload-tnow+told;

told=tnow;

if(tcnt>=ticks)break; //时间超过/等于要延迟的时间,则退出.

}

}

}

#if 1

//延时nms

//nms:要延时的ms数

void delay_ms(uint16_t nms)

{

uint32_t i;

for(i=0; i<nms; i++) delay_us(1000);

}

#endif

//delay.h

#ifndef _DELAY_H

#define _DELAY_H

#include "gd32f3x0.h"

void delay_init(uint8_t SYSCLK);

void delay_ms(uint16_t nms);

void delay_us(uint32_t nus);

#endif

//drv_usart.c

/*

* Copyright (c) 2006-2021, RT-Thread Development Team

*

* SPDX-License-Identifier: Apache-2.0

*

* Change Logs:

* Date Author Notes

* 2021-06-21 RiceChen the first version

*/

#include //drv_usart.h

//增加tx_af,rx_af

/*

* Copyright (c) 2006-2021, RT-Thread Development Team

*

* SPDX-License-Identifier: Apache-2.0

*

* Change Logs:

* Date Author Notes

* 2021-06-20 RiceChen the first version

*/

#ifndef __DRV_USART_H__

#define __DRV_USART_H__

#include //drv_gpio.c

//增加GPIOE的存储位置,不然GPIOF会出错

/*

* Copyright (c) 2006-2021, RT-Thread Development Team

*

* SPDX-License-Identifier: Apache-2.0

*

* Change Logs:

* Date Author Notes

* 2021-06-20 RiceChen the first version

*/

#include //drv_gpio.h

/*

* Copyright (c) 2006-2021, RT-Thread Development Team

*

* SPDX-License-Identifier: Apache-2.0

*

* Change Logs:

* Date Author Notes

* 2021-06-20 RiceChen the first version

*/

#ifndef __DRV_GPIO_H__

#define __DRV_GPIO_H__

#include "gd32f3x0.h"

#include "gd32f3x0_exti.h"

#define __GD32_PORT(port) GPIO##port

#define GD32_PIN(index, port, pin) {index, RCU_GPIO##port, \

GPIO##port, GPIO_PIN_##pin, \

EXTI_SOURCE_GPIO##port, \

EXTI_SOURCE_PIN##pin}

#define GD32_PIN_DEFAULT {-1, (rcu_periph_enum)0, 0, 0, 0, 0}

#define GET_PIN(PORTx,PIN) (rt_base_t)((16 * ( ((rt_base_t)__GD32_PORT(PORTx) - (rt_base_t)GPIO_BASE)/(0x0400UL) )) + PIN)

struct pin_index

{

rt_int16_t index;

rcu_periph_enum clk;

rt_uint32_t gpio_periph;

rt_uint32_t pin;

rt_uint8_t port_src;

rt_uint8_t pin_src;

};

struct pin_irq_map

{

rt_uint16_t pinbit;

IRQn_Type irqno;

};

#endif

//board.c

/*

* Copyright (c) 2006-2021, RT-Thread Development Team

*

* SPDX-License-Identifier: Apache-2.0

*

* Change Logs:

* Date Author Notes

* 2009-01-05 Bernard first implementation

*/

#include