单片机学习笔记——特殊功能寄存器(SFR)_(上)

目录

片内RAM的特殊功能寄存器

F0H——寄存器B

单片机乘法原理

单片机除法原理

E0H——累加器ACC

ACC和A的区别和联系

寄存器和存储器的区别和联系

D0H——程序状态控制字PSW

B8H——中断优先级控制寄存器IP

A8H——中断允许寄存器IE

B0H——特殊功能寄存器P3

A0H——特殊功能寄存器P2

片内RAM的特殊功能寄存器

![]()

片内RAM一共有21个特殊功能寄存器

F0H——寄存器B

寄存器B称为辅助寄存器,是为乘法和除法指令而设置的,仅在乘法、除法指令中为寄存器寻址,在其它指令中为直接寻址

| 运算前 | 运算后 | |

| 寄存器B | 被乘数 | 结果的高8位 |

| 累加器ACC | 乘数 | 结果的低8位 |

单片机乘法原理

- 确定乘数和被乘数

- 将乘数和被乘数化为二进制

- 判断乘数是否为0,若为0,直接输出0

- 乘数不为0时,被乘数的二进制序列和乘数的二进制序列按位运算——被乘数遇到乘数某位为0时,按全零序列左移一位;遇到乘数某位为1时,被乘数整体左移一位——每次移位结果相加

- 直到乘数最高位为0时,停止计算并输出结果

(虽然在计算过程中,乘数和被乘数的先后顺序并不重要,但是在单片机的读出和写入过程中,由于其存储位置的不同,会有细微差别)

|

使用控制电路实现乘除法时,用B寄存器存放在运算过程中保持不变的被乘数和除数

- 乘法运算中,需要不断地将乘数右移,判断其最低位,如果为1,则加上被乘数,故乘数不变

- 在除法运算中,要将被除数减去除数,得到余数,然后再加上商和向左移,所以除数是不变的

| 运算前 | 运算后 | |

| 寄存器B | 除数 | 余数 |

| 累加器ACC | 被除数 | 商 |

单片机除法原理

- 确定除数和被除数

- 将除数和被除数化为二进制

- 判断除数是否为0,是的话,无法计算

- 除数不为0,被除数的二进制序列和除数的二进制序列按位运算——除数按位左移,被除数与除数按位相减,重复此操作,直到被除数小于除数时,得到商

- 被除数减去除数与商之积即为其余数(进行左移减法之后被除数剩下的部分就是余数)

|

E0H——累加器ACC

ACC——8位,一个操作数经暂存器2进入ALU(算数逻辑单元)的输入端,与另一个来自暂存器1的操作数进行运算,结果再送回ACC,在指令中,使用助记符A表示

Accumulator Register是应用最广泛的专用寄存器——用于存放8位数据,许多单操作数指令的操作数、双操作数指令的一个操作数取自累加器。加、减、乘、除算术运算指令的结果都存放在累加器A或寄存器B

ACC和A的区别和联系

A 和 ACC,是同一个特殊功能寄存器,但编程时,有两种写法:

【Practical】单片机中Acc与A的区别_push acc_Anova.YJ的博客-CSDN博客

- 写成 A(指令操作),是寄存器寻址,指令长度和周期都较短,为2字节1周期,A在汇编后则隐含在指令操作码中,在指令中默认是无地址的

- 写成 ACC(累加器位操作),是直接寻址,周期和长度都多用一个字节,3字节2周期——汇编后的机器码必有一个字节的操作数,是累加器的字节地址E0H,可出现在用直接寻址的任何地方

同样的,工作寄存器R0~R7在指令中写法不同,生成的机器码也不同,如:

前者属于寄存器寻址,后者属于存储器直接寻址

R0和00H的级别不同

- 00H只是RAM区的一个普通单元,其读写速度要比慢得多。微型计算机内部通常设置工作寄存器组,运算的结果可以放在寄存器中而不必每次都放到存储器里,可以提高机器的工作速度。其实寄存器也是一种存储器,只不过它是CPU中的部件,速度最快而已

寄存器和存储器的区别和联系

- 寄存器存在于CPU中,速度很快,数目有限;计算机运算时,必须先将数据读入寄存器

- 存储器就是内存,速度稍慢,但数量很大

寄存器用于存储二进制代码,由触发器而成,一个触发器可存储1位二进制代码,故存放n位二进制代码的寄存器,需用n个触发器来构成

按照功能的不同,可将寄存器分为

- 基本寄存器只能并行送入数据,也只能并行输出

- 移位寄存器中的数据可以在移位脉冲作用下依次逐位右移或左移,数据既可以并行输入、并行输出,也可以串行输入、串行输出,还可以并行输入、串行输出,或串行输入、并行输出,十分灵活,用途也很广

存储器单元实际上是时序逻辑电路的一种。按存储器的使用类型可分为只读存储器(ROM)和随机存取存储器(RAM),两者的功能有较大的区别,因此在描述上也有所不同

存储器是许多存储单元的集合,按单元号顺序排列。每个单元由若干二进制位构成,以表示存储单元中存放的数值

累加器ACC作寄存器时的主要作用:

1、存储临时的数据,比如做算术运算时候的临时结果

2、存放函数的返回值,比如WINDOWS 的API函数中,返回值一般都是放在累加器中的

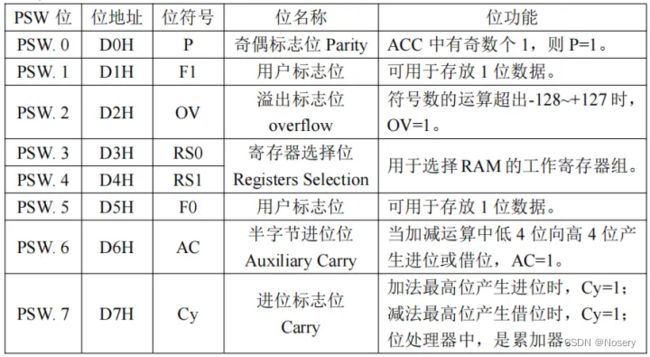

D0H——程序状态控制字PSW

Program State Word,存放着当前ALU的操作状态特征

注意以下几点

- 进位标志位CY(PSW.7),在指令中,使用C代替CY,如果要根据加减运算是否有仅为来决定程序的转移方向,则必须在运算前清零

- 用户标志位F0(PSW.5),可根据用户需求自定义作为软件标志

- 溢出标志位OV(PSW.2),符号数运算结果超出-128~+127时由硬件置1

- 保留位F1(PSW.1),89C51未使用,52用于用户标志位,和F0一样可自定义为软件标志

RS0(PSW.3) 和 RS1(PSW.4)决定当前使用哪个工作寄存器组

![]()

B8H——中断优先级控制寄存器IP

中断

6个中断请求信号;2种触发方式;6个中断标志;5个中断源;2级中断允许控制;2个优先级;1个中断向量表;4个相关寄存器。

对单片机来讲,中断是指CPU在处理某一事件A时,发生了另一事件B,请求CPU迅速处理(中断发生);CPU暂时停止当前工作(中断响应),转去处理事件B(中断服务);待CPU将事件B处理完毕后,再回到原来事件A被中断的地方继续处理事件A(中断返回),这一过程称之为中断

中断自然优先级 IP.0(PX0)最高,IP.7 最低,IP可进行位寻址,单片机复位时,各位全部清零——也就是说,复位之后所有的中断都处于低优先级,服务顺序按自然优先级

高优先级中断能够打断低优先级中断以形成中断嵌套,同级或低级对高级不能进行中断嵌套

优先级寄存器的各个位,如果置1——设为高优先级,如果置0——设为低优先级,同一优先级的排序仍按照自然优先级排序

置1操作方法

指令操作置1 MOV IP,#07H ;将各个中断按需置1,提高优先级

位操作置1 SETB PX0

(其中分号;用于汇编语言的注释)

若几个同级中断同时向CPU请求中断响应,在没有设置中断优先级情况下,按照默认自然中断优先级响应中断;在设置中断优先级后,则按设置的高低顺序的自然优先级顺序确定响应的先后顺序

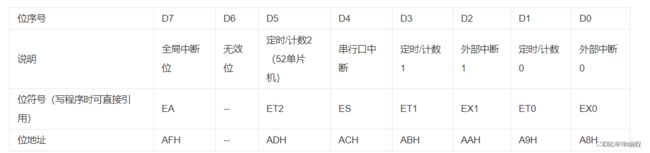

A8H——中断允许寄存器IE

必须先打开全局中断IE.8(EA),才能决定其他的中断请求是否能被响应

置1操作方法(允许定时计数器0(ET0)中断)

指令操作置1 MOV IE,#82H

位操作置1 SETB EA,SETB ET0 ;SETB EA用于CPU开全局中断

(ET2只有89C52里面有 )

B0H——特殊功能寄存器P3

P3口是6位双向口,既可以作为输入,也可以作为输出。从P3.0~P3.5两两一组,分别是串行口,外部中断口和定时器口,P3.6和P3.7分别是片外RAM的写读选通信号

p3的第二功能是中断,所以只要开中断就转化为第二功能,开中断用中断允许控制器IE,IE的地址是(A8H)把它的最高位置一,开总中断,然后你想用哪个中断就给那个中断置一

P3各线的第二功能

P3口是一个多功能端口,与P1,P2口的差别在于多了与非门和缓冲器。故使得P3口除了具有P1口的准双向I/O功能之外,还可以使用各引脚所具有的第二功能

与非门的作用实际上是一个开关,决定是输出锁存器上的数据还是输出第二功能的信号。WR和RD是第二输出功能引脚。当第二输出端为1时,输出Q端信号;当Q=1时,可输出第二输出端的信号。编程时,不必事先由软件设置P3口为通用I/O口还是第二功能

也就是直接对P3口做了一个操作,而没有使用它内部的特殊功能,比如没有使用过串口,也没有使用过外部中断,也没有使用过定时计数器的计数功能,也没有做外部扩展,这个时候没有对那些特殊功能做设置,这个输出功能线它就会是1,不需要来干预,这个是由指令和硬件配合来决定的,所以如果没有使用它的第二功能,这个线它肯定是1,这样的话外部引脚的电平就是仅由的内部总线来决定

A0H——特殊功能寄存器P2

P2口是8位输出口,只能作为输出使用,在P2口上可以连接LED、LCD等输出设备

P2口比P0口多了一个多路开关转换器,其输出端也不一样了——输出端是一个上拉电阻加一个非门。它也可作为普通的IO口和作为地址的高8位:当它作为普通的IO口时,控制端MUX为0,开关就打到下面和内部总线相连,一旦断开电平就会通过上拉电阻连接到VCC,外部引脚 P2.X 呈现的就是高电平;当内部电路写0时经过开关,非门端的场效应管就会导通,外部引脚 P2.X 就会呈现低电平

在使用输入功能的时候要先使内部总线先写1,否则经过输入通道读出外部电平的状态的时候就会读错,此时场效应管导通,无论是什么状态的电平,进来之后都只能读到是低电平,就会出错。(也就是说,如果使用之前写入的是0,Q是0,MUX控制开关打到0,经过非门,电平为1,场效应管导通,VCC经过一个电阻之后接地,外部引脚此时无论是什么情况,都不会连接到VCC的电路中,所以就是低电平——存在时钟信号的情况下,输出Q跟随输入D,即内部写0,输出端就为0)

为什么P2口使用输入功能的时候要在内部电路上写1

要先在内部总线上写1,目的就是使场效应管处于断开的状态,外部引脚的电平经过D端才能真正进去,当遇到外部高电平的时候,内部经过读引脚读进来的的电平才是1;外部遇到低电平的时候,内部总线上读进来才是0,这个时候读电平才不会出错

地址由P0口(低8位)和P2口(高8位)共同组成,P0分时复用,可作为地址的低8位,也可以作为8位数据的输出端;P2口则作为地址高8位的输出端