Vivado-DDS IP核配置

目录

Configuration

System Parameters

Hardware Parameters

Implementation

Detailed Implementation

DDS输出数据频率计算

想通过PG-141了解DDS Compiler IP核或者英语不好的朋友可以通过下面的链接进行学习,比机翻强无数倍

https://www.rstk.cn/news/1198370.html?action=onClick

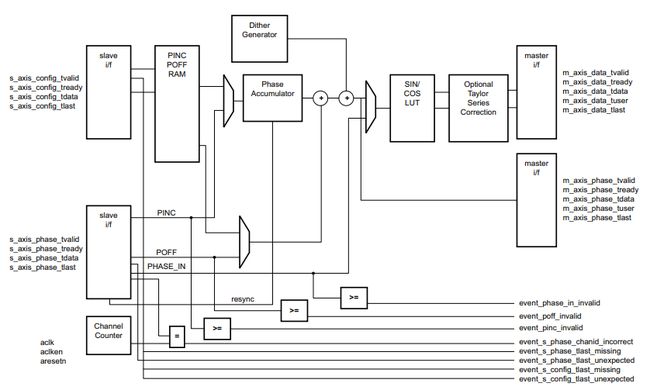

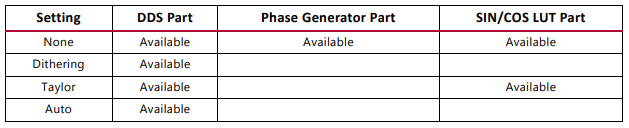

DDS Compiler——直接数字合成器,DDS 由一个相位发生器和一个 SIN / COS 查找表组成,这两个功能可以单独使用也可以一起使用。

DDS Core Architecture

关于DDS Compiler的功能不过多赘述,可通过官方文档PG141进行了解,下面将对DDS Compiler的配置进行说明。

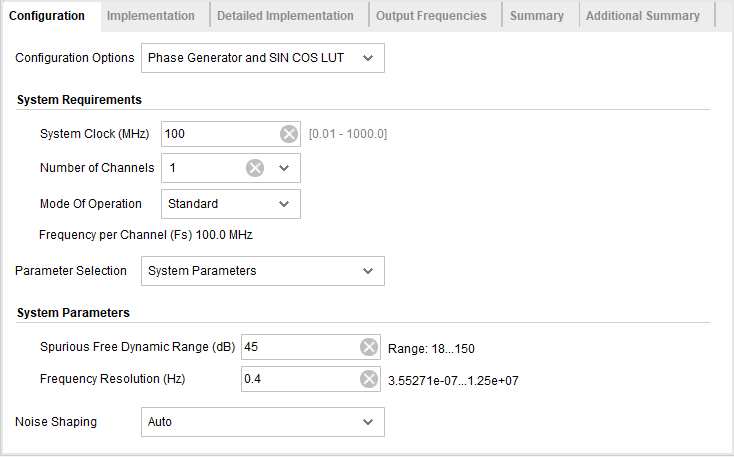

Configuration

Configuration界面

Configuration界面的Configuration Options可选择DDS Compiler的模式,有Phase Generator and SIN COS LUT模式、Phase Generator Only模式和SIN COS LUT Only模式。一般使用DDS Compiler作为测试信号生成器时选择Phase Generator and SIN COS LUT模式即可。

在System Requirements下的System Clock(MHz)中填写输入DDS Compiler aclk信号的系统时钟的频率;于Number of Channels中根据需求选择通道数(最多支持16个通道,通道是时分复用的);在Mode Of Operation中一般选择Standard模式,Rasterized(光栅)模式可以减少相位噪声。

在Parameter Selection 选择DDS Compiler将使用System Parameters(系统参数-频域参数)还是Hardware Parameters(硬件参数-时域参数);系统参数将可配置Spurious Free Dynamic Range (SFDR)、Frequency Resolution和Noise Shaping;硬件参数将可配置Noise Shaping、Phase Width和Output Width。通常选择System Parameters。

System Parameters

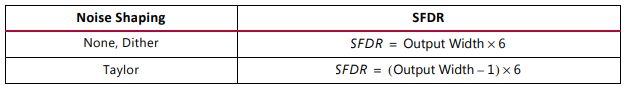

SFDR(无杂散动态范围)将决定DDS Compiler的数据输出宽度,其计算方式如下表所示

SFDR的计算公式

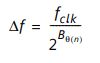

Frequency Resolution(频率分辨率)以Hz为单位,指定最小频率分辨率,影响Phase Width(相位宽度)和输出信号的频率,其计算方式如下所示

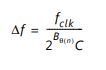

频率分辨率的计算公式

若DDS被时分复用以生成C个通道,则频率分辨率的计算方式应为

多通道下频率分辨率的计算公式

其计算值一般为不循环无限小数,填写时小数值越精确Phase Width的值越准确 (可能会出现小数值位数不够导致Phase Width的值有误差的情况,所以建议把计算得到的值全部填上而不是只取其中的几位)。设置Frequency Resolution后可以通过Summary中的Phase Width判断是否计算正确。

公式中fclk为aclk-System Clock的频率,Bθ(n)为相位宽度的值。推荐将Phase Width设为32以便进行Phase Increment和Phase Offset的控制。

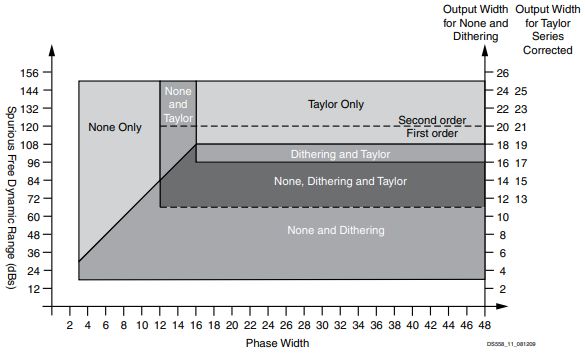

Noise Shaping(噪声整形)选择是否使用None(相位截断),Dithering(抖动)或Taylor Series Corrected(泰勒级数校正)。一般选择Auto,此选项将根据System Parameters(系统参数)自动确定Noise Shaping(噪声整形)的模式。

其取值域如下所示

噪声整形值域

Hardware Parameters

Phase Width(相位宽度),设置m_axis_phase_tdata中PHASE_OUT字段的宽度。

Output Width(输出宽度),仅当选择DDS或SIN/COS LUT部件时才启用,设置m_axis_data_tdata中SINE和COSINE字段的宽度。

Noise Shaping(噪声整形)选择是否使用None(相位截断),Dithering(抖动)或Taylor Series Corrected(泰勒级数校正)。

Hardware Parameters模式下噪声整形选项

Hardware Parameters模式需要手动设置Phase Angle Increment Values(二进制)和Phase Angle Offset Values(二进制),因使用较少故在此不过多赘述。

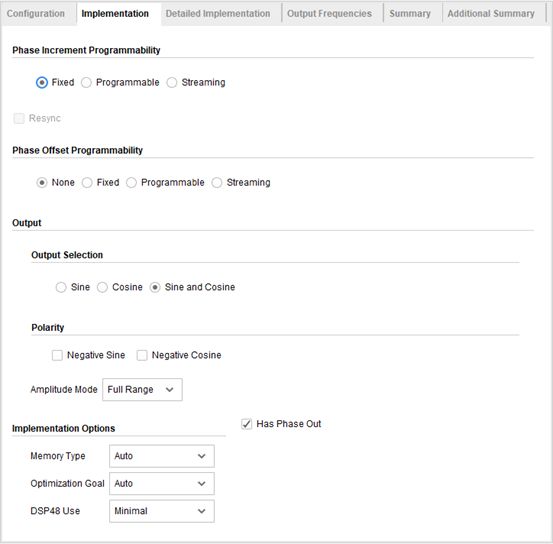

Implementation

Phase Increment Programmability(相位增量可编程性)和Phase Offset Programmability(相位偏移可编程性),这两个选项用来设置Phase Increment和Phase Offset值是否可以在运行时更改或者更改的方式。Fixed:表示该值在生成时固定,不能在运行时更改,使用的资源最少,选择时需要手动配置Output Frequencies或Phase Offset Angles;Programmable:表示在运行时可以通过CONFIG channel进行更改(选择时IP核将生成S_AXIS_CONFIG通道),建议在DDS频率需要在操作模式进行改变时选择此选项;Streaming:表示在运行时可以直接通过输入的PHASE channel进行更改(选择时IP核将生成S_AXIS_PHASE通道),建议在需要经常配置时选择此选项。None:只在Phase Offset Programmability中可选,表示不需要相位偏移功能。

若Phase Width的值为3-16时,若同时选择Programmable或Streaming时S_AXIS_CONFIG或S_AXIS_PHASE的tdata信号将变成32位(只有一个时为16位),低16位由Phase Increment和Unsed Bit组成,高16位由Phase Offset 和Unsed Bit组成。若Phase Width的值为17-32时,若同时选择Programmable或Streaming时S_AXIS_CONFIG或S_AXIS_PHASE的tdata信号将变成64位(只有一个时为32位),低32位由Phase Increment和Unsed Bit组成,高32位由Phase Offset 和Unsed Bit组成。若Phase Width的值为更高时以此类推即可。若使能Resync则还需占据额外的字段,具体细节建议阅读官方手册PG-141的Protocol Description,在此不过多赘述。

Output中的Output_Selection可选择DDS通过m_axis_data_tdata输出具有正交SINE和COSINE字段数据或仅输出这两个字段之一。Polarity可选择m_axis_data_tdata输出的的SINE和COSINE字段被反转。

Implementation Options中的选项默认即可,如非必要无需修改。

Detailed Implementation

AXI Channel Options用于配置AXI接口信号,选项默认即可,如非必要无需修改。在默认情况下Phase Increment和Phase Offset的配置只需要在输入数据时同时使能tvalid信号即可,便于操作,可简化配置流程。

Latency Options选择应通过Vivado IDE自动配置延迟还是手动配置延迟,推荐使用自动配置。

Has Phase Out: 选中时,DDS IP核将具有输出Phase的输出通道。

ACLKEN: 选中时,DDS IP核将具有一个aclken(高电平有效时钟使能)输入端口。

ARESETn: 选中时,DDS IP核将具有一个aresetn(低电平有效同步复位)输入端口。

DDS输出数据频率计算

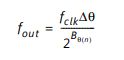

在标准模式下数据输出频率fout需要通过System Clock的频率fclk、相位宽度Bθ(n)和Phase Increment Δθ得出,公式如下所示

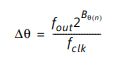

若要生成数据输出频率fout,则需要设置Phase Increment的值Δθ(根据对DDS IP核的配置有不同的方式如S_AXIS_CONFIG或S_AXIS_PHASE),其计算公式如下所示

在使用DDS Compiler IP时将Δθ作为输入给Phase Increment的配置端口即可(选择System Parameters模式的非Fixed的模式时为S_AXIS_CONFIG或S_AXIS_PHASE通道,选择Hardware Parameters模式时配置Phase Angle Increment Values)。