Quartus工程的qsf配置约束文件介绍

一、qsf文件概述

qsf:Quartus Setting File,是Quartus工程的配置文件;

包含一个Quartus工程的所有约束,包括工程的软件版本信息、FPGA器件信息、引脚约分配、引脚电平分配,编译约束和用于Classic TimingAnalyzer的时序约束;

二、文件配置格式

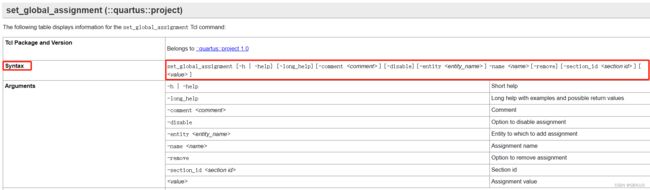

2.1 set_global_assignment--配置属性格式

语法:set_global_assignment

set_global_assignment [-h | -help] [-long_help] [-comment

note:这里,[]内的内容是可选的,被<>扩起来的就是必须填写的参数

新建空的工程时,Quartus软件根据配置自动生成的qsf文件有如下内容:

set_global_assignment -name FAMILY "Cyclone V"

set_global_assignment -name DEVICE 5CGXBC3B6U19C7

set_global_assignment -name TOP_LEVEL_ENTITY quartus_prj_demo

set_global_assignment -name ORIGINAL_QUARTUS_VERSION 18.1.0

set_global_assignment -name PROJECT_CREATION_TIME_DATE "21:43:09 FEBRUARY 07, 2024"

set_global_assignment -name LAST_QUARTUS_VERSION "18.1.0 Standard Edition"

set_global_assignment -name PROJECT_OUTPUT_DIRECTORY output_files

set_global_assignment -name MIN_CORE_JUNCTION_TEMP 0

set_global_assignment -name MAX_CORE_JUNCTION_TEMP 85

set_global_assignment -name ERROR_CHECK_FREQUENCY_DIVISOR 256

set_global_assignment -name EDA_SIMULATION_TOOL "ModelSim (Verilog)"

set_global_assignment -name EDA_TIME_SCALE "1 ps" -section_id eda_simulation

set_global_assignment -name EDA_OUTPUT_DATA_FORMAT "VERILOG HDL" -section_id eda_simulation

只需看懂意思即可:由上图可以知道

- FPA器件的系列与具体型号:FAMILY与DEVICE

- 顶层实体名称:TOP_LEVEL_ENTITY

- Quartus软件版本:创建工程时的Quartus版本与最终打开的Quartus版本:ORIGINAL_QUARTUS_VERSION 和LAST_QUARTUS_VERSION

- 创建工程的时间:PROJECT_CREATION_TIME_DATE

- 工程输出路径:PROJECT_OUTPUT_DIRECTORY

- 最小与最大核心半导体核心节点温度:MIN_CORE_JUNCTION_TEMP与MAX_CORE_JUNCTION_TEMP

- EDA仿真软件:EDA_SIMULATION_TOOL

- EDA仿真时间单位:EDA_TIME_SCALE

- EDA输出数据格式:EDA_OUTPUT_DATA_FORMAT

- CRC校验时钟频率:ERROR_CHECK_FREQUENCY_DIVISOR

Specifies the divide value of the internal clock, which determines the frequency of the CRC. The divide value must be a power of two(分频值为2的幂次). Refer to the device handbook to find the frequency of the internal clock for the selected device.

其他部分有:

set_global_assignment -name PRESERVE_UNUSED_XCVR_CHANNEL ON

set_global_assignment -name MESSAGE_DISABLE 332157

set_global_assignment -name MESSAGE_DISABLE 113015

set_global_assignment -name POWER_PRESET_COOLING_SOLUTION "23 MM HEAT SINK WITH 200 LFPM AIRFLOW"

set_global_assignment -name POWER_BOARD_THERMAL_MODEL "NONE (CONSERVATIVE)"

set_global_assignment -name ENABLE_SIGNALTAP ONset_global_assignment -name PROJECT_IP_REGENERATION_POLICY NEVER_REGENERATE_IP

set_global_assignment -name USE_SIGNALTAP_FILE output_files/stp1.stpset_global_assignment -name SIGNALTAP_FILE output_files/stp1.stp

set_global_assignment -name QSYS_FILE ../rtl/aux_mux.qsys

set_global_assignment -name IP_FILE ../rtl/ip/aux_mux_vid_clk.ip

set_global_assignment -name VERILOG_FILE ../rtl/temp_sensor.v

set_global_assignment -name MIF_FILE pll.mif

set_global_assignment -name SDC_FILE ../rtl/user_constr.sdc

set_global_assignment -name SYSTEMVERILOG_FILE ../rtl/xcvr_reconfig_arbiter.sv

set_global_assignment -name TCL_SCRIPT_FILE ../tcl/Pin_Location.tcl

2.2 set_location_assignment--配置管脚格式

语法:set_location_assignment

set_location_assignment [-h | -help] [-long_help] [-comment

qsf文件中的引脚分配举例:

set_location_assignment PIN_AB1 -to global_resetn

set_location_assignment PIN_AB2 -to hdmi_rx[0]set_location_assignment PIN_AB3 -to "hdmi_rx[0](n)"

注释:

- 普通的引脚分配,设置一个全局reset引脚,低电平有效

- hdmi_rx[0]与hdmi_rx[0](n)分别是一对hdmi差分对接收端的p网络和n网络

- 有空格或者或者括号(n)这种网络,需要加双引号

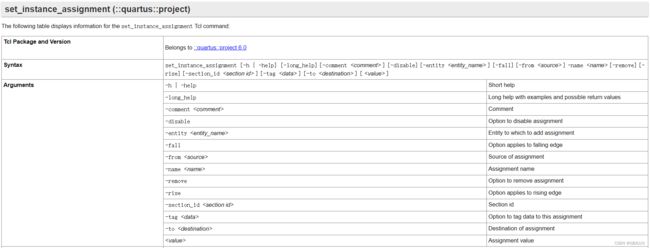

2.3 set_instance_assignment

语法:set_instance_assignment

set_instance_assignment [-h | -help] [-long_help] [-comment

qsf文件中的实例分配举例:

set_instance_assignment -name IO_STANDARD LVDS -to refclk_135m_p

或者:

set_instance_assignment -name IO_STANDARD LVDS -to refclk_100m_p -entity top_instance

注释:

- 设置差分时钟P网络为LVDS电平标准

- Quartus中指定差分网路电平标准时,只需要指明P网络的电平标准即可,N网络默认同P网络的电平标准

- 这里还给差分时钟网络refclk_100m_p指定了顶层模块名

三、应用场景

3.1 普通IO引脚

set_location_assignment PIN_AB1 -to led_0

set_instance_assignment -name IO_STANDARD "1.8 V" -to led_0

3.2 低速IO引脚

set_location_assignment PIN_AB1 -to hdmi_scl

set_instance_assignment -name IO_STANDARD "1.8 V" -to hdmi_scl

set_instance_assignment -name SLEW_RATE 0 -to hdmi_scl -entity top_instance

set_instance_assignment -name CURRENT_STRENGTH_NEW 2MA -to hdmi_scl -entity top_instance

3.3 差分时钟约束

set_location_assignment PIN_AB1 -to refclk_100m_p

set_location_assignment PIN_AB2 -to "refclk_100m_p(n)"

set_instance_assignment -name IO_STANDARD LVDS -to refclk_100m_p

或者:

set_instance_assignment -name IO_STANDARD LVDS -to refclk_100m_p -entity top_instance

偶尔也有:

set_instance_assignment -name INPUT_TERMINATION DIFFERENTIAL -to refclk_100m_p

3.4 高速差分对tx

set_location_assignment PIN_AB1 -to hdmi_tx[0]

set_location_assignment PIN_AB2 -to "hdmi_tx[0](n)"

set_instance_assignment -name IO_STANDARD "HIGH SPEED DIFFERENTIAL I/O" -to hdmi_tx[0] -entity top_instance

3.5 高速差分对rx

set_location_assignment PIN_AB0 -to dp_rx_p[0]

set_location_assignment PIN_AB1 -to dp_rx_p[0]

set_instance_assignment -name XCVR_VCCR_VCCT_VOLTAGE 1_0V -to dp_rx_p[0]

set_instance_assignment -name IO_STANDARD "HIGH SPEED DIFFERENTIAL I/O" -to dp_rx_p[0]

如下这种只有P脚,没有N脚的差分对还没看懂,待后续分析:

set_location_assignment PIN_AB1 -to hdmi_rx_p

set_instance_assignment -name IO_STANDARD "HIGH SPEED DIFFERENTIAL I/O" -to hdmi_rx_p -entity top_instance -disable

set_instance_assignment -name XCVR_VCCR_VCCT_VOLTAGE 1_0V -to hdmi_rx_p -entity top_instance -disable

set_instance_assignment -name XCVR_A10_RX_EQ_DC_GAIN_TRIM NO_DC_GAIN -to hdmi_rx_p -entity top_instance -disable

set_instance_assignment -name XCVR_A10_RX_ONE_STAGE_ENABLE NON_S1_MODE -to hdmi_rx_p -entity top_instance -disable

set_instance_assignment -name XCVR_A10_RX_ADP_VGA_SEL RADP_VGA_SEL_4 -to hdmi_rx_p -entity top_instance -disable

set_instance_assignment -name XCVR_A10_RX_LINK SR -to hdmi_rx_p -entity top_instance -disable

四、Quartus导入导出qsf文件

4.1 导入qsf文件方法

Assignments 》 Import Assignments,单击添加qsf文件(该qsf文件可以是其他工程里面的),再OK即可。

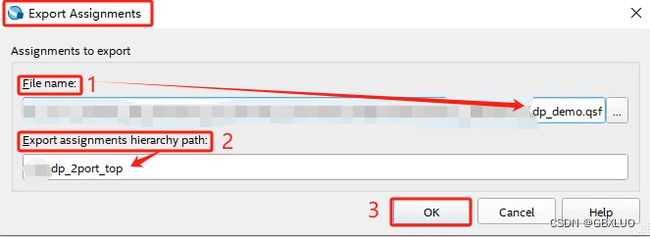

4.2 导出qsf文件方法

Assignments 》 Export Assignments,无特别要求,默认即可。