ModelSim入门

verilog设计进阶

时间:2014年5月5日星期一

主要收获:

1. 安装了ModelSim ALTERA 6.4a;

2. 熟悉基本流程,仿真成功;

3. 了解testbench语法基本。

为什么要学ModelSim……

1. Modelsim是专业的HDL语言仿真器,比 Quartus自带的仿真器功能强大的多.

2. Quartus simulator不支持Testbench ,只支持波形文件.vwf。vwf文件全称是矢量波形文件(Vector Waveform File),是Quartus II中仿真输入、计算、输出数据的载体。一般设计者建立波形文件时,需要自行建立复位、时钟信号以及控制和输入数据、输出数据信号等。其中工作量最大的就是输入数据的波形录入。比如要仿真仅1KB的串行输入数据量,则手工输入信号的波形要画8000个周期,不仅费时费力而且容易出错。

安装遇到的问题……

由于笔记本是win8系统,安装的是ModelSim ALTERA 6.4a,破解之后仍然打不开。解决的方法是……以管理员的身份打开。

可综合的比较器:

module compare(a, b, equal);

input a;

input b;

output equal;

assign equal = (a==b)?1:0;

endmodule

测试模块:

`timescale 1ns/1ns

module compare_test;

reg a,b;

wire equal;

initial begin

a=0;b=0;

#100 a=0;b=1;

#100 a=1;b=0;

#100 a=1;b=1;

#100 $stop;

end

compare u1(a, b, equal);

endmodule

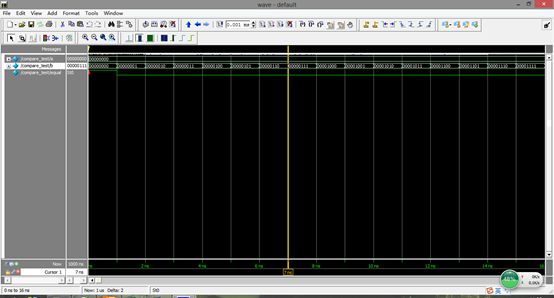

仿真波形:

练习:

设计一个字节(8位)比较器。

要求:比较两个字节的大小,如a[7:0]大于b[7:0]输出高电平,否则输出低电平,改写测试模型,使其能进行比较全面的测试。

思考:

第一次接触testbench文件,所以有很多问题。比较困难的就是"全面的测试",需要对a和b进行所有情况的测试。分析a和b的数值都是在0~255之间,则可以对b每1ns进行一次自增,对a每256ns进行一次自增,即可实现对a和b所有情况的比较。

测试文件:

`timescale 1ns/1ns

module compare_test;

reg[7:0] a,b;

wire equal;

initial begin

a[7:0]=0;b[7:0]=0;

#100 a[7:0]=8'b0000_0001; b[7:0]=8'b0000_0010;

#100 a[7:0]=8'b0000_0010; b[7:0]=8'b0000_0010;

#100 a[7:0]=8'b1000_0001; b[7:0]=8'b0000_0010;

#100 a[7:0]=8'b1000_0001; b[7:0]=8'b1000_0001;

#100 a[7:0]=8'b1111_0001; b[7:0]=8'b1111_0001;

end

always #1 b[7:0]<=b[7:0]+1;

always #256 a[7:0]<=a[7:0]+1;

compare u1(a[7:0], b[7:0], equal);

endmodule

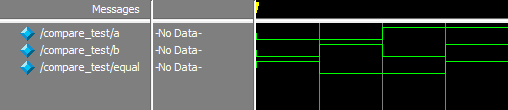

仿真波形图: