基于TI C64X DSP高清视频编、解码器软硬件技术概要

1 技术参数一览

|

|

Items

|

Encoder

|

Decoder

|

备注

|

|

硬件参数

|

CPU

|

TMS320DM642(720MHz)

|

兼容C64X

|

|

|

视频D/A(A/D)

|

ADV7401(74.25MHz)

|

ADV7393(74.25MHz)

|

ADI公司

|

|

|

音频D/A(A/D)

|

PCM1808(48KHz)

|

PCM1807(48KHz)

|

TI公司

|

|

|

FLASH

|

4M Nor Flash

|

--

|

||

|

SDRAM

|

32M(133MHz)

|

--

|

||

|

ISRAM

|

256KB

|

128K Cache2

|

||

|

EMAC

|

10/100Mbps

|

支持以太网

|

||

|

软件参数

|

视频算法

|

XviD 1.1.0

|

符合MPEG-4

|

|

|

支持分辨率

|

4:3(800x600, 1024x768)

16:9(720p)

16:10(1280x800)

|

可向上、下

兼容

|

||

|

帧率

|

24f/s以上

|

1024x768及更低分辨率能达到30f/s

|

||

|

码率

|

6.144Mbps左右

|

--

|

||

|

视频质量

(量化步长)

|

4~14

|

允许范围:

4~31

|

||

|

开发环境

|

IDE版本

|

CCS3.1/CCS3.3

|

--

|

|

|

Flash Burn版本

|

V 2.8

|

--

|

||

|

JTAG仿真器

|

SEED-XDS560PLUS

|

--

|

||

|

NDK版本

|

V 1.71

|

--

|

||

|

DDK版本

|

V 1.11

|

--

|

||

|

基本功能

|

采集

|

视频:ADV7401输入为VGA-RGB,输出为YUV4:2:2

音频:PCM1808输入为双声道模拟信号,输出为16bit PCM

|

||

|

压缩

|

视频:XviD编码器的输入为YUV4:2:0,输出为MPEG-4

音频:PCM或MP3

|

|||

|

传输

|

采用UDP组播经以太网传输

|

|||

|

解压缩

|

视频:XviD解码器的输入为MPEG-4,输出为YV12

音频:PCM或MP3

|

|||

|

显示

|

视频:ADV7393输入为YUV4:2:2,输出为RGB

音频:PCM1807输入为PCM,输出为左右模拟声道

|

|||

|

扩展功能

|

视频边界自动调整

|

第一次开机自动调整,相当于显示器的Autoset功能

|

||

|

视频割裂复原

|

防止视频在强干扰的情况下出现上下屏割裂现象

|

|||

|

动态IP

配置

|

支持运行过程中动态配置编、解码设备的IP地址

|

|||

|

音量调节

|

可随时调整PCM1807侧输出的音量

|

|||

说明:1)本设计为TMS320DM642 Only解决方案,另支持TMS320DM642 + PCI Host方案,在第二种方案中网络传输功能在PCI Host中实现。

2)支持与编码器完全配套的采用DirectShow开发的PC机解码客户端。

3)编解码器的软件部分与硬件部分相对独立,除线性汇编部分(.sa)要求支持C64X VLIW指令集以及EDMA指令,其它均为标准的C程序。

4)本文档所列技术参数在无特殊说明的情况下均指分辨率为720p(1280x720)时的指标。

2 系统架构

2.1 编码器

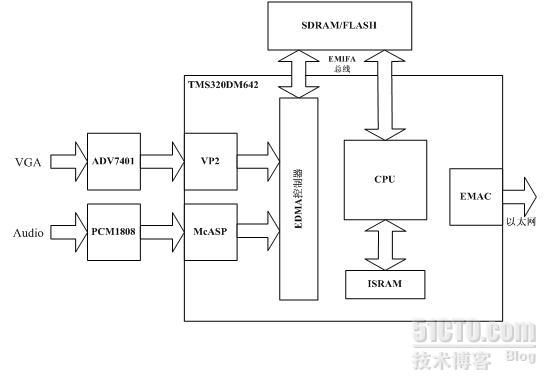

如图2.1所示为编码器的系统结构图。

图

2.1 编码器系统结构图

视频源前端为VGA接口,经ADV7401视频采集芯片将RGB模拟信号转化成YUV4:2:2的数字信号,TMS320DM642的视频口VP2将采集到的YUV数据由EDMA(Enhanced Direct Memory Access)通道拷贝到SDRAM的存储单元。CPU从SDRAM中读取采集到的YUV数据转换成YUV4:2:0格式后进行XviD压缩编码并将编码后的码流回写到SDRAM中。前端音频源为双通道音频接口,通过PCM1808音频采集芯片,将模拟音频信号转换成PCM(Pulse Code Modulation)格式的数字音频信号,并以左对齐I

2S格式送入TMS320DM642的多通道音频串口McASP。McASP接口将采集到的音频数据经EDMA通道拷贝到SDRAM中的存储单元。CPU读取SDRAM中采集到的音频数据进行处理并将结果回写到SDRAM中。经压缩处理后音视频码流再经以太网(10/100Mbps)以组播的形式发送到网络客户端。

2.2 解码器

如图2.2所示为解码器的系统结构图。

图

2.2 解码器系统结构图

CPU获取从以太网接口接收的视频码流数据并解码为YV12格式的YUV数据,进一步转换为YUV4:2:2格式后由VP2以60f/s的速率输出。输出的YUV4:2:2数据经视频分配器(Splitter)发送到多个视频接收器,再由视频接收器中的ADV7393转换成RGB格式送至显示器。解码后得到的PCM音频数据通过VP2通道随视频信号一同输出到视频分配器,再由视频接收器中的PCM1807转换成模拟信号送至音频功放。当然,也可以去掉视频分配器和视频接收器,将VP2端口输出的音、视频信号直接与PCM1807和ADV7393相连。

3 软件特性

3.1 软件接口

l 编码器

intMPEG4_encode( Encoder *enc_handle,

FVID_Frame *capFrameBuf,

unsigned char *outbuf );

l 解码器

int MPEG4_decode ( unsigned char *istream,

FVID_Frame *disFrameBuf,

int istream_size );

3.2 XviD简介

XviD是第二代MPEG-4视频编码内核中可选模式最多编码速度最快的视频编码,其各种算法的设计都具有代表性的先进意义。其编码功能模块的划分如图3.1所示。

图

3.1 编码器功能模块划分

3.3 XviD优化

本设计中综合运用了项目级优化、程序级优化、EDMA优化、存储结构优化和线性汇编优化。在此,只对程序级优化和线性汇编优化进行简要说明。

3.3.1程序级优化

考虑到实用性,本设计在XviD源码的基础上进行了如下删减和改进:

1)去掉B帧编码;

2)去掉半像素插值;

3)采用h.263量化、去掉MPEG-4量化;

4)去掉GMC编码;

5)去掉AC高级预测;

5)sad值计算、钻石搜索等函数进行了改进。

3.3.2线性汇编优化

本设计性能优化的大部分工作集中在线性汇编的改写上,部分关键代码改写成线性汇编后性能对比如表3.1所示(解码器的优化性能在此没有列出)。

表3.1 线性汇编性能对比

|

函数

|

优化前(时钟周期)

|

优化后(时钟周期)

|

|

fdct()

|

2536

|

600

|

|

idct()

|

10040

|

1224

|

|

quant_h263_inter()

|

4000

|

528

|

|

dequant_h263_inter()

|

4700

|

616

|

|

quant_dequant_h263_intra()

|

6372

|

688

|

|

sad16v()

|

224

|

80

|

|

transfer_16to8add()

|

1088

|

340

|

|

transfer_16to8copy()

|

640

|

200

|

|

transfer_8to16sub_s()

|

880

|

584

|

4 应用与演示

4.1 Encoder模块

如图4.1所示为编码器实物图,该编码器完成视频的采集、压缩和网络传输。视频和音频输入信号以及网络输出信号均连接到背板插口。

图

4.1 编码器实物图

4.2 Decoder模块

如图4.2所示为解码器实物图,该解码器完成视频网络接收、解压缩和视频输出。模块左侧集成了一个视频分配器(Splitter)。该视频分配器采用FPGA实现,它将DSP解压缩后的YUV4:2:2格式的视频信号发送到两个千兆以太网口(对应车厢左右两侧)。

图4.2 解码器实物图

4.3 地铁PIS视频系统

如图4.3所示为用Encoder和Decoder模块搭建的地铁PIS(Passenger Information System)视频系统的拓扑图。该系统用于列车动态地图显示、报站广播、司机乘客对讲、播放广告等。目前已成功应用于深圳地铁2号北段延长线、广州3号线、台北地铁线、沙特麦加地铁线和新加坡地铁线。

图

4.3 PIS系统拓扑图

4.4 效果演示

4.4.1 DSP Encoder + PC Decoder

在实验室环境下搭建的DSP Encoder + PC Decoder的系统如图4.4所示。

图

4.4 DSP Encoder + PC Decoder

图中左侧的便携式PC机的音频输出和VGA输出分别为Encoder模块的音频和视频输入。中间为一个Encoder模块和一个Switch模块以及一个5V的开关电源模块,三者插在一块背板上,模拟音频信号和视频信号由背板引入。右侧为一个PC Decoder,PC机的以太网口与Switch模块的以太网口相连。PC机解码客户端软件接收来自Encoder发送的码流数据并解码播放。PC机解码客户端显示效果如图4.5所示。

图

4.5 客户端显示效果

在此,便携式PC机分辨率设为1280×720,选用的播放文件为《冰河世纪II》高清视频文件。客户端PC机分辨率设为1280×960,图4.5中LCD屏显示的1280×720大小的中间区域(红色方框内)即为Encoder压缩后的视频码流的解码图像。

4.4.2 DSP Encoder + DSP Decoder

实际应用中搭建的DSP Encoder + DSP Decoder系统如图4.6所示。

图

4.6 DSP Encoder + DSP Decoder

图中左侧为安放在列车车头的标准U3机箱,内部集成有DSP Encoder、Media Player和Switch等模块。压缩后的视频数据流经Switch模块由百兆以太网线(图中绿色)传输到右侧的U3机箱。右侧的U3机箱安放在列车车厢位置,内部集成有DSP Decoder和Switch模块,它将接收到的视频码流解码后由千兆以太网线(图中黄色)传输到视频接收端并显示。