Make PCB Lirary PCB设计总结I

第一次由已绘制好的原理图来进行PCB绘制,低水平、经验的总结,不够供TA人参考。

需求:原理图已经绘制,并已经导入PCB(A.PCB)内,线已经布了一部分。需要从新根据原理图来绘制PCB。

1 Make PCB Library

如果将原理图直接导进PCB环境内,会发现很多的元件对应不了其封装(很多元件的封装可能是设计者自己绘制的,在Miscellaneous Devices.IntLib和MiscellaneousConnectors.IntLib中找不到其封装)而导不进PCB环境内。这个时候可以将设计者A.PCB中封装生成对应的.PcbLib文件:将界面切换到A.PCB界面 >> Design >> Make PCB Library。此时AD软件就会在当前工程下生成一个Libraries文件夹,其内包含一个PCB Library Documents文件夹,对应的A.PcbLib就在这个文件下。在A.PcbLib界面下,点击Projects下的PCB Library就可以看到A.PcbLib封装库里的各封装列表:

点击Projects则可重新回到工程视图。PCB封装库包含在工程下时,这个库可不用安装,此时各元件也能自动就对应到自己的封装。可以将原理图(对应封装)导进PCB环境中了。如果没有对应到其封装,那么就选中元件 >> 右键 >> 属性(或双击元件) >> 模型 >>添加去浏览元件对应的封装。如果某各元件的数量较多时,可以用批量添加封装的方法。

2 编译原理图

在导入PCB环境之前应该利用AD内嵌的工具检查一下原理图是否有“floating net label(Net Label 没有放到Wire上)”等问题。在确保原理图符合设定规则的前提下导入PCB环境中。导入PCB环境的步骤为:在PCB工程下新建一个PCB文件,将AD的显示界面切换到PCB文件下,Design >> Import Changes from *.ProPcb。

3 PCB设计

(1) 设定PCB的规格

PCB规格是根据实际的加工要求或者制作PCB板子公司的实际工艺水平来设置的。比如某个PCB制造商的最高工艺水平可以让线间距最小为0.254mm,那我们就可以在PCB的规格中设置线间距不小于为0.254mm的值。第一次绘制PCB时,我们只关心了PCB板的线 -- 线距离、线– 孔距离及线宽度三种规格。设置这些规格的步骤为:

将AD界面切换到PCB文件,Design >> Rules。在弹出的PCB Rules and Constraints Editor(PCB规格约束编辑器)中,

- 在Electrical下选择Clearance(间隙),将其Attributes设置为6mil(要确保制造商有这个工艺水平),这就设置了线 – 孔间的间隙。使能检查PCB中线路的短路(ShortCircuit)及断路(Un-Routed Net)情况。

- 在Routing下选择Width设置布线的最小和最大宽度。电源线一般会比地线的宽度宽,地线宽度会比一般的连接线宽,所以需要设置线宽的范围。可以在Width的Attributes属性下选择默认的布线宽度。

- 在Routing下选择RoutingVias设置过孔的大小范围。设置Manufacturing下HoleSize的范围。

- …….

在允许检查(PCB环境下快捷键L后勾选DRC Error Makers)这些规格的情况下,在PCB设计过程中违反了这些规格时就会有提示或者颜色标注。

(2) 绘制板框

板框的大小决定布局的空间。在进行PCB布局之前一定要明确板框的大小,否则后来的板框尺寸变更可能会影响布局(尤其是布线之后)。绘制板框的步骤为:

- 获取板框的大小并计算四角上的孔位置。

- 在PCB文件中用“Place>> Line”(快捷键 P + L)来绘制板框。

- 将所有的元件放入板框中后,若只是想PCB文件显示板子那么大的空间,则选中四条边框 >> Design >> Board Sharp >> Define From Selected Objects。

(3) 布局

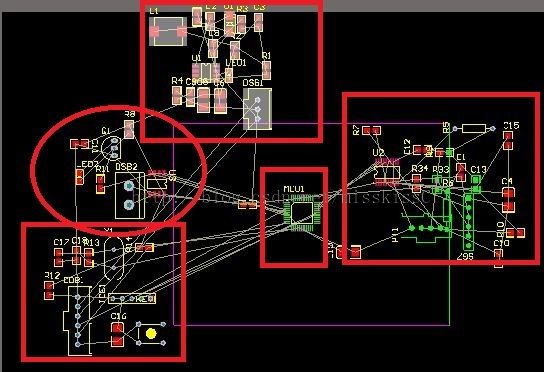

布局是PCB设计的一个关键步骤。所花的时间应该是最多的。在布局时至少要保证能够成功布完线。元件较少时可以采用在原理图中选中所有器件>> 切换到PCB文件中(PCB的封装也被对应的选中) >> Tools >> Component Placement >>Reposition Selected Components来布局。但如果元件较多时,这个办法对于像我这样对电路还一窍不通的人来说未免就是一个好办法。

经历过一次布局后,我觉得与原理图对应,模块化的拖封装到PCB板框的方法比较科学(对目前的我来说):

- 布局时一定要优先考虑,是否能够成功布完线。

- 可根据各个模块与主控芯片连接的方向将图分为几个模块。除了与主控芯片相连的引脚外,各个模块都是内部连接关系。首先考虑各个模块与主控芯片的方便连接。

- 一般来说,各模块之间除了电源和地之外没有连接关系。避开电源和地连接的飞线的干扰,同时也适当考虑各个模块之间电源和地之间连接的方便性(电源一般是绕一圈,让各个模块都能够得到电源,地可用覆铜的方式连接)。同时考虑特殊元件的位置(如USB,晶振,排针)。

- 再在各个模块内协调各个封装(元件)的布局,可以根据电路连接方式来布局,适当考虑相同器件的对齐。

- 适当考虑整体PCB布局的简洁与大方性。

(4) 布线

如果布局完美,那么布线就不在话下了(对于一两层的板子,最多打孔进行布线)。同时根据设置的规格让电源线宽 > 地线宽 > 一般线宽。

(5) 覆铜

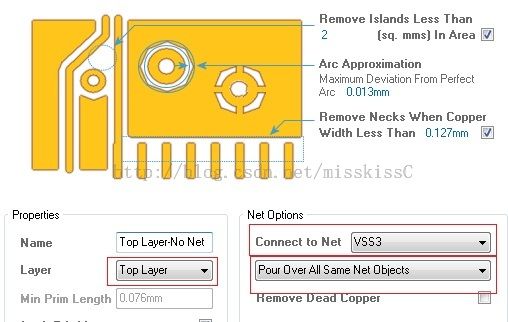

在初步觉得布线也完成了的情况下,可以用覆铜的方式来连接公共地,这会给PCB设计省下许多布局和布线的开销。布铜时就会体会到“网络标号”的好处了,点击Place Polygon Plane快捷图标:

首先选择在那一层覆铜,上图为Top Layer。然后选择在Top Layer层连接到哪一个网络标号上(在这里地的网络标号被设置成VSS3,凡是具有相同网络标号VSS3的地方就会被连接起来,点击确定后,用鼠标选定覆铜范围,范围选定后右键开始在选定范围覆铜。覆铜后,可局部放大观察效果,在其它线或者引脚周围是没有被覆铜的。

覆铜后不能在含覆铜的地方连线,如果还有连线的必要就先删掉覆铜(在覆铜显示的情况下,快捷键为E + D,然后用鼠标左击一下有覆铜的地方。隐藏显示覆铜,快捷键L >> Show/Hide >> Polygons >> Hidden)。一般是在进行规格检查后,发现有的地方还没有连线,此时应该将覆铜删除,然后连线,再覆铜。

(6) 规格检查

PCB初步完成后,需要用设定的规则检查一下确定还有没有问题(比如有的引脚间还没有连线)。切换到PCB文件下,Tools >> Design Rule Check,确定检查项及输出项后点击左下角的RunDesign Rule Check。对于对话框中的选项,第一次看到可能会比较陌生,但我们应该尝试着去阅读这些项,并弄逐步去弄懂它们的含义。再者,PCB的规格检查不像C语言编译器,PCB的规格检查是检查PCB设计是否符合(1)中设定的规格,如果不符合给出一个警告。但这个警告到底会不会影响PCB的制作是不一定的,但为了安全起见,最好还是将PCB设计成符合设定PCB规格的模型(如果设定的PCB规格就是最高工艺标准呢)。

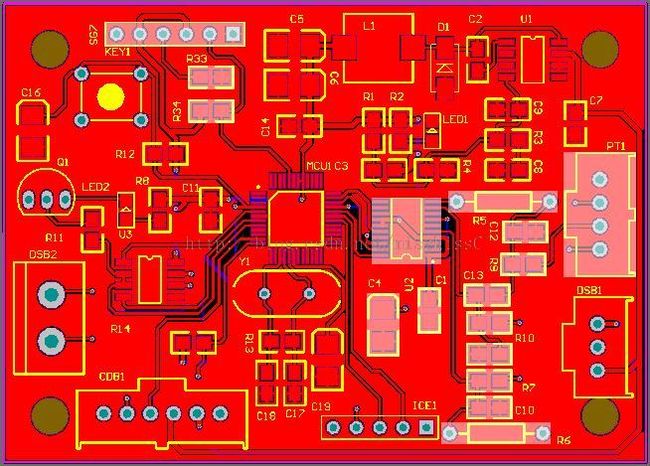

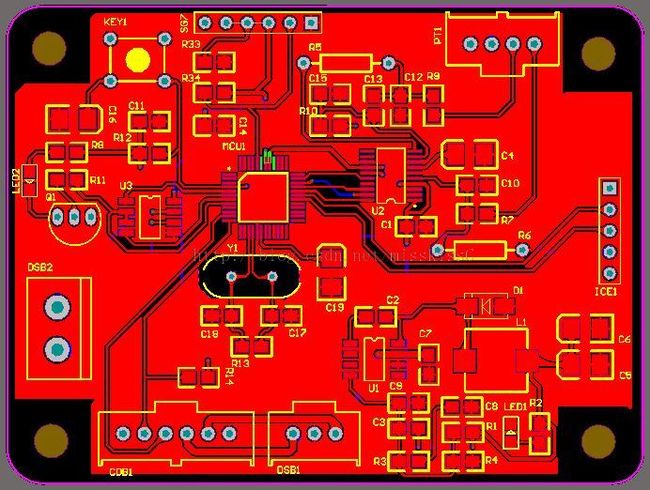

(7) PCB_V0.1

第一次进行PCB设计。对这个板子的设计并不满意,因为在PCB设计的过程中心里老是没底,不知道元件对应的封装到底对不对,也不知道布局时各器件是否有什么特殊讲究,也心虚布线时哪里没有布对。现在这块板子还没有拿出去加工制作。估计是要多碰几鼻子灰才能正常加工,因为我资质低于一般人之下,要是一次性成功我倒觉得才属不科学事件。[2014.8.3-0:0 - 1:45]

4 改进

(2) 师兄讲的规格

- 晶振引出的线尽量对称。晶振下面无覆铜:Place >> Polygon Pour Cutout,晶振下无过孔,不走线。

- 滤波电容尽量靠近VCC及其引脚旁。

- 同一芯片的多个电源不要连在一起(防一根电源线同时供多个引脚电流过大烧坏电源线)。

- 线距,线径(线径越小阻抗越大)[如二者都默认10mil],过孔径要合适。

- 补泪滴:Tools >> TearTrops….选择补泪滴项。

- 避免死铜:覆铜时勾选RemoveDead Copper。地线连接加覆铜的情况下,要将线与覆铜融合。建议将所有地线连接的原因:板子很密集时,覆铜覆不到。

- 器件外壳可能比丝印线宽大,器件之间要隔远一点,防止到时器件放不下。

- 两层板:上层走线和下层走线尽量保持垂直。

- 两层有两个地时,要打多个过孔来保持地的连接。

- 各个器件的名字(丝印)统一放在器件的某个方向。

- 布局时主控芯片、大器件周围空隙大一些,方便布线。

- 板框四角用弧角,避免划手。四角上过孔(焊盘)周围空出来。

- LED靠边(个人喜好)。

(3) 老师讲的

- 双面板PCB设计的原则和要求。对于双列直插器件,一般是一面放元件,另一面走线。

- 布局时,根据功能来分区(输入模块,输出模块,处理模块)。外围器件朝向要统一。

- 电源不能画错,否则很容易将板子烧坏。

- 晶振源和差分信号的连线都需要对称,因为线长度不一样阻抗就不一样,若不对称可能会带来较大干扰。

- 一般小信号或模拟信号用宽线连接。高频信号用细线连接。

PNote Over.