FPGA上实现VGA接口

手头有一块晶振50MHz的cyclonII EP2C6的开发板,拿来做VGA显示接口的实验。查询常见刷新频率表,可以选择800*600@72Hz的模式。

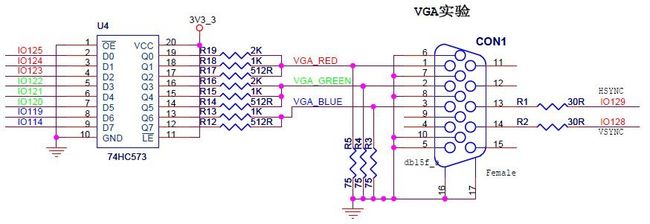

一、硬件连接

VGA是15针接口,有用的为1(红)2(绿)3(蓝)三根模拟信号,以及13(行同步)14(帧同步)以及地信号。颜色采用8bit 3:3:2RGB,可以显示256种不同的颜色。

二、时序分析

在800*600@72Hz模式下水平(行)周期为1040个像素(Pix)

垂直扫描周期为666个像素

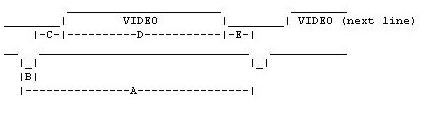

其中水平扫描时序为

其中 A 为周期1040个像素,B为同步信号脉冲,为120个像素,C为后沿61个像素,D为有效显示806个像素,E为前沿53个像素;

同理可知垂直同步信号为周期666像素,同步信号为125像素,后沿为436像素,有效显示为604像素,后延为35像素;

二、编写显示彩条的verilog程序

1)接口定义

module

VGA

(

i_clk ,

i_rst_n ,

o_red ,

o_bule ,

o_green ,

o_Hsnyc ,

o_Vsnyc ,

i_key3

);

2)参数定义

parameter LinePeriod = 12'd1040 ;

parameter H_SyncPulse = 10'd120 ;

parameter H_BackEdge = 10'd61 ;

parameter H_frontEdge = 10'd53 ;

parameter H_ActivePix = 10'd806 ;

parameter FramePeriod = 10'd666;

parameter V_SyncPulse = 10'd6;

parameter V_BackEdge = 10'd21;

parameter V_frontEdge = 10'd35;

parameter V_ActiveLine = 10'd604;

3)产生同步信号

//水平扫描计数器

always @ (posedge i_clk or negedge i_rst_n)

begin

if(!i_rst_n) x_cnt <= 1;

else if (x_cnt == LinePeriod) x_cnt <= 1;

else x_cnt <= x_cnt + 1;

end

//水平扫描同步B信号的产生

always @ (posedge i_clk or negedge i_rst_n)

begin

if(!i_rst_n) o_Hsnyc <= 1;

else if(x_cnt == 1) o_Hsnyc <= 0;

else if(x_cnt == H_SyncPulse) o_Hsnyc <= 1;

end

同样的方法产生垂直同步信号,不在赘述

4)显示

由于是显示彩条,只要知道扫描到什么位置显示就可以了,不用管前沿和后延信号

//265色 RGB信号的输出

always @ (posedge i_clk or negedge i_rst_n)

begin

if(!i_rst_n)

begin o_red <= 3'b000 ; o_green <= 3'b000 ; o_bule <= 2'b00 ; end

else

//显示横屏

begin

if(y_cnt < 127) begin o_red <= 3'b111 ; o_green <= 3'b000 ; o_bule <= 2'b00 ; end

else if(y_cnt < 227) begin o_red <= 3'b111 ; o_green <= 3'b000 ; o_bule <= 2'b00 ; end

else if(y_cnt < 327) begin o_red <= 3'b000 ; o_green <= 3'b111 ; o_bule <= 2'b00 ; end

else if(y_cnt < 427) begin o_red <= 3'b000 ; o_green <= 3'b111 ; o_bule <= 2'b00 ; end

else if(y_cnt < 527) begin o_red <= 3'b000 ; o_green <= 3'b000 ; o_bule <= 2'b11 ; end

else if(y_cnt < 627) begin o_red <= 3'b000 ; o_green <= 3'b000 ; o_bule <= 2'b11 ; end

else if(y_cnt < 666) begin o_red <= 3'b111 ; o_green <= 3'b111 ; o_bule <= 2'b11 ; end

else begin o_red <= 3'b000 ; o_green <= 3'b000 ; o_bule <= 2'b00 ; end

end

end