DISPLAY CONTROLLER

Q: What is the maximum resolution of LCD display?

A: Max frequency 83MHz, Max resolution 1280x1024 @60Hz

This is only reference. It is limited by memory bandwidth according to user scenario

or data type.

Q: Can RGB and MIPI output simultaneously?

A: No. One interface type should be chosen, because there is one display controller.

Q: Duty ratio of VCLK is not 50:50. How to change duty ratio?

A: Specification of VCLK duty ratio is in the range of 50:50 ± 10%. If CLKVAL_F of

VIDCON0 register is even number, that is, video clock source is divided by odd number,

duty ratio of VCLK can be out of range. To make 50:50 duty, CLKVAL_F should be odd number.

If it is hard to make specific VCLK with odd CLKVAL_F value, you can use SCLK_FIMD as

video clock source and control divider value in Clock controller. You can find FIMD_RATIO

in CLK_DIV1 register in user's manual.

CAMERA INTERFACE

Q: What is the maximum frequency and resolution for camera I/F?

A: Max The maximum PCLK is up to 83MHz.

The PCLK is more than 83MHz for 1080P recoding, so you should use MIPI I/F for 1080p

recoding. Max input image size is 8192x8192 in case of scaler bypass mode. If using scaler

or rotator, it can be restricted. Please refer to user's manual.

Q: Is 16bit interface supported by Camera I/F?

A: Not supported.

MIPI DSI

Q: What is DSI initializing sequence?

A: As below sequence you set.

-. Using HS clock in DSI for DDI operating clock

1. DSI initialize

1.1 Set No of DSI Lane

1.2 Configure DSI PLL and turn on

1.3 Set escape clock divider and enable byte clock and escape clock.

1.4 Set relation of display controller (video/command mode, size, porch)

2. Initialize display controller (refer to the display part)

3. Start display controller

4. Transfer initialization DDI command through DSIM

-. Not using HS clock in DSI ( DSI has external clock source )

1. DSI initialize

1.1 Set No of DSI Lane

1.2 Configure DSI PLL and turn on

1.3 Set escape clock divider and enable byte clock and escape clock.

1.4 Set relation of display controller (video/command mode, size, porch)

2. Transfer initialization DDI command through DSIM.

3. Initialize display controller ( refer to the display controller)

4. Start display controller

Q: C110 supports both command mode and video mode in MIPI DSI?

A: Yes. C110 supports both command and video MIPI DSI mode.

Q: How to debug MIPI DSI?

A: check below item.

1. Check below 'DISPLAY_CONTROL' register setting.

: If you want to use MIPI DSI, you must set 'DISPLAY_PATH_SEL' value is '10' or '11'.

2. Check EINT filter enable or not in TE signal from LCD module.

: All EINT filter in C110 should be set 'enable' for avoiding unintended interrupt.

MIPI CSI

Q: How to debug problem in MIPI CSI I/F ?

A: Check below item.

1. Check clock-lane and data-lane signals from camera module.

CSIS data is transmitted continuously regardless of receive chip.

In stop mode data and clock lane are 1.1V.

In run mode these signal swing with 200mV range above 200mV.

2. Check that MIPI power is supplied properly.

VDD_MIPI_A(K15) is 1.8V. VDD_MIPI_D(H14,H15) and VDD_MIPI_PLL(K13) is 1.1V.

3. Check status register (CSIC_DPHYSTS)

If you confirm that MIPI_CSI is operating or not, check MIPI_CSI status register

(CSIS_DPHYSTS : base + 0x0C). In case of using 2-lane data transmit, CSIS_DPHYSTS

value changes between 0xF1 and 0xC0. But using continuous clock mode, CSIS_DPHYSTS

value changes between 0xF0 and 0xC0.

Q: What is CSIS initializing sequence?

A: As below sequence you set.

1. Camera module initialize ( stream data off and set camera ISP only)

2. CSIS initialize and on ( both link and PHY )

3. Camera module start ( stream data on )

4. FIMC start.

Q: How to debug SOT(start of transmission) error ?

A: SOT error is occurred by PHY incorrect timing. First, you check T_hs-prepare and T-hs-zero

timing as below. And then you set CSIS_DPHYCTRL[31:27] register to modify AC timing.

But CSIS_DPHYCTRL[31:27] register is hidden spec. If you want to get more information,

please contact SOC_CSE team after checking T_hs-prepare and T_hs-zero.

Q: How to debug Overflow error?

A: If CSIS input bandwidth is more than output bandwidth, overflow error is occurred.

This problem is cleared by control input bandwidth is higher or output bandwidth is lower.

- Input bandwidth : MIPI speed (Mbps/lane) * number of data-lane.

- Output bandwidth : pixel clock(from CSIS) * 32 (if parallel bit is set in CSIS_CTRL register)

G3D

Q: What API is supported in C110?

A: C110 support OpenGL_ES1.1, OpenGL_ES2.0 and OpenVG1.0 industry API.

MFC

Q: What is the performance and restriction when encoding and decoding simultaneously?

A: The performance is 720P 30fps encoding and decoding at the same time.

Q: What parameter is the factor to affect encoding video quality?

A: In VBR mode (Rate control is off), video quality will increase by decreasing

FrameQp value. In CBR mode (Rate control is on), video quality will increase by

increasing bit-rate.

Q: How can VBR mode be changed into CBR mode?

A: To change the encoding mode, ENC_RC_CONFIG(offset address : 0xC5A0) bit[9](FR_RC_EN)

and bit[8](MB_RC_EN) are set to 1 (RC on) in MFC SFR.

Q: What size is the limit of one encoded frame in encoding?

A: There is no limit of encoded frame size in H/W side.

Q: What is the sequence in power on and off MFC block?

A: While input clock is togglng, MFC block power can turn on and off.

Power off sequence - Clock on -> Power off -> Clock off

Power on sequence - Clock on -> Power on

Q: In case data aborts happens in MFC operation, what may be the cause?

A: Stream buffer and YUV buffer need to have "non-cacheable" memory.

1.26 TV OUT & VIDEO DAC

Q: The green color (or other color) is displayed on TV?

A: Check

TV OUT & VIDEO DAC

Q: The green color (or other color) is displayed on TV?

A: Check the below items out.

1. Comply with the TV subsystem(VP-Mixer-HDMI(Tvenc)) enable/disable sequence.

The SFRs of Video Processor and Image Mixer is updated by Vertical Sync of TVENC‘s

Timingn Generator. Thus, SFRs are configured before this bit is enabled. The

enabling sequence is as follows:“VP -> MIXER -> TVENC(HDMI)” Also, because SFRs

are updated by Verical Sync, the disabling sequence is following as:

“VP -> MIXER -> TVNEC(HDMI)” If you want to stop the operation of MIXER, make

REG_RUN bit “0” and check whether MIXER_OPERATION_STATUS bit is “1”. And then,

off the HDMI or Tvenc.

2. Comply with the clock and block power on/off sequence of the TV subsystem

TV Sub-System Block(T Blk) is synchronous reset block. Therefore, Before block power

is turned on,all IP’s clocks should be turn on. When you turn off the T Block, Turn

off the T-block power, thereafter turn off the clocks. Other Block is same as T-Block

Q: Display is blurry or there is afterimage on TV?

A: Check whether coefficient value of oversampling filter is default value.

VIDEO PROCESSOR

Q: What is the maximum resolution able to process at VP?

A: Input source size is supported up to 1920x1080, and minimum size is 32x4.

: Are there supported data format?

A: Supported data format : NV12, Tiled NV12

MIXER

Q: Is there the off sequence of MIXER operation?

A: The disabling sequence of TV(HDMI) subsystem is basically following as :

VP disable -> Mixer disable-> HDMI disable.

And If you want to stop the operation of MIXER, make REG_RUN bit of MIXER_STATUS

register to "0" and check MIXER_OPERATION_STATUS bit whether it is "1"(MIXER is

idle mode). And then disable HDMI.

Q: The UI display quality of MIXER's graphic layers is not good in case of the

interlaced output with vertical x2 scale-up. (ex. 1080i@60Hz).

The example of output image is as in the following : source UI image size(960x540p),

output UI image size(1920x1080i)

A: MIXER get the even and odd field data individually, and then scaled up individually.

So, displayed UI graphic quality is bad. The vertical scale-up of the graphic layers

is only duplicated. Work-around example for this is as in the following :

At the interlaced output mode, like 1080i@60Hz, the original setting(bad case) are

MIXER_CFG[2] = 0(interlaced mode) and MIXER_GRAPHICx_WH[12] = 1(x2 duplication).

But, to improve the displayed UI quality, you should set to MIXER_CFG[2] = 1

(progressive mode) and MIXER_GRAPHICx_WH[12] = 0(no scale). If you set like these,

the displayed image will become much better quality. But, the bandwidth of the graphic

layers will be doubled. That is to say, MIXER will get the 960x540 size instead of the

960x240 in each field period.

HDMI

Q: Is HDMI Compliance test done in BSP?

A: Yes, It's done.

Q: How to debug the failure item which customer meets in HDMI compliance test?

A: 1. Test ID 7-2(TMDS-VL) fail : in case of VL < 2.7V.

Adjust the TMDS Data Amplitude Control or TMDS Clock Amplitude Control bits to lower

value than current setting. (For detail, refer to the HDMI PHY configuration section

of the user's manual)

2. HDMI signal eye-diagram fail

Pre-determined differential line impedance of the differential pairs is 100[Ohm].

And recommended range of the differential line impedance of the trace is between

95[Ohm] to 105[Ohm].

- When you draw signals to make 5x, it would better to shorten the gap in 1x range

(Gap1 & Gab2). The smallest gap1 and gap2 are best.

- Please check the power ripple of VDD_HDMI_PLL Power(1.1V) under SET.

- Recommend VDD_HDMI_PLL Power(1.1V) to use LDO-power because of Power ripple.

If no LDO, you have to get stable DC-DC power absolutely.

For detail, refer to the HDMI Artwork Guide of C110 Circuit Design Guide.

Q: How to use HDCP? Is HDCP key fused?

A: HDCP key is internally fused in C110 and V210.

Q: How to design HPD, CEC signal connection?

A: CEC signal is multiplexed with EXT_INT[12] and HPD signal is multiplexed with EXT_INT[13].

- CEC signal design guide

- HPD signal design guide

Besides the upper case, you can use the HDMI companion chip for all related HDMI signals.

Q: What is the maximum resolution and frame rate for HDMI output?

A: The maximum output resolution is 1080p@30Hz, 720p@60Hz, 1080i@60Hz.

Additionally, the various other formats are supported up to 74.25Mhz pixel clock.

Q: What is I2C channel used for DDC interface?

A: We recommend that I2C channel 1 is used for DDC interface. Moreover, it should not be

used with other I2C slave. That is to say, It is recommend that I2C channel 1 is only

connected with HDMI DDC if using the HDMI.

Q: The green color(or other color) is displayed on TV?

A: Check the below items out.

1. Comply with the TV subsystem(VP-Mixer-HDMI(Tvenc)) enable/disable sequence.

The SFRs of Video Processor and Image Mixer is updated by Vertical Sync of TVENC‘s

Timing Generator. Thus, SFRs are configured before this bit is enabled. The enabling

sequence is as follows: “VP -> MIXER -> TVENC(HDMI)” Also, because SFRs are updated by

Verical Sync, the disabling sequence is following as:“VP -> MIXER -> TVNEC(HDMI)”

If you want to stop the operation of MIXER, make REG_RUN bit “0” and check whether

MIXER_OPERATION_STATUS bit is “1”. And then, off the HDMI or Tvenc.

2. Comply with the clock and block power on/off sequence of the TV subsystem

TV Sub-System Block(T Blk) is synchronous reset block. Therefore, Before block power

is turned on, all IP’s clocks should be turn on. When you turn off the T Block, Turn off

the T-block power, thereafter turn off the clocks. Other Block is same as T-Block

3. If you enabled the HDCP function, check the below items whether there is some problem

about the HDCP key.

- Check whether the HDCP key is internally fused in the C110/V210

: During initialize the HDCP, the "An" and "Aksv" values transferred to TV should not be

"zero".

- Aren't there any errors like ECC fail while load the HDCP key?

SD/MMC CONTROLLER

Q: Can eMMC be used as storage device?

A: Yes. Of course you can.

Q: Should pull-up resistor put on CMD & DATA signal of SD/MMC I/F externally? What is

the recommended resistance?

A: If connect too big register to CMD and DATA lane, it will be responsible for timing

issue. So 10KOhm at command lane and 50KOhm at data lane is our guidance.

Q: Can be support eMMC4.41 Spec?

A: Originally, C110/V210 is compatible with eMMC4.3, but 8 more eMMC4.41 features are can

be support. Please refer to below newly added feature list on eMMC4.41.

1. Boot Operation (with DDR mode) - C110/V210 HW can not support.(SDR mode only).

2. Sleep mode - C110/V210 HW can support, but S/W Driver required.

3. Reliable write - C110/V210 HW can support, but S/W Driver required.

4. Dual data rate - C110/V210 HW can not support.

5. Multiple Partition - C110/V210 HW can support, but S/W Driver required.

6. Security Enhancement - C110/V210 HW can support, but S/W Driver required.

7. TRIM - C110/V210 HW can support, but S/W Driver required.

8. Reply protected memory block - C110/V210 HW can support, but S/W Driver required.

9. Background Operation - C110/V210 HW can support, but S/W Driver required.

10. High Priority Interrupt - C110/V210 HW can support, but S/W Driver required.

Q: If customers are using eMMC4.41 devices, can it be used as booting device?

A: Even though using eMMC4.x device, do not need to use boot partition. It means that eMMC4.x

devices can be used as booting device with user's partition. If customers want to use boot

partition, they have to use eMMC4.3 booting mode. All eMMC4.41 devices also have backwards

compatibility.

Q: SD clock can be stop during idle time?

A: Yes. If SD/MMC host controller is not access SD/MMC devices, SD/MMC clock can be stop.

Current will be saved around 20mA at VDD_MMC power and card power. If current is not a issue,

clock does not need to control.

Q: What is loading capacitance limitation?

A: Since SD/MMC is high speed signal, loading capacitance is very important. Don't exceed 40pF

per each data line.

Q: Data lines signal quality is too bad, overshoot/undershoot is detected.

A: For optimize signal quality; you should control IO drive strength. Please optimize drive

strength based on customer's set environment.

Q: between 4 bit mode and 8 bit mode, which one is better?

A: 8 bit mode has double bandwidth than 4 bit mode, but many cards are not faster than 25MB/sec.

please check your device's maximum performance.

Q: How can we solve 'Data CRC Error' problem?

A: First of all, customer should check that signal timing is meets on JDEC spec.

using feedback delay setting, signal timing can be turning.

Q: Sometimes cannot initialize SD/MMC cards, what can we do?

A: Right after card power-up, cards are needs delay time. It is described in JDEC spec.; 74cycle

should be required before first command (reset command or OCR command).

USB2.0 OTG

Q: Both of device and host modes can be used?

A: Only device mode can be used. Solution for host mode isn't prepared yet.

Q: How is the XuOtgID pin used?

A: It is leaved as floating (>100KOhm) in the case of device mode.

Q: Which function of USB2.0 Device is supported?

A: Complies to USB 2.0 Spec. (Rev 1.0a)

Operates in High-Speed (48-Mbps) and Full-Speed (12 Mbps)

Supports UTMI+ Level 3 interface (Rev 1.0)

1 Control EP0 for control transfer

15 Device Mode programmable EPs

Programmable EP type: Bulk, Isochronous or Interrupt.

Programmable IN/OUT direction.

Supports packet-based, dynamic FIFO memory allocation of 7936 depths (35-bit width)

Q: How to control the shape of eye pattern diagram for USB2.0 Device DP/DM signal?

A: Please contact to [email protected].

Q: How to design USB2.0 Device layout?

A: DM and DP are differential signal, impedance should be 90 Ohm (-/+ 5 Ohm)

Q: What is the range of USB2.0 OTG VBUS voltage?

A: Valid Vbus voltage range is a 4.4V - 5.25V.

MODEM INTERFACE

Q: Which kind of modem interface can be supported?

A: C110 has modem interface IP which consist of 16kB DPRAM and interrupt logic.

In addition, OneDRAM in POP package or USB I/F can be used for higher speed modem support.

Q: Can Modem interface wake up from power mode?

A: No. Also DPRAM can't be accessed in power mode.

Q: Is there any problem with the case that AP & Modem access DPRAM simultaneously?

A: Both AP and modem can write at different area at the same time. In case that one write and

the other read same area simultaneously, there is no issue about interface access, but can

be possibility that read data is wrong. And when both try to write to the same address area

at the exact same time, the result is not guaranteed.

Therefore, DPRAM solution divides DPRAM into 3 different areas generally. First one is

shared area,such as mail box generating interrupt. Second one is RX area where AP read it

and Modem write it. Third one is TX area where AP write it and Modem read it. It can make

data exchange safer.

DRAM CONTROLLER

Q: How to route DRAM signal

A: 请参考"Hardware design guide" 文档.

SROM CONTROLLER

Q: What is the data bus width supported?

A: Supports either 8 or 16-bit data bus, but 16-bit data bus for BANK0.

To select SROM address base(8bit or 16bit) for each memory bank, control

the AddrMode and DataWidth bits of SROM_BW register(0xE800_0000)

Q: What is the address bus width supported?

A: It is supported to 23 bits width(Xm0ADDR[22:0]), but Xm0ADDR[22:16] are

multiplexed with other functions and Xm0ADDR[22:16] are not released retention

automatically like Xm0ADDR[15:0].

ONENAND CONTROLLER

Q: 可以同时使用OneNand和Nand接口吗?

A: 不推荐,因为有些pin是复用的.

Q: 在sleep mode为了减少漏电流OneNand I/Os是如何设置的?

A: 如果使用oneNAND,相关的nCS和nRP pins在sleep mode应该设置为

"Output High and No pull" ,其它的设为" Input and Pull-down".

NAND FLASH CONTROLLER

Q: 可以同时使用OneNand和Nand接口吗?

A: 不推荐,因为有些pin是复用的.

SYSTEM TIMER

Q: How to guarantee the accuracy of system time?

A: You can start to have doubts about the system time if you experiences the frame drop of

the streaming contents playing (such as DMB) even in the strong electric field. In this

situation, you can identify the accuracy of system time with RTC. In timer ISR, you insert

the routine in which the BCD time of RTC and system time is compared, and report the alert

if its difference is increasing or decreasing. This means the system time is wrong.

Q: Why system timer is inaccurate (PWM Counter buffer)?

A: PWM Timer is fed with PCLK through its prescalar and divider.

Normally, the system time is passing with fixed period of PWM interrupt. But if the counter

value of timer is not exact due to the integer division of prescalar and divider, the period

of PWM interrupt is not same with what expected. If the system time is not exact, you must

check the counter buffer value of PWM timer.

Q: Why system timer is inaccurate (Long execution time of ISR)?

A: If you insert the debug message in ISR, it can cause the inaccuracy of timer.

Usually, the debug message is printed out via UART with 115200 bps. It means that it takes

about 100 us to flush 1 character. And about 1ms is delayed if you print out 10 characters.

WATCHDOG TIMER

Q: How long does it take until XnRSTOUT fall down after Watchdog reset ?

A: It takes about 10us.

Q: Can DRAM keep the data after Watchdog reset happen?

A: No, it is not guaranteed.

Q: How do we know if the Watchdog Reset happen?

A: you can check the Reset Control Register(RST_STAT, Address = 0xE010A000).

When the watchdog reset happen, bit [2] of this register set to '1'

Q: In case of using PS_HOLD signal for holding system power, what can be a reason if system

power is turned off just after Watchdog Reset occurs?

A: When PS_HOLD_OUT_EN bit-field in PS_HOLD_CONTROL is set to 1, EINT0 pin still keeps high

even in watchdog reset. Please check it.

REAL TIME CLOCK

Q: Even thoght the VDD_RTC is not supplied, can it Boot?

A: Yes, but RTC Block won't be operated. We recommand that VDD_RTC should be supplied..

Q: Can RTC Clcok be used from the other component, for examle PMIC, In order to reduce a Crystal

component?

A: Yes.

Q: In case of using PS_HOLD signal for holding system power, what can be a reason if system

power is turned off just after Watchdog Reset occurs?

A: When PS_HOLD_OUT_EN bit-field in PS_HOLD_CONTROL is set to 1, EINT0 pin still keeps high

even in watchdog reset. Please check it.

REAL TIME CLOCK

Q: Even thoght the VDD_RTC is not supplied, can it Boot?

A: Yes, but RTC Block won't be operated. We recommand that VDD_RTC should be supplied..

Q: Can RTC Clcok be used from the other component, for examle PMIC, In order to reduce a Crystal

component?

A: Yes.

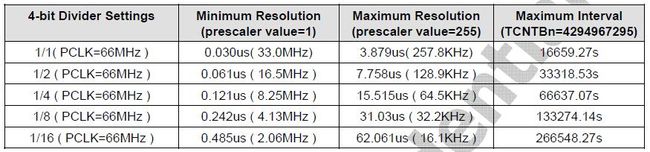

PWM TIMER

Q: What is the resolution?

A: It depends on the prescaler value and 4-bit divider setting value.

The Minimum and the Maximum resolution is followings.

Q: Why PWM delay time is not exact?

A: If you want to use the small delay under 1ms, you can use the PWM timer.

In this case, expecting time may be wrong if you use the PWM timer as One-shot mode.

It takes a small time to set up the timer, moreover the timer looks expired even in zero time

if TCNTO SFR is accessed to check the elapse of time during this "small time".

To avoid this, you should set the PWM timer as free-running counter - auto- reload with

relatively long period. With this method, you can guarantee the exact delay time ± minimum

resolution of counter, and it is safe to be accessed by multiple process.

Q: The motor is controlled by PWMOUT. But the motor glitch occurs.

A: check the PWM frequency and duty with oscilloscope (clock resolution & clock counter).

SYSTEM TIMER

Q: How to guarantee the accuracy of system time?

A: You can start to have doubts about the system time if you experiences the frame drop of the

streaming contents playing (such as DMB) even in the strong electric field. In this situation,

you can identify the accuracy of system time with RTC. In timer ISR, you insert the routine

in which the BCD time of RTC and system time is compared, and report the alert if its difference

is increasing or decreasing. This means the system time is wrong.

Q: Why system timer is inaccurate (PWM Counter buffer)?

A: PWM Timer is fed with PCLK through its prescalar and divider.

Normally, the system time is passing with fixed period of PWM interrupt. But if the counter

value of timer is not exact due to the integer division of prescalar and divider, the period

of PWM interrupt is not same with what expected. If the system time is not exact, you must

check the counter buffer value of PWM timer.

Q: Why system timer is inaccurate (Long execution time of ISR)?

A: If you insert the debug message in ISR, it can cause the inaccuracy of timer.

Usually, the debug message is printed out via UART with 115200 bps. It means that it takes about

100 us to flush 1 character. And about 1ms is delayed if you print out 10 characters.

Q: Why PWM delay time is not exact?

A: If you want to use the small delay under 1ms, you can use the PWM timer.

In this case, expecting time may be wrong if you use the PWM timer as One-shot mode.

It takes a small time to set up the timer, moreover the timer looks expired even in zero time

if TCNTO SFR is accessed to check the elapse of time during this "small time".

To avoid this, you should set the PWM timer as free-running counter - auto- reload with

relatively long period. With this method, you can guarantee the exact delay time ± minimum

resolution of counter, and it is safe to be accessed by multiple process.

Q: The motor is controlled by PWMOUT. But the motor glitch occurs.

A: check the PWM frequency and duty with oscilloscope (clock resolution & clock counter).

SYSTEM TIMER

Q: How to guarantee the accuracy of system time?

A: You can start to have doubts about the system time if you experiences the frame drop of the

streaming contents playing (such as DMB) even in the strong electric field. In this situation,

you can identify the accuracy of system time with RTC. In timer ISR, you insert the routine

in which the BCD time of RTC and system time is compared, and report the alert if its difference

is increasing or decreasing. This means the system time is wrong.

Q: Why system timer is inaccurate (PWM Counter buffer)?

A: PWM Timer is fed with PCLK through its prescalar and divider.

Normally, the system time is passing with fixed period of PWM interrupt. But if the counter

value of timer is not exact due to the integer division of prescalar and divider, the period

of PWM interrupt is not same with what expected. If the system time is not exact, you must

check the counter buffer value of PWM timer.

Q: Why system timer is inaccurate (Long execution time of ISR)?

A: If you insert the debug message in ISR, it can cause the inaccuracy of timer.

Usually, the debug message is printed out via UART with 115200 bps. It means that it takes about

100 us to flush 1 character. And about 1ms is delayed if you print out 10 characters.

UART

Q: What is the maximum baudrate and endurance for each UART port?

A: Four UART supports 3Mbps ports for Bluetooth 2.0 and UART Frame error should be less than

1.87%(3/160)

For Example)

1. Baud Rate Configuration

There are four UART baud rate divisor registers in the UART block, namely, UBRDIV0,

UBRDIV1,UBRDIV2 and UBRDIV3. The value stored in the baud rate divisor register (UBRDIVn)

and dividing slot register(UDIVSLOTn) is used to determine the serial Tx/Rx clock rate

(baud rate) as follows:

DIV_VAL = UBRDIVn + (num of 1's in UDIVSLOTn)/16

DIV_VAL = (PCLK / (bps x 16)) −1 or DIV_VAL = (SCLK_UART / (bps x 16)) −1

Using UDIVSLOT, you can generate the baud rate more accurately. For example, if the

baud-rate is 115200 bps and SCLK_UART is 40 MHz, UBRDIVn and UDIVSLOTn are:

DIV_VAL = (40000000 / (115200 x 16)) -1 = 21.7 -1 = 20.7

2. Baud Rate Error Tolerance

tUPCLK = (UBRDIVn + 1) x 16 x 1Frame / (PCLK or SCLK_UART)

tEXTUARTCLK = 1Frame / baud-rate

* tUPCLK: Real UART Clock, tEXTUARTCLK: Ideal UART Clock

UART error = (tUPCLK − tEXTUARTCLK) / tEXTUARTCLK x 100%

Q: Debug message through the UART port cannot be read.

A: If the source clock is changed, the UART baudrate is also changed. To fix this problem,

you should adjust the UBRDIVn and UDIVSLOTn.

Q: There is lots of frame/ parity error on UART when using high speed BT.

A: To fix this problem, match the baudrate between BT module and UART by calculating

exact baudrate of UART (UBRDIV and UDIVSLOT). In some source clock, you can generate exact

baudrate, and change the source clock or change the baudrate of BT same with UART.

I2C

Q: How many devices can be used in same I2C bus?

A: Because C110 supports multi-master I2C-bus mode, there is no restrictions on number of

devices can be used in same I2C bus. If there are available GPIOs, we recommend connecting

one device with one I2C bus. C110 has three channel I2C bus. Three devices use each HW I2C

bus and additional devices use I2C by GPIO emulator.

Q: What condition 'I2C bus busy' is set in I2CSTAT register?

A: 'I2C bus busy' is set by start condition. And 'I2C non-busy' is set by stop condition. If you

control external I2C pull up voltage regulator on/off on using I2C, be careful unintended

'I2C bus busy' set by start condition. (ref below fig.) So we recommend not controlling

external pull up voltage regulator. To clear 'I2C bus busy', serial output bit in I2CSTAT is

set '0' and set '1'.

Q: Compare HW I2C and GPIO I2C emulation.

A: Both of HW I2C and GPIO I2C emulation can support 400kbit/s.

GPIO I2C emulation needs more CPU occupation.

Q: How to control the drivability of I2C signal.

A: Modify the GPxDRV register of corresponding GPIO group.

SYSTEM TIMER

Q: How to guarantee the accuracy of system time?

A: You can start to have doubts about the system time if you experiences the frame drop of

the streaming contents playing (such as DMB) even in the strong electric field. In this

situation, you can identify the accuracy of system time with RTC. In timer ISR, you insert

the routine in which the BCD time of RTC and system time is compared, and report the alert

if its difference is increasing or decreasing. This means the system time is wrong.

Q: Why system timer is inaccurate (PWM Counter buffer)?

A: PWM Timer is fed with PCLK through its prescalar and divider.

Normally, the system time is passing with fixed period of PWM interrupt. But if the counter

value of timer is not exact due to the integer division of prescalar and divider, the period

of PWM interrupt is not same with what expected. If the system time is not exact, you must

check the counter buffer value of PWM timer.

Q: Why system timer is inaccurate (Long execution time of ISR)?

A: If you insert the debug message in ISR, it can cause the inaccuracy of timer.

Usually, the debug message is printed out via UART with 115200 bps. It means that it takes

about 100 us to flush 1 character. And about 1ms is delayed if you print out 10 characters.

WATCHDOG TIMER

Q: How long does it take until XnRSTOUT fall down after Watchdog reset ?

A: It takes about 10us.

Q: Can DRAM keep the data after Watchdog reset happen?

A: No, it is not guaranteed.

Q: How do we know if the Watchdog Reset happen?

A: you can check the Reset Control Register(RST_STAT, Address = 0xE010A000).

When the watchdog reset happen, bit [2] of this register set to '1'

Q: In case of using PS_HOLD signal for holding system power, what can be a reason if system

power is turned off just after Watchdog Reset occurs?

A: When PS_HOLD_OUT_EN bit-field in PS_HOLD_CONTROL is set to 1, EINT0 pin still keeps high

even in watchdog reset. Please check it.

REAL TIME CLOCK

Q: Even thoght the VDD_RTC is not supplied, can it Boot?

A: Yes, but RTC Block won't be operated. We recommand that VDD_RTC should be supplied..

Q: Can RTC Clcok be used from the other component, for examle PMIC, In order to reduce a Crystal

component?

A: Yes.

Q: In case of using PS_HOLD signal for holding system power, what can be a reason if system

power is turned off just after Watchdog Reset occurs?

A: When PS_HOLD_OUT_EN bit-field in PS_HOLD_CONTROL is set to 1, EINT0 pin still keeps high

even in watchdog reset. Please check it.

REAL TIME CLOCK

Q: Even thoght the VDD_RTC is not supplied, can it Boot?

A: Yes, but RTC Block won't be operated. We recommand that VDD_RTC should be supplied..

Q: Can RTC Clcok be used from the other component, for examle PMIC, In order to reduce a Crystal

component?

A: Yes.

Q: In case of using PS_HOLD signal for holding system power, what can be a reason if system power is turned off just after Watchdog Reset occurs? A: When PS_HOLD_OUT_EN bit-field in PS_HOLD_CONTROL is set to 1, EINT0 pin still keeps high even in watchdog reset. Please check it. REAL TIME CLOCK Q: Even thoght the VDD_RTC is not supplied, can it Boot? A: Yes, but RTC Block won't be operated. We recommand that VDD_RTC should be supplied.. Q: Can RTC Clcok be used from the other component, for examle PMIC, In order to reduce a Crystal component? A: Yes.

PWM TIMER Q: What is the resolution? A: It depends on the prescaler value and 4-bit divider setting value. The Minimum and the Maximum resolution is followings.Q: Why PWM delay time is not exact? A: If you want to use the small delay under 1ms, you can use the PWM timer. In this case, expecting time may be wrong if you use the PWM timer as One-shot mode. It takes a small time to set up the timer, moreover the timer looks expired even in zero time if TCNTO SFR is accessed to check the elapse of time during this "small time". To avoid this, you should set the PWM timer as free-running counter - auto- reload with relatively long period. With this method, you can guarantee the exact delay time ± minimum resolution of counter, and it is safe to be accessed by multiple process. Q: The motor is controlled by PWMOUT. But the motor glitch occurs. A: check the PWM frequency and duty with oscilloscope (clock resolution & clock counter). SYSTEM TIMER Q: How to guarantee the accuracy of system time? A: You can start to have doubts about the system time if you experiences the frame drop of the streaming contents playing (such as DMB) even in the strong electric field. In this situation, you can identify the accuracy of system time with RTC. In timer ISR, you insert the routine in which the BCD time of RTC and system time is compared, and report the alert if its difference is increasing or decreasing. This means the system time is wrong. Q: Why system timer is inaccurate (PWM Counter buffer)? A: PWM Timer is fed with PCLK through its prescalar and divider. Normally, the system time is passing with fixed period of PWM interrupt. But if the counter value of timer is not exact due to the integer division of prescalar and divider, the period of PWM interrupt is not same with what expected. If the system time is not exact, you must check the counter buffer value of PWM timer. Q: Why system timer is inaccurate (Long execution time of ISR)? A: If you insert the debug message in ISR, it can cause the inaccuracy of timer. Usually, the debug message is printed out via UART with 115200 bps. It means that it takes about 100 us to flush 1 character. And about 1ms is delayed if you print out 10 characters.

Q: In case of using PS_HOLD signal for holding system power, what can be a reason if system power is turned off just after Watchdog Reset occurs? A: When PS_HOLD_OUT_EN bit-field in PS_HOLD_CONTROL is set to 1, EINT0 pin still keeps high even in watchdog reset. Please check it. REAL TIME CLOCK Q: Even thoght the VDD_RTC is not supplied, can it Boot? A: Yes, but RTC Block won't be operated. We recommand that VDD_RTC should be supplied.. Q: Can RTC Clcok be used from the other component, for examle PMIC, In order to reduce a Crystal component? A: Yes.