三星uboot-1.1.6源码分析——lowlevel_init.S (2)——时钟配置

三星uboot-1.1.6源码分析——lowlevel_init.S (board\samsung\smdk6410)(1)的链接地址

上一篇主要是此文件的前半部分代码,重点说了时钟的ASYNC MODE和SYNC MODE两种模式。

接着上一篇分析----------现在来看具体的时钟代码,如下所示:

system_clock_init:

ldrr0, =ELFIN_CLOCK_POWER_BASE@0x7e00f000

在Smdk6410.h (include\configs)文件中有定义:

#define CONFIG_CLK_532_133_66

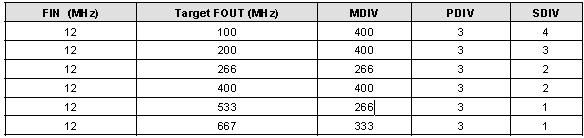

#elif defined(CONFIG_CLK_532_133_66) /* FIN 12MHz, Fout 532MHz */

#define APLL_MDIV 266

#define APLL_PDIV 3

#define APLL_SDIV 1

#define CONFIG_SYNC_MODE

#ifdef CONFIG_SYNC_MODE 看上面,我们定义了这个宏

ldrr1, [r0, #OTHERS_OFFSET]

movr2, #0x40

orrr1, r1, r2

strr1, [r0, #OTHERS_OFFSET]

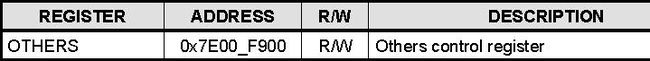

其中有:#define OTHERS_OFFSET0x900

nop

nop

nop

nop

nop

ldrr2, =0x80

orrr1, r1, r2

strr1, [r0, #OTHERS_OFFSET]

上面这一段主要是对寄存器OTHERS的操作,看下面:

check_syncack:

ldrr1, [r0, #OTHERS_OFFSET]

ldrr2, =0xf00

andr1, r1, r2

cmpr1, #0xf00

bnecheck_syncack

确认同步,看下图:

#else /*ASYNC Mode */

nop

nop

nop

nop

nop

ldr r1, [r0, #OTHERS_OFFSET]

bic r1, r1, #0xC0

orr r1, r1, #0x40

str r1, [r0, #OTHERS_OFFSET]

wait_for_async:

ldr r1, [r0, #OTHERS_OFFSET]

and r1, r1, #0xf00

cmp r1, #0x0

bnewait_for_async

ldr r1, [r0, #OTHERS_OFFSET]

bic r1, r1, #0x40

str r1, [r0, #OTHERS_OFFSET]

#endif

下面才是真正的时钟设置:

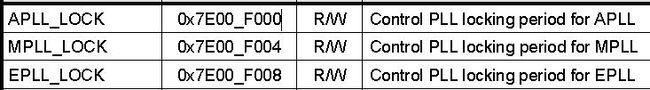

movr1, #0xff00

orrr1, r1, #0xff

strr1, [r0, #APLL_LOCK_OFFSET]

strr1, [r0, #MPLL_LOCK_OFFSET]

strr1, [r0, #EPLL_LOCK_OFFSET]

主要是这三个寄存器:

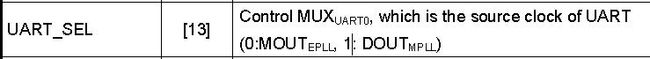

/* CLKUART(=66.5Mhz) = CLKUART_input(532/2=266Mhz) / (UART_RATIO(3)+1) */

/* CLKUART(=50Mhz) = CLKUART_input(400/2=200Mhz) / (UART_RATIO(3)+1) */

/* Now, When you use UART CLK SRC by EXT_UCLK1, We support 532MHz & 400MHz value */

这里说明下,UART可以选择三个时钟源中的一个,这三个时钟源是:

The baud-rate generator can be clocked by PCLK, EXT_UCLK0 or EXT_UCLK1.

#if defined(CONFIG_CLKSRC_CLKUART) 应该和UART有关

ldr r1, [r0, #CLK_DIV2_OFFSET]

bic r1, r1, #0x70000

orr r1, r1, #0x30000

str r1, [r0, #CLK_DIV2_OFFSET]

#endif

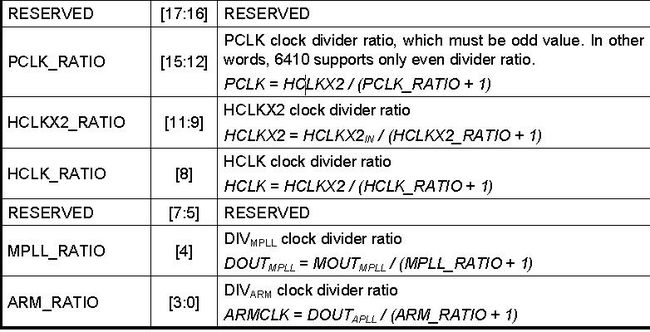

ldr r1, [r0, #CLK_DIV0_OFFSET]/*Set Clock Divider*/

bic r1, r1, #0x30000

bic r1, r1, #0xff00

bic r1, r1, #0xff

ldr r2, =CLK_DIV_VAL

orr r1, r1, r2

str r1, [r0, #CLK_DIV0_OFFSET] ----- 看下面:

#if defined(CONFIG_CLK_800_133_66)

#define Startup_APLLdiv 0

#define Startup_HCLKx2div 2

#elif defined(CONFIG_CLK_400_133_66)

#define Startup_APLLdiv 1

#define Startup_HCLKx2div 2

#else

#define Startup_APLLdiv 0

#define Startup_HCLKx2div 1

#endif

#define Startup_PCLKdiv3

#define Startup_HCLKdiv 1

#define Startup_MPLLdiv 1

#define CLK_DIV_VAL ((Startup_PCLKdiv<<12)|(Startup_HCLKx2div<<9)|(Startup_HCLKdiv<<8)|(Startup_MPLLdiv<<4)|Startup_APLLdiv)

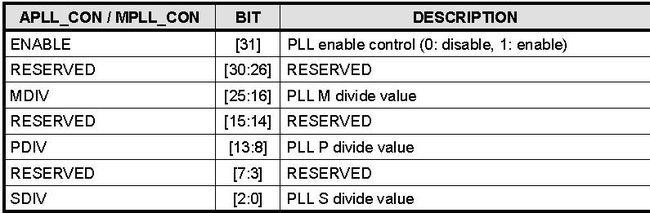

ldr r1, =APLL_VAL

str r1, [r0, #APLL_CON_OFFSET]-----看下面:

#define APLL_VALset_pll(APLL_MDIV, APLL_PDIV, APLL_SDIV)

#define set_pll(mdiv, pdiv, sdiv)(1<<31 | mdiv<<16 | pdiv<<8 | sdiv)

#elif defined(CONFIG_CLK_532_133_66) /* FIN 12MHz, Fout 532MHz */

#define APLL_MDIV 266

#define APLL_PDIV 3

#define APLL_SDIV 1

#define CONFIG_SYNC_MODE

NOTE1:

The output frequency is calculated using the following equation:

FOUT = MDIV X FIN / (PDIV X 2SDIV)

where, MDIV, PDIV, SDIV for APLL and MPLL must meet the following conditions :

MDIV: 64 ≤ MDIV ≤ 1023

PDIV: 1 ≤ PDIV ≤ 63

SDIV: 0 ≤ SDIV ≤ 5

FVCO (=MDIV X FIN / PDIV): 800MHz ≤ FVCO ≤ 1600MHz

FOUT: 40MHz ≤ FVCO ≤ 1600MHz

FIN : 10MHz ≤ FIN ≤ 20MHz

Don't set the value P and M to all zeros.

ldr r1, =MPLL_VAL

str r1, [r0, #MPLL_CON_OFFSET]- - - -看下面:- - -图在上面:

#define MPLL_VALset_pll(MPLL_MDIV, MPLL_PDIV, MPLL_SDIV)

#define set_pll(mdiv, pdiv, sdiv)(1<<31 | mdiv<<16 | pdiv<<8 | sdiv)

/* fixed MPLL 533MHz */

#define MPLL_MDIV 266

#define MPLL_PDIV 3

#define MPLL_SDIV 1

ldrr1, =0x80200203 /* FOUT of EPLL is 96MHz */

strr1, [r0, #EPLL_CON0_OFFSET]

ldrr1, =0x0

strr1, [r0, #EPLL_CON1_OFFSET]----看下面:

ldr r1, [r0, #CLK_SRC_OFFSET]/* APLL, MPLL, EPLL select to Fout */

#if defined(CONFIG_CLKSRC_CLKUART) 我们定义了:#define CONFIG_CLKSRC_CLKUART

ldr r2, =0x2007

#else

ldr r2, =0x7

#endif

orr r1, r1, r2

str r1, [r0, #CLK_SRC_OFFSET]---看下图:

* wait at least 200us to stablize all clock */

mov r1, #0x10000

1:subs r1, r1, #1

bne 1b

#if 0

mrcp15, 0, r0, c1, c0, 0

orrr0, r0, #0xc0000000/* clock setting in MMU */

mcrp15, 0, r0, c1, c0, 0

#endif

#ifdef CONFIG_SYNC_MODE /* Synchronization for VIC port */ 不太懂

ldr r1, [r0, #OTHERS_OFFSET]

orr r1, r1, #0x20

str r1, [r0, #OTHERS_OFFSET]

#else

ldr r1, [r0, #OTHERS_OFFSET]

bic r1, r1, #0x20

str r1, [r0, #OTHERS_OFFSET]

#endif

mov pc, lr 返回

三星uboot-1.1.6源码分析——lowlevel_init.S (3)---串口的链接地址