S5PV210 时钟配置解析

S5PV210时钟体系

S5PV210中包含3大类时钟domain,分别是主系统时钟domain (简称MSYS,下面将使用简称来进行相关讲解)、显示相关的时钟domain (DSYS)、外围设备的时钟domain (PSYS)。

1) MSYS:用来给cortex a8处理器,dram控制器,3D,IRAM,IROM,中断控制器等提供时钟;

2) DSYS:用来给显示相关的部件提供时钟,包括FIMC, FIMD, JPEG, and multimedia IPs;

3) PSYS:用来给外围设备提供时钟,如i2s, spi,i2c,uart等

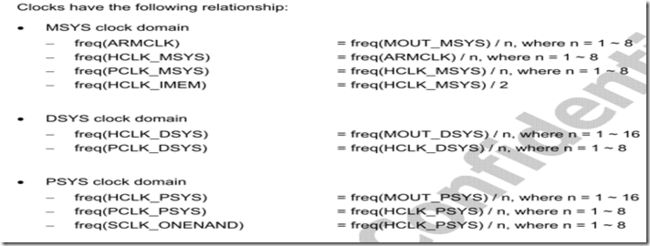

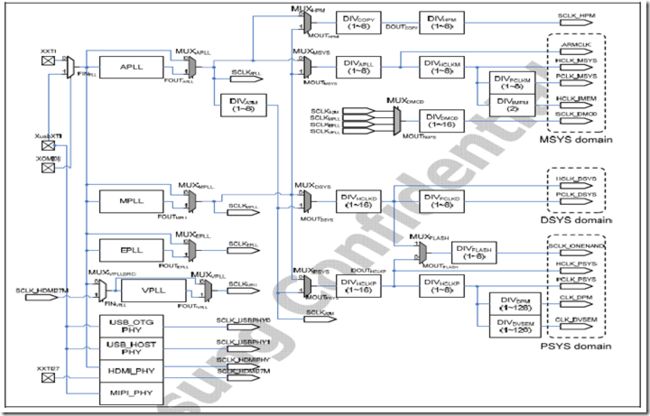

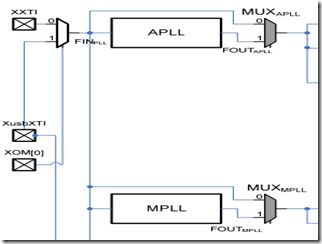

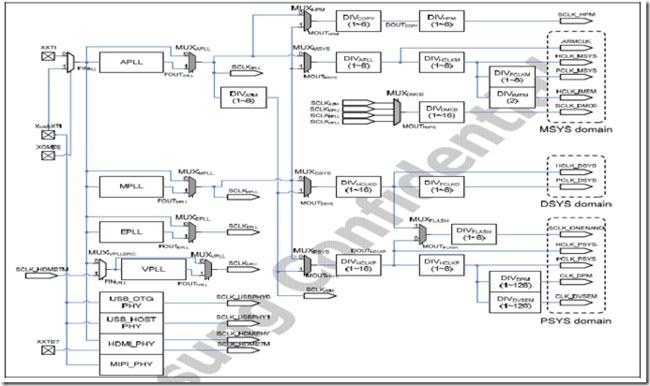

Mini210S外接的晶振频率(简称Fin)为24MHz,通过时钟控制逻辑PLL可以提高系统时钟。S5PV210共有4个倍频器,即PLL,包括APLL(供MSYS使用),MPLL(供DSYS使用),EPLL(供PSYS使用),VPLL(供video相关的时钟使用)。3大类时钟domain中,可以使用不同的分频,使其给不同部件输出所需要的时钟,各类时钟的关系如下图:

S5PV210时钟分类图

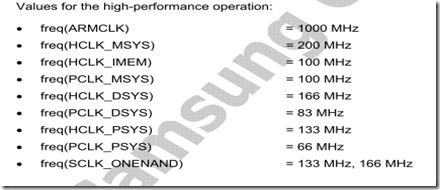

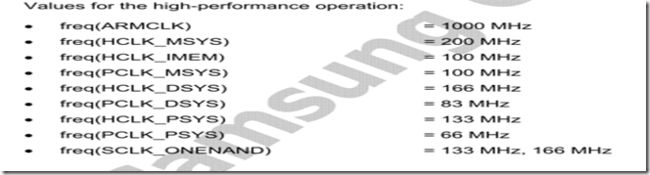

如何确定各类时钟的值,芯片手册上给出了参考值,我们按照参考值设置即可,各类时钟的参考值如下图:

S5PV210时钟设置参考值图

具体如何设置上述各种各样的时钟,可参考下图:

S5PV210时钟设置参考图

该图十分重要,依据上图我们就可以设置好所有硬件部件所需的工作时钟(实际上我们并不需要设置好所有部件的工作时钟,我们只需设置好我们需要使用的硬件部件的工作时钟即可),在本章第二节中,我们将以上图为基础,通过设置时钟相关的寄存器,达到初始化时钟的目的。

程序例子:

分别用了汇编语言和C语言来编写,详细代码见链接。下面以C语言代码来讲解:

1. start.S

在调用main函数之前,调用了时钟初始化函数clock_init,进行时钟相关的设置。

2. clock.c

clock_init()在clock.c中定义,具体代码如下:

void clock_init()

{

// 1 设置各种时钟开关,暂时不使用PLL

CLK_SRC0 = 0x0;

// 2 设置锁定时间,使用默认值即可

APLL_LOCK = 0x0000FFFF;

MPLL_LOCK = 0x0000FFFF;

// 3 设置分频

CLK_DIV0 = 0x14131440;

// 4 设置PLL

APLL_CON0 = APLL_VAL;

MPLL_CON = MPLL_VAL;

// 5 设置各种时钟开关,使用PLL

CLK_SRC0 = 0x10001111;

}

上述代码共有5个步骤,下面我们一一讲解每一个步骤:

第一步 、设置各种时钟开关,暂时不使用PLL

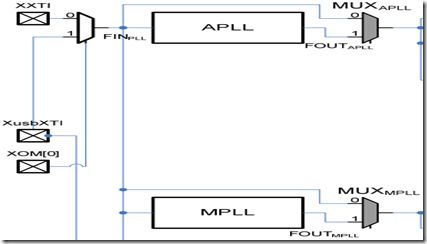

根据时钟设置图,下面是放大图:

首先我们需要选择使用外接24MHz晶振,由上图可知,APLL和MPLL的时钟源由“FIN_PLL”决定,在芯片手册中搜索“FIN_PLL”,可知相关寄存器为CLK_SRC0,见下图:

在未设置PLL和各种分频系数之前,我们不能使用PLL,为了保险起见,暂时直接使用频率较低的外接的24MHz晶振,待设置好PLL和分频系数后再重新设置各种时钟开关。

第二步 、设置锁定时间

设置PLL后,时钟从Fin提升到目标频率时,需要一定的时间,即锁定时间。

第三步 、设置分频

与分频相关的寄存器是CLK_DIV0,见下图:

现在我们来根据本章第一节中给出的时钟设置参考值来设置该寄存器。

-

ARMCLK = 1000MHz = MOUT_MSYS / (APLL_RATIO + 1),经过在第四和第五步的设置后,MOUT_MSYS会被设置为1000MHz,所以 APLL_RATIO=0即可

-

SCLKA2M=200MHz=SCLKAPLL / (A2M_RATIO + 1),由于SCLKAPLL=1000MHz,所以A2M_RATIO=4。

-

HCLK_MSYS=200MHz=ARMCLK / (HCLK_MSYS_RATIO + 1),所以HCLK_MSYS_RATIO=4

-

PCLK_MSYS=100MHz=HCLK_MSYS / (PCLK_MSYS_RATIO + 1),所以PCLK_MSYS_RATIO=1

-

HCLK_DSYS=166MHz=MOUT_DSYS / (HCLK_DSYS_RATIO + 1), 经过在第四和第五步的设置后,MOUT_DSYS =667MHz,所以HCLK_DSYS_RATIO=3

-

PCLK_DSYS=83MHz=HCLK_DSYS / (PCLK_DSYS_RATIO + 1),所以PCLK_DSYS_RATIO=1

-

HCLK_PSYS=133Mhz=MOUT_PSYS / (HCLK_PSYS_RATIO + 1),经过在第四和第五步的设置后,MOUT_PSYS =667MHz所以HCLK_PSYS_RATIO=4

-

PCLK_PSYS=66Mhz=HCLK_PSYS / (PCLK_PSYS_RATIO + 1),所以HCLK_PSYS_RATIO=1

所以CLK_DIV0 = 0x14131440;

第四步 、设置PLL

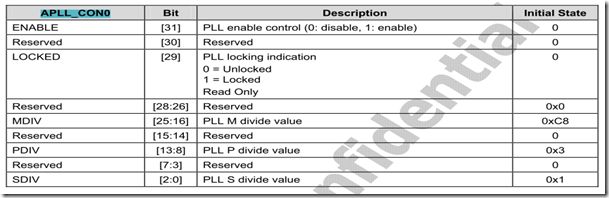

PLL即倍频器,用来放大运行频率。设置好分频后,我们就需要设置PLL了。APLL/MPLL的启动是通过设置APLL_CON0/MPLL_CON寄存器,我们逐个来设置。

APLL_CON0

ALPP_CON0负责设置APLL,FINPLL=24MHz,经过APLL后,我们将输 出FOUT=1000Mhz的时钟频率,FOUT的计算公式如下: FOUT=MDIV*FIN/(PDIV*2^(SDIV-1)) = 1000 MHz

由于FIN=24MHz,FOUT=1000MHz,我们可以这样取值: MDIV= 0x7d,PDIV= 0x3,SDIV=1。这3个值并不是固定死的,只要能使FOUT=1000Mhz,任意搭配都是可以的。

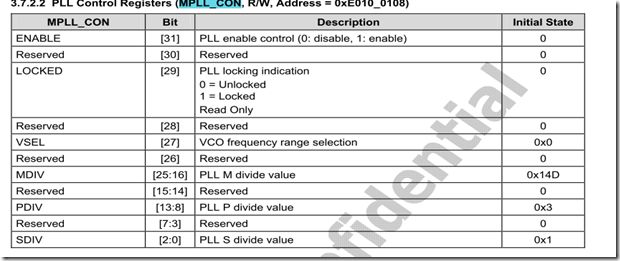

MPLL_CON

MPLL_CON寄存器负责设置MPLL,经过MPLL后,我们将输出FOUT=667Mhz的时钟频率,FOUT的计算公式如下: FOUT=MDIV*FIN/(PDIV*2^SDIV) = 667 MHz

由于FIN=24MHz,FOUT=667MHz,我们可以这样取值: MDIV=0x29B, PDIV= 0xC,SDIV=1。这3个值并不是固定死的,只要能使FOUT=667Mhz,任意搭配都是可以的。

第五步 设置各种时钟开关

S5PV210时钟设置参考图

在上图中,所有的MUX都是用来选择时钟的,相关寄存器是CLK_SRC0, 见下图:

参考S5PV210时钟设置参考图,设置各种时钟开关:

APLL_SEL=1,使用FOUTAPLL

MPLL_SEL=1,使用FOUTMPLL

EPLL_SEL=1,使用FOUTEPLL

VPLL_SEL=1,使用FOUTVPLL

MUX_MSYS_SEL=0,使用SCLKAPLL

MUX_DSYS_SEL=0,使用SCLKMPLL

MUX_PSYS_SEL=0,使用SCLKMPLL

ONENAND_SEL=1,使用HCLK_DSYS

所以CLK_SRC0=0x10001111;

3. main.c

在main函数中实现LED闪烁的功能,与前面的代码大同小异。