四、mini2440裸机程序之MMU(上)

来自ARM920T参考手册

可在以下官方网站下载:

http://infocenter.arm.com/help/index.jsp

一、前期介绍

访问CP15寄存器组的语法:

在特权模式下,访问CP15寄存器组通过MCR/MRC指令:

MCR/MRC{cond} P15 , opcode_1 , Rd , CRn , CRm , opcode_2

Rd : arm920t CPU核的寄存器

CRn : 指定要访问的协寄存器(c0,c1,c3,….)

CRm 和opcode_2 : 在寻址寄存器时指定特殊活动(c0,c1,c2,...)

TLB:TranslationLookaside Buffer

转换索引缓冲(分为I TLB 和 D TLB),用来存储最近使用到的页表条目(sectionor page descriptor) , 这样就避免了每次地址转换时都到主存去查找表,然后再找到相应的描述符.这个存储器用于提高访问性能.

当CPU发出一个VA时,VA转换成MVA , MMU先访问TLB , 看看有没有存储着能转换这个MVA的描述符 . 如果有就直接使用这个描述符进行地址转换和权限检查 , 否则,回到主存里查找表,找到相应的描述符之后进行地址转换和权限检查并把这个描述符写入TLB(如果TLB已满了,则使用round-robit算法找到一个记录项把它覆盖了),这样下次用到这个MVA时就可以直接使用TLB中的描述符.

与MMU相关CP15的协寄存器:

所有的CP15 MMU寄存器里面除了register 8,都包含状态.我们可以通过读取它们通过使用MRC指令,修改它们通过使用MCR指令. 在数据异常期间Registers 5和6都会被MMU写入状态,往Register 8写入会引起MMU执行一次TLB操作,来操作TLB入口.这个寄存器不能被读.在Instruction TLB和Data TLB中都有一份register 10的副本.CP15指令里的opcode_2被用于决定访问的是哪个.

转换表基地址(TTB)

当TLB没有包含一个为要求当前MVA转换匹配的记录项时,硬件转换进程被开启.TTB寄存器指向了物理内存的一张表(包含了段或页描述符,或者两者都有)的基地址.TTB寄存器在被读取的时候低14bits必须被设置为0,这也就要求表必须存放在16KB的边界上.如下图:

同时,此次找到的描述符填入TLB.

转换表可以有高达4096个记录项,每一个记录都为32位,描述了1MB的虚拟内存.这就允许了高达4G的虚拟内存被编址.

关于查表的过程如下表:

一级获取(Levelone fetch)如下:

可以看出TTB[31:14]与MVA[31:20]由以上方式串联出一个4字节的转换表记录,这个记录作为进入一个段基址或者一个页表基址的一级描述符(Level one descriptor).

一级描述符(Level onedescriptor)

这个一级描述符可以是段描述符,可以是粗页描述符,细页描述符,或者是无效的:下面图示了这个一级描述符的格式:

注:

Section descriptor : 提供大小为1MB的内存块基地址.

Page table descriptors : 提供一张页表(包含二级描述符(level two descriptors))的基地址,而且页表还分为两种不同大小:

1)粗页表(coarse page table) : 256个记录项 , 这些记录项把1MB大小的内存分裂成4KB的256个内存块.

2)细页表(fine page table) : 1024个记录项,这些记录项把1MB大小的内存分裂成1KB的1024个内存块.

以下是一级描述符的位定义图示:

其中的C位称为Ctt,B位称为Btt,这两个为配合着Ccr(CP15 register 1的C位)使用,如下图:

C=0,Ctt=X,Btt=0(NCNB):读写不使用cache,直接访问AMBA ASB接口。写数据不被缓冲,CPU需要等待直到数据完整放到AMBA ASB接口上。

C=X,Ctt=0,Btt=1(NCB):读写不使用cache,直接访问AMBA ASB接口。写数据被缓冲并随后出现在AMBA ASB接口上,CPU在数据完全写入write buffer之后尽可能快继续执行。

C=1,Ctt=1,Btt=0(WT):写通模式;读写过程都不能被外设中断

| cache读命中 |

从cache读数据 |

不访问AMBA ASB接口 |

-------------------- |

| cache读缺失 |

引起linefill |

访问一次AMBA ASB接口 |

-------------------- |

| cache写命中 |

更新cache数据 |

所有被写的数据被缓冲并随后出现在AMBA ASB接口 |

在数据被完整缓冲了CPU马上继续执行 |

| cache写缺失 |

不操作cache |

所有被写的数据被缓冲并随后出现在AMBA ASB接口 |

在数据被完整缓冲了CPU马上继续执行 |

C=1,Ctt=1,Btt=1(WB):写回模式;读,写,写回都不能被外设中断

| cache读命中 |

从cache读数据 |

不访问AMBA ASB接口 |

-------------------- |

| cache读缺失 |

引起linefill |

访问一次AMBA ASB接口 |

-------------------- |

| cache写命中 |

更新cache数据并标识数据为脏数据 |

不访问AMBA ASB接口 |

在数据需要被换出或clean操作时才放入AMBA ASB 接口 |

| cache写缺失 |

-------------------- |

所有被写的数据被缓冲并随后出现在AMBA ASB接口 |

在数据被完整缓冲了CPU马上继续执行 |

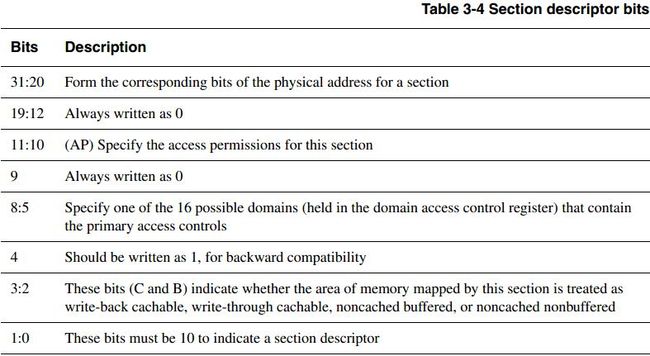

段描述符(sectiondescriptor)

1)格式:

2)位定义:

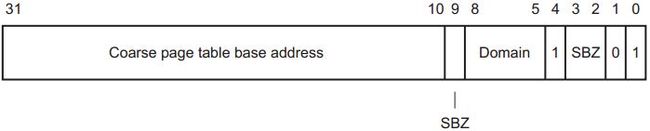

粗页表描述符(coarsepage table descriptor)

1)格式:

2)位定义:

细页表描述符(fine pagetable descriptor)

1)格式:

2)位定义:

页二级描述符(level twodescriptor)

二级描述符可为小页(small page),大页(large page),微小页(tiny page)和无效(invalid)4种,

大页 : 提供64KB大小的内存块基址

小页 : 提供4KB大小的内存块基址

微小页: 提供1BK大小的内存块基址

注意:

在粗页表里: 对于大页描述符必须在16个连续的记录项里被重复,而小页则每一个记录项对应一个描述符.

在细页表里: 对于大页描述符必须在64个连续的记录项里被重复,而小页描述符必须在4个连续的记录项里被重复,而微小页描述符则每一个记录项对应一个描述符.

1)格式:

注意: 微小页不支持子页访问权限(subpage permissions),因为1K已经是最小访问单元了.所以在页二级描述符中只有一个访问权限位.

2)位定义:

段转换(Translatingsection)过程:

(注:转换前必须检测一级描述符的权限)

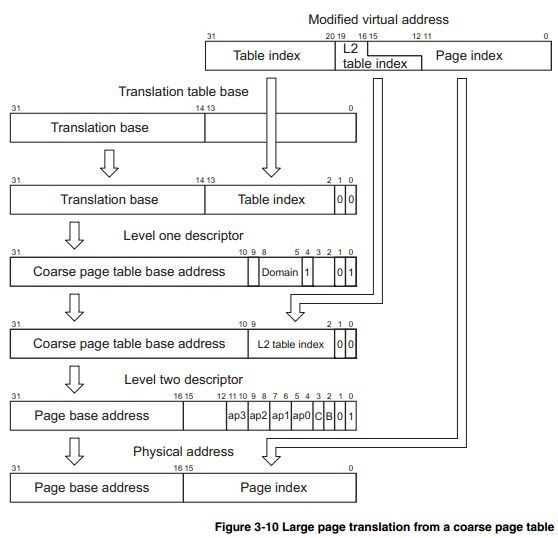

大页转换(Translating large page)过程:

小页转换(Translating small page)过程:

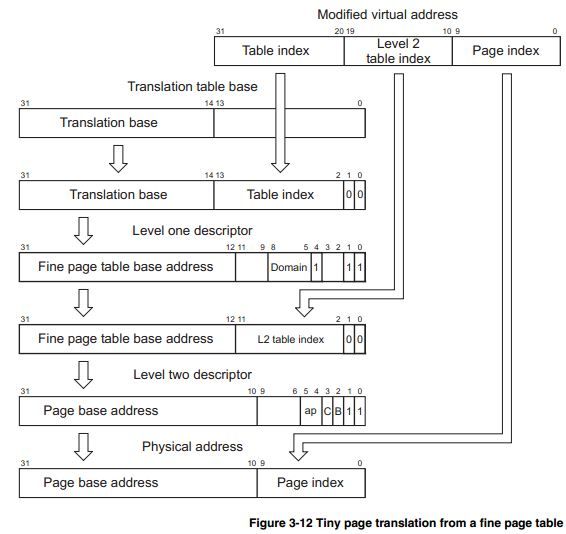

微小页转换(Translating tiny page)过程:

注:

在上面介绍了使用MMU进行地址映射的时候有段映射,大页,小页,微小页.分成这样是主要是为了什么呢?在怎么映射都最大达到4G,按照我自己的理解是为了控制访问权限的最小单元.

在段映射 : AP的最小作用单元为1M

在大页映射里 : AP的最小作用单元为16K

在小页映射里 : AP的最小作用单元为1K

在微小页里 : AP的最小作用单元也为1K但是微小页不支持子页访问权限设置

根据应用的需要,我们可以把我们期待大小的区域设为特定的访问权限(比如在特权模式下才能访问,或者用户模式下也能访问…)

对于二级查表的,二级页表基地址也必须是物理地址。

关于子页(subpages)的那点事

我们可以为小页or大页的子页定义访问权限.如果在页转换期间,一张小页or大页有一个不同访问权限的子页,那么只往TLB写入子页的访问权限,而当子页的访问权限都跟小页or大页的一致,那么小页or大页访问权限会被写入TLB.

当我们使用子页权限,并且页记录项已经是(invalidated)了,那么我们必须独个的使4个子页无效.

MMU和CPU异常

MMU会产生以下几种异常:

1)对齐异常(只在数据访问期间)

2)转换异常

3)域异常

4)权限异常

另外还有外部系统引起的外部异常.

对齐异常检测可以通过CP15 register 1的A bit来设置.不管MMU是否使能,对对齐异常检测都没有影响. 而转换,域和权限异常只在MMU使能情况下才会出现.

Faultstatus registers(FSR)

在数据异常情况下,MMU设置一个4-bit 的值,FS[3:0],只能是4个被编码了的domain数.

Domain access control

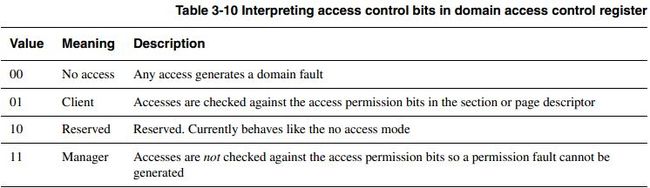

MMU的访问情况首先是通过使用domains来控制 , 由16个domains并且每个由2-bit区域来定义,两种类型的使用者被支持,客户和管理.domains被定义在domainaccess control寄存器.,下图演示了这个寄存器:

以下为在domain access control寄存器里的access control bits的取值及说明:

下图演示了AP bits 和它们是如何依赖于S 和 R bits(control register bits 8 和 9)

MMU用于检查访问异常的顺序如下图示:

Alignment fault

如果alignment fault被使能(A bit in CP15 register 1 set) , MMU产生一个alignmentfault 在word access时出现地址不是word-aligned , 或者在halfword access时出现地址不是halfword-aligned , 不管MMU是否使能 .

Translation fault

1)Section Translationfault : 当一级描述符被标识为invalid(描述符的bits[1:0]=00)的时候会产生 .

2)page Translationfault : 当一级描述符被标识为invalid(描述符的bits[1:0]=00)的时候会产生 .

Domain fault

1)Section Translation fault : 一级描述符保存一个4-bit 的区域,用于选择16个 2-bit的domains access control register中的一个. 指定的domain用于检查访问权限.这个动作在一级描述符被返回是执行.

2)page Translation fault : 一级描述符保存一个4-bit 的区域,用于选择16个 2-bit的domains access control register中的一个. 指定的domain用于检查访问权限.这个动作在一级描述符被返回是执行.

Permission fault

假如2-bit的domain 域返回01(client), 那么AP将会被进行.

1)Section : 如果一级描述符定义了段映射访问, 描述符的AP bits决定了访问是否允许,而且必须依赖S和R bits(control register bit 8 and 9)

2)Large page or small page : 如果一级描述符定义了页映射访问并且二级描述符是用于large or small page , 将有4个AP(ap3~ap0)被指定. 每一个对应1/4的页.

3)Tiny page : 如果一级描述符定义了页映射访问并且二级描述符是用于tiny page , 那么二级描述符的AP bits决定访问是否允许就像段访问一样.

ICache

ARM920T包含了一个16KB的ICache。这个ICache由32个字节的512行组成。可以通过选择random或者rount-robin算法来覆盖已存在的指令通过RR bit(CP15register 1 , bit 14)。

在ICache里的指令可以被上锁,防止这条指令被一次linefill(我的理解是一次行写入,用于添加或者更新ICache里面的条目)覆写。这个操作我们可以通过以下图示来理解ICache:

使能和禁止ICache

在复位的时候,ICache条目都是无效的并且ICache是禁止的。我们可以通过往Icrbit里写1来使能ICache,并且通过写0来禁止。

当Icache禁止时,Cache条目被忽略并且所有指令获取被单独非序列性访问通过AMBA ASB接口。ICache通常配合着MMU使用。在这个情况下MMU转换表描述符的Ctt位指明了一个区域内存是否可缓存。

当Cache在之前使能的情况下被禁止,所有的cache条目被忽略。所有的指令获取跟上面一样并且cache不会被更新。如果cache重新被使能了,那它的条目项不会被改变。如果内容跟主存里的不一致了,我们需要在重新使能ICache之前invalidate ICache。

如果cache使能而MMU禁止,所有的指令获取被认为是可缓存的。并且没有保护检查,物理地址只被映射为MVA供cache来寻找相应内容。

我们可以同时使能MMU和ICache通过使用一个MCR指令写入1到CP15 register 1 的M bit和Icr bit 。

ICache 操作

为了提高执行效率,我们必须在复位之后尽可能快的使能ICache。

假如ICache被使能了,那么每一次的指令获取都会使得ICache查询被执行:

(1)如果所要求的指令在ICache被找到了,这次查询被称为cache hit(cache命中)。如果指令获取是cachehit并且Ctt=1(指明这个内存区域是可缓存的),那么指令被返回给CPU core。

(2)如果找不到,这次查询被称为cache miss(cache缺失)。如果是cache miss并且Ctt=1,那么8-word linefill会被执行,或许会替换某一条记录项。被替换的记录项,称为victom。这个victom是通过使用random算法或者round-robin算法在没有上锁的记录项里选出来的。

假如Ctt=0,表明这个内存区域是不允许缓存的,所以一个单一的非序列性的内存访问出现在AMBA ASB接口上。