I2C总线原理总结

1.I2C总线描述

I2C总线就Philips公司推出的串行总线标准(为二线制)。总线上扩展的外围器件及外设接口通过总线寻址,就具备总线仲裁和高低速设备同步等功能的高性能多主机总线。

2.I2C总线原理SDA 串行数据线

SCL 串行时钟线

可发送接收数据

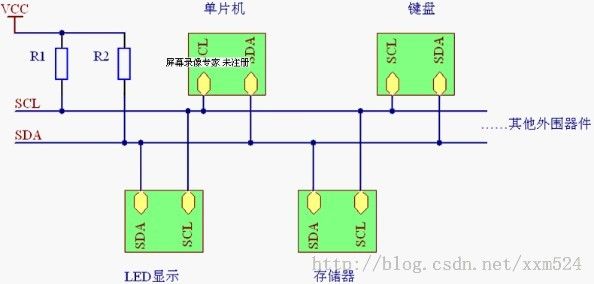

所有挂接在I2C总线上的器件和接口电路都应具有I2C总线接口,且所有的SDA/SCL同名端相连。总线上所有器件要依靠SDA发送的地址信号寻址,不需要片选线。

3.I2C总线优点

组成系统结构简单,芯片管脚数量少,无需片选信号;

I2C上的所有设备的SDA,SCL引脚必须外接上拉电阻。

4.典型的I2C总线系统结构

5.I2C总线器件的寻址方式主器件在进行数据传输前需要通过寻址,选择需要通信的从器件。

I2C总线上所有的外围器件都需要有唯一的7位地址;

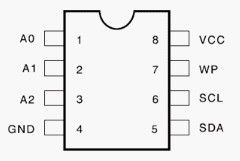

器件地址:4位,是I2C器件固有的地址编码,期间出厂时就已经给定,不可更改,如24C08 为1010。

引脚地址:3位,是由I2C总线外围器件的地址引脚(A2, A1, A0)决定,根据其在电路中接电源正极、接地或悬空的不同,形成不同的地址代码。、

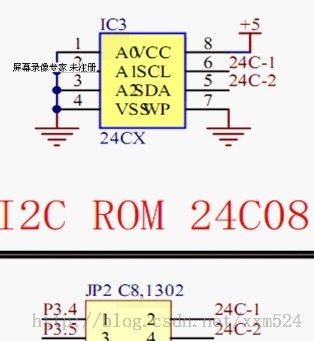

6.I2C总线接口EEPROM存储器AT24C08

7.C51模拟I2C总线协议典型的51系列单片机没有I2C总线接口,需要程序模拟I2C总线数据传输协议。

8.I2C总线数据操作

在I2C总线上,数据是伴随着时钟脉冲,一位一位地传送的,数据位由高到低传送,每位数据占一个时间脉冲。

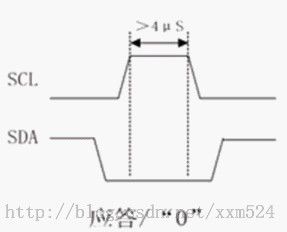

1)开始信号

时钟线SCL为高电平期间,数据SDA上高电平向电平变化的下降沿信号。起始信号出现后,才可以进行后续的I2C总线寻址或数据传输。

编程算法:

SCL = 1; SDA = 1; 延时大于4.7us SDA = 0; 延时大于4us SCL= 0; //SCL为低电平时,SDA上数据才允许变化

2)终止信号

时钟线SCL为高电平期间,数据线SDA上低电平到高电平变化的上升沿信号。终止信号一出现,所有的I2C总线操作都结束,并释放总线控制权。

编程算法:

SCL = 1; SDA = 0; 延时大于4us SDA = 1; //SDA的上升沿被认为是结束信号 延时大于4.7us SDA = 0; SCL = 0;

3) 应答信号

I2C总线数据传送时,一个字节数据传送完毕后都需要由朱期间产生应答信号。主器件在第9个(传完1个字节的数据)时钟上释放数据总线SDA,使其处于高电平状态,此时从 期间输出低电平拉低数据总线SDA为应答信号。

编程算法:

bit ack_bit; SDA = 1; //应在时钟脉冲的高电平期间(SCL=1)释放SDA线,以让SDA线转由接收设备控制 延时2个时钟脉冲 SCL = 1; 延时大于4us ack_bit = SDA; //接收设备向SDA送电平表示是应答信号,已经接收到一个字节;若送高电平,表示没有接收到,传送异常,结束发送 SCL = 0;

9.I2C总线接口EEPROM操作流程(24C08)

(主发送从接受)

1) 主器件产生开始信号

2) 发送第一个字节为控制字节(前七位是从器件的地址片选信号,最低位是数据传送方向,高电平为读从器件,低电平为写从器件)

3) 发送一个选择从器件片内地址的字节,来决定开始读写数据的起始地址

4) 发送数据,可以是单字节也可以是一组数据

5) 从器件每接收到一个字节后,都返回一个应答信号

6) 主器件在应答时钟周期高电平期间释放SDA线(SDA上升沿,即终止信号),转由从器件控制,从器件在这个时钟周期的高电平期间必须拉低SDA线,并视之为低电平,作为有效的应答信号