基于LDPC的下一代SSD控制器中的软解码

基于LDPC的下一代SSD控制器中的软解码

作者: Stephen Bates

简介

我的上一篇博文中,讨论了如何控制低密度奇偶校验(LDPC)纠错码的参数来管理与固态盘(SSD)读相关的延迟。然而,其中只谈及了与单次LDPC代码字相关的迭代。本篇博文中,我们研究一下,在最初解码失败时的情况,以及如何利用软信息来恢复SSD上的数据。

硬数据解码与软数据解码

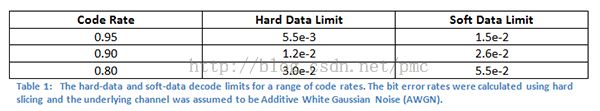

1948年十月,ClaudeShannon发表了一篇学术论文“有关通信的数学理论”,开启了信息理论学科的先河。由于文中的理论定义了一个任何纠错码均无法逾越的性能界限,因此今天依然普遍用于鉴定纠错码的优劣。有意思的一点是,对任一通道而言,都存在着两个界限,一个针对硬数据解码,另一个则用于软数据解码。下面表一中给出了若干用例。

对NAND闪存进行读操作时,通常只会得到与闪存上数据相关的1、0等。由于此时无从得知这些0和1中哪些是有效数据,哪些是可疑数据(有人就此作了不少文章,但就本文而言,先假设此言为真),因此,对此数据进行的初次LDPC解码是基于硬数据。在此情况下,初次解码的性能局限为表一中第二列所示。

NAND闪存中的LDPC及软数据解码

如果假设硬数据LDPC解码失败,对此SSD而言,就存在多种选择。一是可以决定返回一个“不可恢复的读错误”,通知用户数据已经永久丢失,而这是终端用户很不乐意看到的。如果此SSD有一个内部RAID系统,还可以试图利用该系统来恢复用户数据。然而,LDPC带来了第三种选择,即软化数据,再尝试进行软数据LDPC解码。请注意,这第三种选择对于采用较为低级的纠错机制(如BCH代码)的控制器而言并不存在。该选择将SSD的性能局限从表一中第二列移至第三列,使得SSD可以在更为嘈杂的环境中运作。

我习惯于将软数据LDPC解码看作三个部分:

1. 重读策略

2. 软数据构建

3. 软LDPC解码

下面来顺次研究这三个部分。

重读策略

重读策略包括以能够辅助软数据构建的方式来读出闪存中一个或多个部分。不论是就闪存读出的部分还是如何进行读操作而言,均有多种选择。研究过信息理论的读者们,我们的目标是将读出数据及原始硬数据两方面的信息均最大化,从而产生出尽可能好的软数据。下面列举若干重读策略的用例:

1. 读出的部分与原始硬数据相同,但是采用了NAND内部一组不同的读阈值电压。

2. MLCNAND中,读出的部分与原始部分共享相同的字线。

3. 读出与主要干扰器相对应的部分。该部分在编程时,对原始硬数据部分的干扰效应最为强烈。

上述三种重读策略各有优缺点,如有需要,三者其实可以结合起来!不过要记住,每次读取闪存都将导致延迟增加!

软数据构建

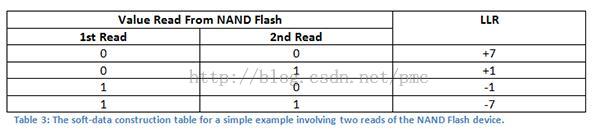

重读策略中每次读都会返回与之相关的0和1的数据——虽然在更为先进的NAND中存在略为改善的多位读,本博文将不对此进行讨论——因此,闪存的每次读取都给我们提供了更多的物理信息,而我们所需要进行的是将这些物理的0和1映射成LDPC解码中的软信息。该映射需要对NAND闪存及采用的LDPC代码具备充分的认知。

下面用一个非常简单的例子来进行说明。对于硬数据解码,可以采用一种非常简单的映射,将闪存中的0和1 转化为LDPC解码器能够消化的信息。我们将该映射的结果称为对数概率比(LLR)。表二中给出了此映射。

现在,假设重读策略中包含有一次额外的读。那么,我们的软数据构建就可能如表三所示。

软LDPC 解码

软数据解码中最后一个步骤是将代码字中每一位的LLR传入LDPC解码器逻辑。期望实现的解码比原有的硬数据解码更为有效,并且SSD能够返回用户数据,甚而可能将该数据移至SSD中较为安全的部分,遇到下一次数据请求时可以更为便利地予以恢复。

LDPC 白皮书

过去几篇博文中,我探讨了LDPC可能对SSD中NAND闪存使用造成的若干影响。读者如果对此感兴趣,想了解更深入的信息,我们提供了一篇内容更为详实的白皮书,欢迎大家下载并提供反馈!

博文预告

本文是有关LDPC代码的系列博文中最后一篇。后续将载出新系列博文,探究数据中心中如何利用PCIe连接的NVM设备来提升性能,敬请期待!PMC公司将在 2014闪存峰会上就此及其他若干论题展示相关研究成果。感兴趣的读者,欢迎光临#416展位或参与我们的技术论坛!