W5300E01-ARM用户手册版本1.0(二)

本用户手册将为大家介绍W5300E01-ARM,它是W5300基于ARM920T的功能评估测试板。共分为9大板块,包括有概述、产品说明、硬件设计向导、板操作、配置开发环境、Linux 内核补丁与编译、根文件系统、启动程序及附录等。上一篇博文里我们为大家介绍了概述、产品说明及硬件设计向导的部分内容,现在我们为大家介绍第二部分包括硬件设计向导的剩余部分,希望对大家有帮助。

第一部分在这里:http://blog.csdn.net/wiznet2012/article/details/7816909

3.2块描述

W5300E01-ARM可以被分为以下几部分。

S3C2410A 系统模块

SDRAM

NAND闪存ROM

WIZ830MJ模块

字符 LCD

RS-232C 串口

USB 主机 / 设备端口

JTAG 接口

编译用的LED & Tact开关

扩展端口接口

功率模块

3.2.1 S3C2410A 系统模块

为了能够支持NAND闪存的引导装载程序,三星S3C2410A处理器包含了被称为Steppingstone的SRAM缓存。

W5300E01-ARM平台在启动存储器中使用NAND闪存ROM,通过下拉S3C2410A的OM0和OM1引脚接地来实现NAND闪存初始化启动。

由于上电复位IC是为用户手动复位安装的,可以在板子运行的时候通过使用tact开关进行手动复位。

3.2.2 SDRAM

64MB的SDRAM用于S3C2410A处理器的外部存储器,并为操作系统的运行和用户应用提供足够的空间。

3.2.3 NAND 闪存 ROM

64MB的NAND闪存ROM用于S3C2410A的外部程序存储器和非易失性存储设备。基本上,Linux启动程序、内核和文件系统都在这个闪存ROM中进行编程。另外,在这个闪存ROM中还嵌入了web服务器(利用W5300 TCP/IP),额外的空间可以提供给用户数据字段。

3.2.4 WIZ830MJ模块

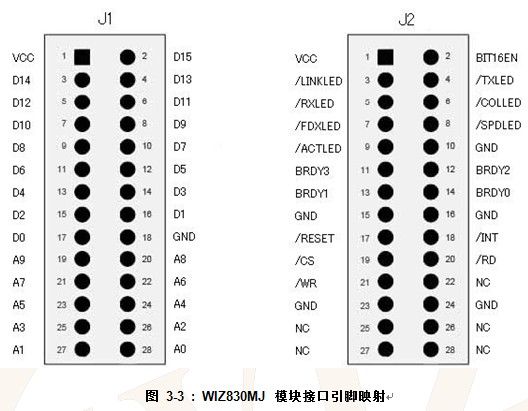

WIZ830MJ是具有W5300 TCP/IP芯片和RJ-45接口(具有变压器)的以太网模块。WIZ830MJ和底板是通过高度为2.54mm的接口连接,如<表 3>所示。

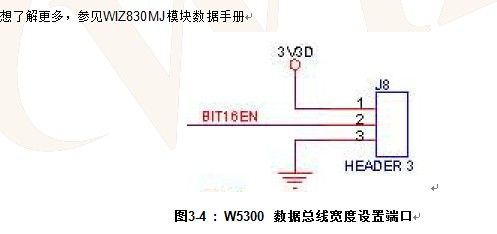

使用J8接口,可以配置WIZ830MJ中W5300的数据总线宽度;使用2个引脚跳线连接J8的引脚1和引脚2,可以配置16位数据总线宽度;通过连接引脚2和引脚3,可以配置8位总线宽度。

3.2.5 RS-232C 串口

S3C2410A处理器支持的3个UARTs信道,RS-232C串口是UART 0信道的接口,剩下的2个信道通过扩展端口用于扩展

W5300E01-ARM平台基本上使用9引脚的DSUB阳极类型接口。

3.2.6 USB主机 / 设备端口

我们为测试USB主机提供A类型主机接头,为S3C2410支持的USB设备(子设备)接口提供Mini类型设备接头。

因为Linux基本上支持USB主机驱动,就可以通过连接W5300E01-ARM平台测试各种USB设备。通过USB设备驱动,Linux支持设备和PC之间的连接。

3.2.7 JTAG 接口

通过JTAG接口,就可以将启动向导写入NAND闪存ROM中,通过JTAG编译设备可以对接口进行编译。如果安装了20引脚的JTAG接头,一般的JTAG设备连接都没有问题。

3.2.8调试用的LED和Tact 开关

使用2个LED和2个Tact开关连接EINT/GPIO,可以进行简单的编译。

3.2.9字符 LCD

字符LCD用于显示调试状态和系统状态。

字符LCD接口(J7)的引脚描述如下所示。

| 引脚号 |

W5300E01-ARM B/D引脚名称 / LCD 引脚名称 |

作用 |

描述 |

| 1 |

GND / VSS |

|

信号接地 |

| 2 |

5V / VDD |

I |

LCD供电 |

| 3 |

V0 / V0 |

I |

LCD驱动电压 |

| 4 |

A1 / RS |

I |

数据 / 指令寄存器选择 |

| 5 |

A2 / RW |

I |

读/写 |

| 6 |

LCD_E / E |

I |

可用信号,开始数据读/写 |

| 7~14 |

D0 / DB0~D7 / DB7 |

I/O |

数据总线 |

| 15 |

5V / LED A |

O |

LED 阳极供电+ |

| 16 |

GND / LED K |

O |

LED 阴极,接地 0V |

表3-1 : LCD 引脚描述

安装在3.3V(I/O接口电压电平)和5V(LCD操作电压电平)之间可以稳定操作74LBC4245双向电平移位器,可以通过双向缓冲器检测LCD的Busy标志位让操作更可靠。

低活性芯片通过逆变器选择S3C2410A的信号位转换成高活性,并用于LCD可用信号。

想了解更多LCD的操作细节,参见LCD数据手册(LC1624(R2).pdf)。

3.2.10电源框图

通过5V/2A的电源适配器给W5300E01-ARM供电,内部电源为5V、3V和1.8V。想了解每个电源的详细情况,参见原理图或‘3.1.2 电源框图’。

通过电源开关(SW1)可以控制5V电源适配器的输入电压,为了防止电压过大造成模块损坏,我们在模块中应用了Poly-Fuse(F1)。

3.2.11扩展端口接口

设计扩展端口接口是为了方便用户添加S3C2410A处理器提供的功能(W5300E01-ARM不提供)。

| 功能 |

引脚号 |

引脚名称 |

作用 |

描述 |

| J3 接口 |

||||

| 功率 |

1 |

3V3D |

|

3.3V 系统电压 |

| 3 |

5V0D |

|

5V系统电压 |

|

| 39 |

GND |

|

系统接地 |

|

| 系统 数据总线 |

2,4,6,8,10,12, 14,16,18,20,22, 24,26,28,30,32 |

D0 ~ D15 |

IO |

数据总线 |

| 系统 地址总线 |

5,7,9,11,13,15, 17,19,21,23,25, 27,29,31,33,35 |

A0 ~ A15 |

O |

地址总线 |

| 系统 控制信号 |

34 |

nGCS0 |

O |

一般芯片选择0 |

| 36 |

nOE |

O |

可用输出 |

|

| 37 |

nRESET |

I |

系统重置输入 |

|

| 38 |

nWE |

O |

可写 |

|

| 40 |

EINT0 |

IO |

外部中断请求/ GPIO |

|

| J4 接口 |

||||

| 电压 |

1 |

3V3D |

|

3.3V 系统电压 |

| 3 |

5V0D |

|

5V 系统电压 |

|

| 39 |

GND |

|

系统接地 |

|

| 38 |

VDDA_ADC |

|

3.3V ADC 电压 |

|

| 40 |

VSSA_ADC |

|

ADC接地 |

|

| DMA |

2 |

nXDACK0 |

O |

外部存储器认可 |

| 4 |

nXDREQ0 |

I |

外部DMA请求 |

|

| I2S接口 |

5 |

I2SLRCK |

IO |

I2S总线信道选择时钟 |

| 7 |

I2SSCLK |

IO |

I2S总线串口时钟 |

|

| 9 |

CDCLK |

O |

CODEC 系统时钟 |

|

| 11 |

I2SSDI |

I |

I2S总线串口数据输入 |

|

| 13 |

I2SSDO |

O |

I2S总线串口数据输出 |

|

| UART接口 |

10 |

TXD1 |

O |

UART1 数据发送端 |

| 12 |

RXD1 |

I |

UART1 数据接收端 |

|

| 14 |

TXD2 |

O |

UART2 数据发送端 |

|

| 16 |

RXD2 |

I |

UART2 数据接收端 |

|

| SD卡接口 |

15 |

SDCLK |

O |

SD 时钟 |

| 17 |

SDCMD |

IO |

SD 命令 |

|

| 19,21,23,25 |

SDDAT0 ~ SDDAT3 |

IO |

SD 接受 / 发送数据 |

|

| SPI接口 |

24 |

SPICLK0 |

IO |

SPI 时钟 |

| 26 |

SPIMOSI0 |

IO |

SPI 主数据输出线 |

|

| 28 |

SPIMISO0 |

IO |

SPI 主数据输入线 |

|

| 30 |

EINT10 / nSS0 |

I |

SPI 芯片选择 (子模式) |

|

| I2C接口 |

27 |

IICSDA |

IO |

I2C 总线数据 |

| 29 |

IICSCL |

IO |

I2C 总线时钟 |

|

| ADC |

32 |

AIN1 |

AI |

ADC 电压输入1 |

| 34 |

AIN0 |

AI |

ADC 电压输入0 |

|

| 36 |

Vref |

AI |

ADC 参考电压 |

|

| GPIO/ 中断 |

18 |

EINT6 |

IO |

外部中断请求 / GPIO |

| 37 |

EINT1 |

IO |

外部中断请求 / GPIO |

|

| 系统 控制信号

|

6 |

nXBREQ |

I |

总线保持请求 |

| 8 |

nXBACK |

O |

总线保持认可 |

|

| 20 |

PWREN |

|

|

|

| 22 |

nRSTOUT |

|

|

|

| 31 |

nWAIT |

|

|

|

| 33 |

nGCS4 |

|

通用芯片选择 4 |

|

| 35 |

nGCS5 |

|

通用芯片选择 5 |

|

| J5 接口 |

||||

| 电压 |

1 |

3V3D |

|

|

| 3 |

5V0D |

|

|

|

| 39 |

GND |

|

|

|

| LCD 数据总线 |

5,7,9,11,13,15, 17,19,21,23,25, 27,29,31,33,35, 37,2,4,6,8,10, 12,14 |

VD0 ~ VD23 |

|

STN / TFT / SEC TFT LCD 数据总线 |

| LCD 控制信号 |

16 |

LEND |

|

行结束信号 |

| 18 |

VCLK |

|

LCD 时钟信号 |

|

| 20 |

VLINE |

|

LCD 行信号 |

|

| 22 |

VM |

|

虚拟机行电压和列电压极性交替 |

|

| 24 |

VFRAME |

|

LCD 帧信号 |

|

| 26,28,30 |

LCDVF0 ~ LCDVF2 |

|

特定的 TFT LCD (OE/REV/REVB)定时控制信号 |

|

| GPIO 接口 / 中断 |

32 |

EINT12 |

IO |

外部中断请求 / GPIO |

| 34 |

EINT23 |

IO |

外部中断请求 / GPIO |

|

| 36 |

EINT22 |

IO |

外部中断请求 / GPIO |

|

| 38 |

EINT21 |

IO |

外部中断请求 / GPIO |

|

| 40 |

EINT20 |

IO |

外部中断请求 / GPIO |

|

表3-2 : 扩展板接口引脚描述

3.3原理图

3.3.1 W5300E01-ARM底板原理图

参见光盘中的 ‘W5300E01-ARM_V1.0.DSN’ 文件。

3.3.2 WIZ830MJ模块原理图

参见光盘中的 ‘WIZ830MJ_R10.DSN’ 文件。

3.4零件清单

3.4.1 W5300E01-ARM 零件清单

参见光盘中的 ‘W5300E01-ARM V1.0 PARTLIST.PDF’文件。

3.4.2 WIZ830MJ模块零件清单

参见光盘中的 ‘WIZ830MJ V1.0 PARTLIST.PDF’文件。

3.5实体规格

3.5.1开发板尺寸

| 符号 |

尺寸 (mm) |

符号 |

尺寸 (mm) |

| A |

118.00 |

I |

14.65 |

| B |

12.10 |

J |

4.00 |

| C |

3.70 |

K |

4.00 |

| D |

4.00 |

L |

3.70 |

| E |

4.00 |

M |

4.00 |

| F |

3.30 |

N |

4.00 |

| G |

14.65 |

O |

4.00 |

| H |

97.00 |

P |

4.00 |

图3-6 : W5300E01-ARM开发板尺寸

想了解更多WIZ830MJ模块开发版尺寸的信息,请参考WIZ830MJ数据手册。