dsp--28335的cmd文件学习(二)

今天调试28335发现出现了错误error: can't allocate .ebss, size 00000400 (page 1) in RAMM1 (avail: 00000380),网上找答案都是改Stack Size,改成小于1024,我一看我早就改了,于是静下心来找答案,发现ebss是未初始化的变量存放的空间,于是在程序中将一些以前调试而没有删除的变量删除了,编译就果断ok了,问题是解决了,但是觉得自己关于cmd文件的学习太过草率了,于是,学习一些28335的cmd文件。ps:在去年的笔记中也发现中发现了error: can't allocate .text太大的原因,但是的解决办法是将一些多余的c文件删除就行了,但是还不知道为什么,现在可以解释了。

转载请注明;来自xzyfeixiang的博客:http://blog.csdn.net/xzyiverson

首先,我们必须要知道一些基本的概念,然后再分析,这里引用书本的一些话。

28335的cmd文件有两个,一个是关于寄存器的,一个是关于程序的。

关于寄存器的cmd文件,包括两部分,一部分是section,这部分是定义的寄存器文件,一部分是map,就是为那些寄存器文件分配地址:

MEMORY

{

PAGE 0: /* Program Memory */

PAGE 1: /* Data Memory */

DEV_EMU : origin = 0x000880, length = 0x000180 /* device emulation registers */

FLASH_REGS : origin = 0x000A80, length = 0x000060 /* FLASH registers */

CSM : origin = 0x000AE0, length = 0x000010 /* code security module registers */

ADC_MIRROR : origin = 0x000B00, length = 0x000010 /* ADC Results register mirror */

XINTF : origin = 0x000B20, length = 0x000020 /* external interface registers */

CPU_TIMER0 : origin = 0x000C00, length = 0x000008 /* CPU Timer0 registers */

CPU_TIMER1 : origin = 0x000C08, length = 0x000008 /* CPU Timer0 registers (CPU Timer1 & Timer2 reserved TI use)*/

CPU_TIMER2 : origin = 0x000C10, length = 0x000008 /* CPU Timer0 registers (CPU Timer1 & Timer2 reserved TI use)*/

PIE_CTRL : origin = 0x000CE0, length = 0x000020 /* PIE control registers */

PIE_VECT : origin = 0x000D00, length = 0x000100 /* PIE Vector Table */

DMA : origin = 0x001000, length = 0x000200 /* DMA Rev 0 registers */

MCBSPA : origin = 0x005000, length = 0x000040 /* McBSP-A registers */

MCBSPB : origin = 0x005040, length = 0x000040 /* McBSP-B registers */

ECANA : origin = 0x006000, length = 0x000040 /* eCAN-A control and status registers */

ECANA_LAM : origin = 0x006040, length = 0x000040 /* eCAN-A local acceptance masks */

ECANA_MOTS : origin = 0x006080, length = 0x000040 /* eCAN-A message object time stamps */

ECANA_MOTO : origin = 0x0060C0, length = 0x000040 /* eCAN-A object time-out registers */

ECANA_MBOX : origin = 0x006100, length = 0x000100 /* eCAN-A mailboxes */

ECANB : origin = 0x006200, length = 0x000040 /* eCAN-B control and status registers */

ECANB_LAM : origin = 0x006240, length = 0x000040 /* eCAN-B local acceptance masks */

ECANB_MOTS : origin = 0x006280, length = 0x000040 /* eCAN-B message object time stamps */

ECANB_MOTO : origin = 0x0062C0, length = 0x000040 /* eCAN-B object time-out registers */

ECANB_MBOX : origin = 0x006300, length = 0x000100 /* eCAN-B mailboxes */

EPWM1 : origin = 0x006800, length = 0x000022 /* Enhanced PWM 1 registers */

EPWM2 : origin = 0x006840, length = 0x000022 /* Enhanced PWM 2 registers */

EPWM3 : origin = 0x006880, length = 0x000022 /* Enhanced PWM 3 registers */

EPWM4 : origin = 0x0068C0, length = 0x000022 /* Enhanced PWM 4 registers */

EPWM5 : origin = 0x006900, length = 0x000022 /* Enhanced PWM 5 registers */

EPWM6 : origin = 0x006940, length = 0x000022 /* Enhanced PWM 6 registers */

ECAP1 : origin = 0x006A00, length = 0x000020 /* Enhanced Capture 1 registers */

ECAP2 : origin = 0x006A20, length = 0x000020 /* Enhanced Capture 2 registers */

ECAP3 : origin = 0x006A40, length = 0x000020 /* Enhanced Capture 3 registers */

ECAP4 : origin = 0x006A60, length = 0x000020 /* Enhanced Capture 4 registers */

ECAP5 : origin = 0x006A80, length = 0x000020 /* Enhanced Capture 5 registers */

ECAP6 : origin = 0x006AA0, length = 0x000020 /* Enhanced Capture 6 registers */

EQEP1 : origin = 0x006B00, length = 0x000040 /* Enhanced QEP 1 registers */

EQEP2 : origin = 0x006B40, length = 0x000040 /* Enhanced QEP 2 registers */

GPIOCTRL : origin = 0x006F80, length = 0x000040 /* GPIO control registers */

GPIODAT : origin = 0x006FC0, length = 0x000020 /* GPIO data registers */

GPIOINT : origin = 0x006FE0, length = 0x000020 /* GPIO interrupt/LPM registers */

SYSTEM : origin = 0x007010, length = 0x000020 /* System control registers */

SPIA : origin = 0x007040, length = 0x000010 /* SPI-A registers */

SCIA : origin = 0x007050, length = 0x000010 /* SCI-A registers */

XINTRUPT : origin = 0x007070, length = 0x000010 /* external interrupt registers */

ADC : origin = 0x007100, length = 0x000020 /* ADC registers */

SCIB : origin = 0x007750, length = 0x000010 /* SCI-B registers */

SCIC : origin = 0x007770, length = 0x000010 /* SCI-C registers */

I2CA : origin = 0x007900, length = 0x000040 /* I2C-A registers */

CSM_PWL : origin = 0x33FFF8, length = 0x000008 /* Part of FLASHA. CSM password locations. */

}

SECTIONS

{

PieVectTableFile : > PIE_VECT, PAGE = 1

/*** Peripheral Frame 0 Register Structures ***/

DevEmuRegsFile : > DEV_EMU, PAGE = 1

FlashRegsFile : > FLASH_REGS, PAGE = 1

CsmRegsFile : > CSM, PAGE = 1

AdcMirrorFile : > ADC_MIRROR, PAGE = 1

XintfRegsFile : > XINTF, PAGE = 1

CpuTimer0RegsFile : > CPU_TIMER0, PAGE = 1

CpuTimer1RegsFile : > CPU_TIMER1, PAGE = 1

CpuTimer2RegsFile : > CPU_TIMER2, PAGE = 1

PieCtrlRegsFile : > PIE_CTRL, PAGE = 1

DmaRegsFile : > DMA, PAGE = 1

/*** Peripheral Frame 3 Register Structures ***/

McbspaRegsFile : > MCBSPA, PAGE = 1

McbspbRegsFile : > MCBSPB, PAGE = 1

/*** Peripheral Frame 1 Register Structures ***/

ECanaRegsFile : > ECANA, PAGE = 1

ECanaLAMRegsFile : > ECANA_LAM PAGE = 1

ECanaMboxesFile : > ECANA_MBOX PAGE = 1

ECanaMOTSRegsFile : > ECANA_MOTS PAGE = 1

ECanaMOTORegsFile : > ECANA_MOTO PAGE = 1

ECanbRegsFile : > ECANB, PAGE = 1

ECanbLAMRegsFile : > ECANB_LAM PAGE = 1

ECanbMboxesFile : > ECANB_MBOX PAGE = 1

ECanbMOTSRegsFile : > ECANB_MOTS PAGE = 1

ECanbMOTORegsFile : > ECANB_MOTO PAGE = 1

EPwm1RegsFile : > EPWM1 PAGE = 1

EPwm2RegsFile : > EPWM2 PAGE = 1

EPwm3RegsFile : > EPWM3 PAGE = 1

EPwm4RegsFile : > EPWM4 PAGE = 1

EPwm5RegsFile : > EPWM5 PAGE = 1

EPwm6RegsFile : > EPWM6 PAGE = 1

ECap1RegsFile : > ECAP1 PAGE = 1

ECap2RegsFile : > ECAP2 PAGE = 1

ECap3RegsFile : > ECAP3 PAGE = 1

ECap4RegsFile : > ECAP4 PAGE = 1

ECap5RegsFile : > ECAP5 PAGE = 1

ECap6RegsFile : > ECAP6 PAGE = 1

EQep1RegsFile : > EQEP1 PAGE = 1

EQep2RegsFile : > EQEP2 PAGE = 1

GpioCtrlRegsFile : > GPIOCTRL PAGE = 1

GpioDataRegsFile : > GPIODAT PAGE = 1

GpioIntRegsFile : > GPIOINT PAGE = 1

/*** Peripheral Frame 2 Register Structures ***/

SysCtrlRegsFile : > SYSTEM, PAGE = 1

SpiaRegsFile : > SPIA, PAGE = 1

SciaRegsFile : > SCIA, PAGE = 1

XIntruptRegsFile : > XINTRUPT, PAGE = 1

AdcRegsFile : > ADC, PAGE = 1

ScibRegsFile : > SCIB, PAGE = 1

ScicRegsFile : > SCIC, PAGE = 1

I2caRegsFile : > I2CA, PAGE = 1

/*** Code Security Module Register Structures ***/

CsmPwlFile : > CSM_PWL, PAGE = 1

关于寄存器的cmd文件没有什么很难理解的地方,关键是程序的cmd文件,要好好学习一下。

MEMORY

{

PAGE 0 :

/* BEGIN is used for the "boot to SARAM" bootloader mode */

/* BOOT_RSVD is used by the boot ROM for stack. */

/* This section is only reserved to keep the BOOT ROM from */

/* corrupting this area during the debug process */

BEGIN : origin = 0x000000, length = 0x000002 /* Boot to M0 will go here */

BOOT_RSVD : origin = 0x000002, length = 0x00004E /* Part of M0, BOOT rom will use this for stack */

RAMM0 : origin = 0x000050, length = 0x0003B0

RAML0 : origin = 0x008000, length = 0x001000

RAML1 : origin = 0x009000, length = 0x001000

RAML2 : origin = 0x00A000, length = 0x001000

RAML3 : origin = 0x00B000, length = 0x001000

ZONE6A : origin = 0x100000, length = 0x00FC00 /* XINTF zone 6 - program space */

CSM_RSVD : origin = 0x33FF80, length = 0x000076 /* Part of FLASHA. Program with all 0x0000 when CSM is in use. */

CSM_PWL : origin = 0x33FFF8, length = 0x000008 /* Part of FLASHA. CSM password locations in FLASHA */

ADC_CAL : origin = 0x380080, length = 0x000009

RESET : origin = 0x3FFFC0, length = 0x000002

IQTABLES : origin = 0x3FE000, length = 0x000b50

IQTABLES2 : origin = 0x3FEB50, length = 0x00008c

FPUTABLES : origin = 0x3FEBDC, length = 0x0006A0

BOOTROM : origin = 0x3FF27C, length = 0x000D44

PAGE 1 :

RAMM1 : origin = 0x000400, length = 0x000400 /* on-chip RAM block M1 */

RAML4 : origin = 0x00C000, length = 0x001000

RAML5 : origin = 0x00D000, length = 0x001000

RAML6 : origin = 0x00E000, length = 0x001000

RAML7 : origin = 0x00F000, length = 0x001000

ZONE6B : origin = 0x10FC00, length = 0x000400 /* XINTF zone 6 - data space */

}

SECTIONS

{

/* Setup for "boot to SARAM" mode:

The codestart section (found in DSP28_CodeStartBranch.asm)

re-directs execution to the start of user code. */

codestart : > BEGIN, PAGE = 0

ramfuncs : > RAML0, PAGE = 0

.text : > RAML1, PAGE = 0

.cinit : > RAML0, PAGE = 0

.pinit : > RAML0, PAGE = 0

.switch : > RAML0, PAGE = 0

.stack : > RAMM1, PAGE = 1

.ebss : > RAML4, PAGE = 1

.econst : > RAML5, PAGE = 1

.esysmem : > RAMM1, PAGE = 1

IQmath : > RAML1, PAGE = 0

IQmathTables : > IQTABLES, PAGE = 0, TYPE = NOLOAD

IQmathTables2 : > IQTABLES2, PAGE = 0, TYPE = NOLOAD

FPUmathTables : > FPUTABLES, PAGE = 0, TYPE = NOLOAD

DMARAML4 : > RAML4, PAGE = 1

DMARAML5 : > RAML5, PAGE = 1

DMARAML6 : > RAML6, PAGE = 1

DMARAML7 : > RAML7, PAGE = 1

ZONE6DATA : > ZONE6B, PAGE = 1

.reset : > RESET, PAGE = 0, TYPE = DSECT /* not used */

csm_rsvd : > CSM_RSVD PAGE = 0, TYPE = DSECT /* not used for SARAM examples */

csmpasswds : > CSM_PWL PAGE = 0, TYPE = DSECT /* not used for SARAM examples */

/* Allocate ADC_cal function (pre-programmed by factory into TI reserved memory) */

.adc_cal : load = ADC_CAL, PAGE = 0, TYPE = NOLOAD

}

也是分为两个部分,下面是段,上面是为那些段分配的地址,当然有些段在程序中比较大,但是给他分配的地址又不够,这个时候就报错了,这个时候需要修改程序或者修改cmd文件了,这样,大致的思路就清晰了。PAGE 0代表程序空间, PAGE 1代表数据空间,我们可以将一个大的空间分成两部分,然后将一些段放在这两部分空间里,但这两空间的总和不能超过原有的空间,上述是运行在ram的cmd文件,下面这个cmd文件我报错的cmd文件,对比一下就可以知道原因了。

MEMORY

{

PAGE 0: /* Program Memory */

/* Memory (RAM/FLASH/OTP) blocks can be moved to PAGE1 for data allocation */

ZONE0 : origin = 0x004000, length = 0x001000 /* XINTF zone 0 */

RAM_L0L1L2L3: origin = 0x008000, length = 0x004000 /* on-chip RAM */

OTP : origin = 0x380400, length = 0x000400 /* on-chip OTP */

ZONE6 : origin = 0x100000, length = 0x100000 /* XINTF zone 6 */

ZONE7A : origin = 0x200000, length = 0x00FC00 /* XINTF zone 7 - program space */

FLASHH : origin = 0x300000, length = 0x008000 /* on-chip FLASH */

FLASHG : origin = 0x308000, length = 0x008000 /* on-chip FLASH */

FLASHF : origin = 0x310000, length = 0x008000 /* on-chip FLASH */

FLASHE : origin = 0x318000, length = 0x008000 /* on-chip FLASH */

FLASHD : origin = 0x320000, length = 0x008000 /* on-chip FLASH */

FLASHC : origin = 0x328000, length = 0x008000 /* on-chip FLASH */

FLASHA : origin = 0x338000, length = 0x007F80 /* on-chip FLASH */

CSM_RSVD : origin = 0x33FF80, length = 0x000076 /* Part of FLASHA. Program with all 0x0000 when CSM is in use. */

BEGIN_FLASH : origin = 0x33FFF6, length = 0x000002 /* Part of FLASHA. Used for "boot to Flash" bootloader mode. */

CSM_PWL : origin = 0x33FFF8, length = 0x000008 /* Part of FLASHA. CSM password locations in FLASHA */

ADC_CAL : origin = 0x380080, length = 0x000009 /* Part of TI OTP */

IQTABLES : origin = 0x3FE000, length = 0x000b50 /* IQ Math Tables in Boot ROM */

IQTABLES2 : origin = 0x3FEB50, length = 0x00008c /* IQ Math Tables in Boot ROM */

FPUTABLES : origin = 0x3FEBDC, length = 0x0006A0 /* FPU Tables in Boot ROM */

ROM : origin = 0x3FF27C, length = 0x000D44 /* Boot ROM */

RESET : origin = 0x3FFFC0, length = 0x000002 /* part of boot ROM */

VECTORS : origin = 0x3FFFC2, length = 0x00003E /* part of boot ROM */

PAGE 1 : /* Data Memory */

/* Memory (RAM/FLASH/OTP) blocks can be moved to PAGE0 for program allocation */

/* Registers remain on PAGE1 */

RAMM0 : origin = 0x000000, length = 0x000400 /* on-chip RAM block M0 */

BOOT_RSVD : origin = 0x000400, length = 0x000080 /* Part of M1, BOOT rom will use this for stack */

RAMM1 : origin = 0x000480, length = 0x000380 /* on-chip RAM block M1 */

RAML4 : origin = 0x00C000, length = 0x001000 /* on-chip RAM block L4 */

RAML5 : origin = 0x00D000, length = 0x001000 /* on-chip RAM block L5 */

RAML6 : origin = 0x00E000, length = 0x001000 /* on-chip RAM block L6 */

RAML7 : origin = 0x00F000, length = 0x001000 /* on-chip RAM block L7 */

ZONE7B : origin = 0x20FC00, length = 0x000400 /* XINTF zone 7 - data space */

}

/**************************************************************/

/* Link all user defined sections */

/**************************************************************/

SECTIONS

{

/*** Code Security Password Locations ***/

csmpasswds : > CSM_PWL PAGE = 0

csm_rsvd : > CSM_RSVD PAGE = 0

/*** User Defined Sections ***/

codestart : > BEGIN_FLASH, PAGE = 0 /* Used by file CodeStartBranch.asm */

wddisable : > FLASHA, PAGE = 0

copysections : > FLASHA, PAGE = 0

/* Allocate IQ math areas: */

IQmath : > FLASHC PAGE = 0 /* Math Code */

IQmathTables : > IQTABLES, PAGE = 0, TYPE = NOLOAD

IQmathTables2 : > IQTABLES2, PAGE = 0, TYPE = NOLOAD

FPUmathTables : > FPUTABLES, PAGE = 0, TYPE = NOLOAD

/* Allocate DMA-accessible RAM sections: */

DMARAML4 : > RAML4, PAGE = 1

DMARAML5 : > RAML5, PAGE = 1

DMARAML6 : > RAML6, PAGE = 1

DMARAML7 : > RAML7, PAGE = 1

/* Allocate 0x400 of XINTF Zone 7 to storing data */

ZONE7DATA : > ZONE7B, PAGE = 1

/* Allocate ADC_cal function (pre-programmed by factory into TI reserved memory) */

.adc_cal : load = ADC_CAL, PAGE = 0, TYPE = NOLOAD

/* .reset is a standard section used by the compiler. It contains the */

/* the address of the start of _c_int00 for C Code. /*

/* When using the boot ROM this section and the CPU vector */

/* table is not needed. Thus the default type is set here to */

/* DSECT */

.reset : > RESET, PAGE = 0, TYPE = DSECT

vectors : > VECTORS PAGE = 0, TYPE = DSECT

/*** Uninitialized Sections ***/

.stack : > RAMM0 PAGE = 1

.ebss : > RAMM1 PAGE = 1

.esysmem : > RAMM1 PAGE = 1

/*** Initialized Sections ***/

.cinit : LOAD = FLASHA, PAGE = 0 /* can be ROM */

RUN = RAM_L0L1L2L3, PAGE = 0 /* must be CSM secured RAM */

LOAD_START(_cinit_loadstart),

RUN_START(_cinit_runstart),

SIZE(_cinit_size)

.const : LOAD = FLASHA, PAGE = 0 /* can be ROM */

RUN = RAM_L0L1L2L3, PAGE = 0 /* must be CSM secured RAM */

LOAD_START(_const_loadstart),

RUN_START(_const_runstart),

SIZE(_const_size)

.econst : LOAD = FLASHA, PAGE = 0 /* can be ROM */

RUN = RAM_L0L1L2L3, PAGE = 0 /* must be CSM secured RAM */

LOAD_START(_econst_loadstart),

RUN_START(_econst_runstart),

SIZE(_econst_size)

.pinit : LOAD = FLASHA, PAGE = 0 /* can be ROM */

RUN = RAM_L0L1L2L3, PAGE = 0 /* must be CSM secured RAM */

LOAD_START(_pinit_loadstart),

RUN_START(_pinit_runstart),

SIZE(_pinit_size)

.switch : LOAD = FLASHA, PAGE = 0 /* can be ROM */

RUN = RAM_L0L1L2L3, PAGE = 0 /* must be CSM secured RAM */

LOAD_START(_switch_loadstart),

RUN_START(_switch_runstart),

SIZE(_switch_size)

.text : LOAD = FLASHA, PAGE = 0 /* can be ROM */

RUN = RAM_L0L1L2L3, PAGE = 0 /* must be CSM secured RAM */

LOAD_START(_text_loadstart),

RUN_START(_text_runstart),

SIZE(_text_size)

}

看下M1分成了两个部分,ebss的部分当然就没有0x400了,这也是为什么会报错的原因了,这是学习cmd文件最基本的东西,要真正学好还有很长的一段距离,只能慢慢来了。

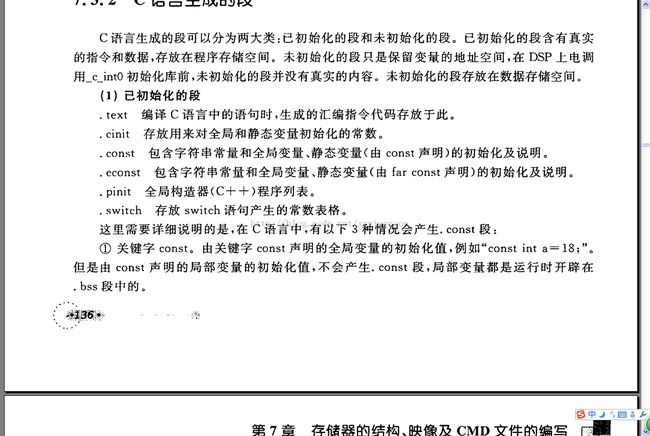

上面这张图为编译工程文件时的链接过程,可以解决我们一部分的疑惑。也解释了我第一段中text过大的原因,在工程中有些文件你虽然没有调用,但是他是占text的空间的,这也是我最初删除了一些不用的c文件就编译成功的原因。

最后:排爆机器人基于dsp+fpga中有些特色还没写出来,包括串口状态机(这部分比较好,继承师兄的),还有就是dsp读写fpga这部分吧(基于xintf的),然后还用到了pwm模块,哦,还有一个就是烧写到flash里面,拷贝到ram里面运行,不过这东西是借鉴的别人的,慢慢记录下来吧。