quartus ii 和 modelsim 编译仿真的流程

暑假要弄fpga,上一次用好像是去年的暑假,感觉流程什么的忘了。所以这次一定要把流程mark一下。

首先在quartus目录下建个文件夹,然后打开quartus在目录下建一个工程,向导记住选好fpga型号,后面什么的先直接过。

然后新建文件,选择verilog或vhdl语言,编写完毕先add to project,保存的时候记住文件名要跟模块名一样(好像不用和项目名称一样)。

然后对源文件进行编译。

一般最好将源文件右击,set as top-level entity,不然会报错:

top-level entity is not defined。

接下来要编写测试文件testbench,也是新建一个文件,保存,编译。

然后要进行仿真的设置,最好一次性设置好,以后就不用在管它了。

1、tool->options->EDA tool options,把安装的Modelsim-Altera路径填写。

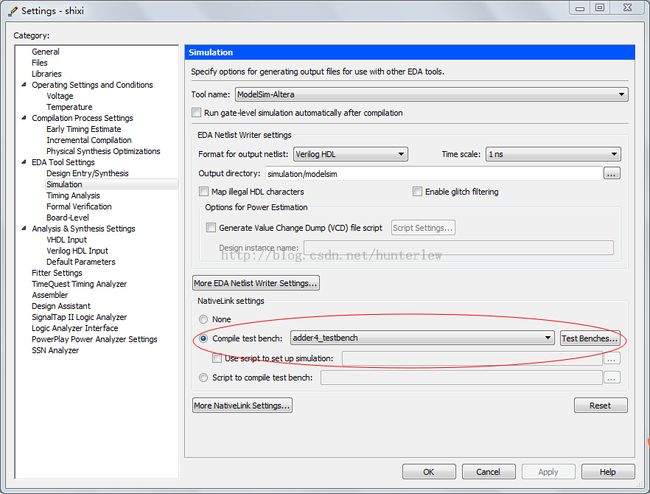

2、assignments->setting->simulation,一样把路径填写。

3、下方的NativeLink settings对Compile test bench选上,然后点开右方的Testbench按钮。

4、选择New,出现新的对话框,填上Testbench名称,下面有个file name选择刚才testbench保存的地方,并记得add,然后连按3个ok设置完成。

5、进行最后一次编译并run,就能打开modelsim进行仿真了。RTL是功能仿真,Gate是时序仿真不过没用过。

至此,仿真流程完成。